Intel Flashes World’s First UCIe-Connected Test Chip Package

Standardization comes to fore.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

- ▶ Meteor Lake: Core Ultra Architecture Detailed, Due Dec. 14

- ▶ Meteor Lake GPU: Chip doubles Integrated Graphics Performance Per Watt

- ▶ 5th-Gen Xeon: Intel Shows 288-Core Processor, Arrives Dec. 14

- ▶ Arrow Lake Wafer: Showcase for 20A Process Node; Chips in 2024

- ▶ Pike Creek: World’s First UCIe-Connected Chiplet-Based CPU

- ▶ Lunar Lake-Based PC: Intel also unveils Panther Lake for 2025

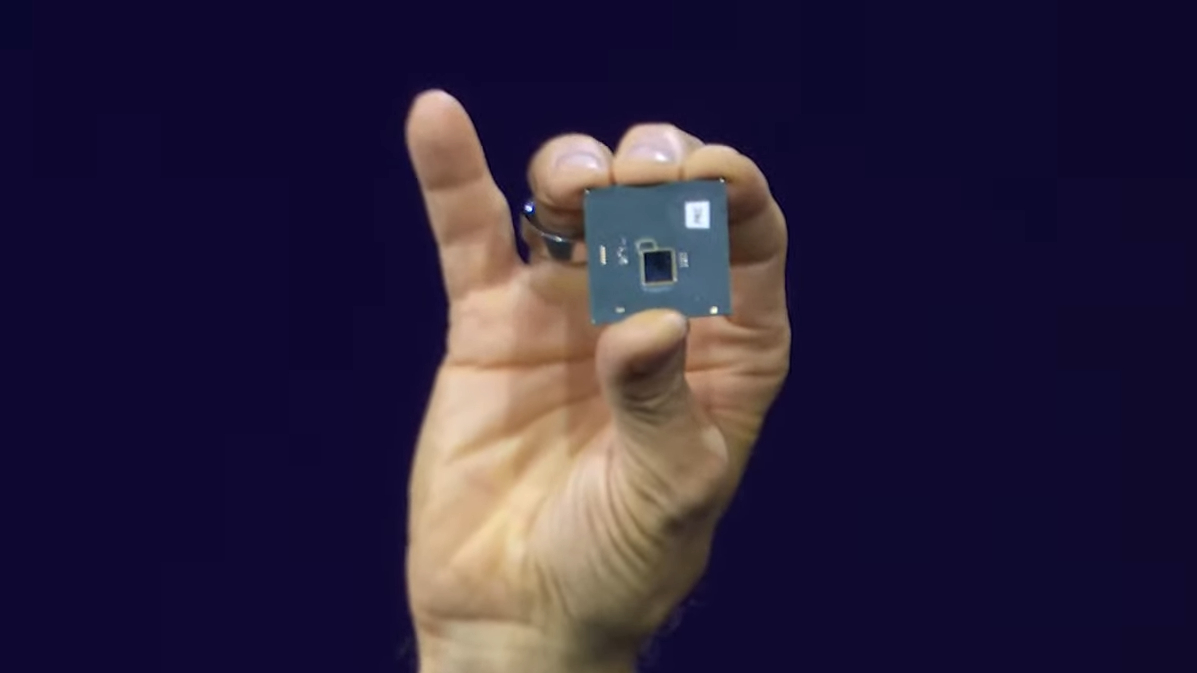

Intel CEO Pat Gelsinger displayed Pike Creek, the world’s first UCIe-connected chiplet-based test chip, here at Innovation 2023, marking the first public display of working UCIe-enabled silicon. The test chip features an Intel UCIe IP chiplet fabbed on its own Intel 3 process node paired with a Synopsys UCIe IP chip fabbed on the leading-edge TSMC N3E node. The two chiplets communicate via Intel’s EMIB interface.

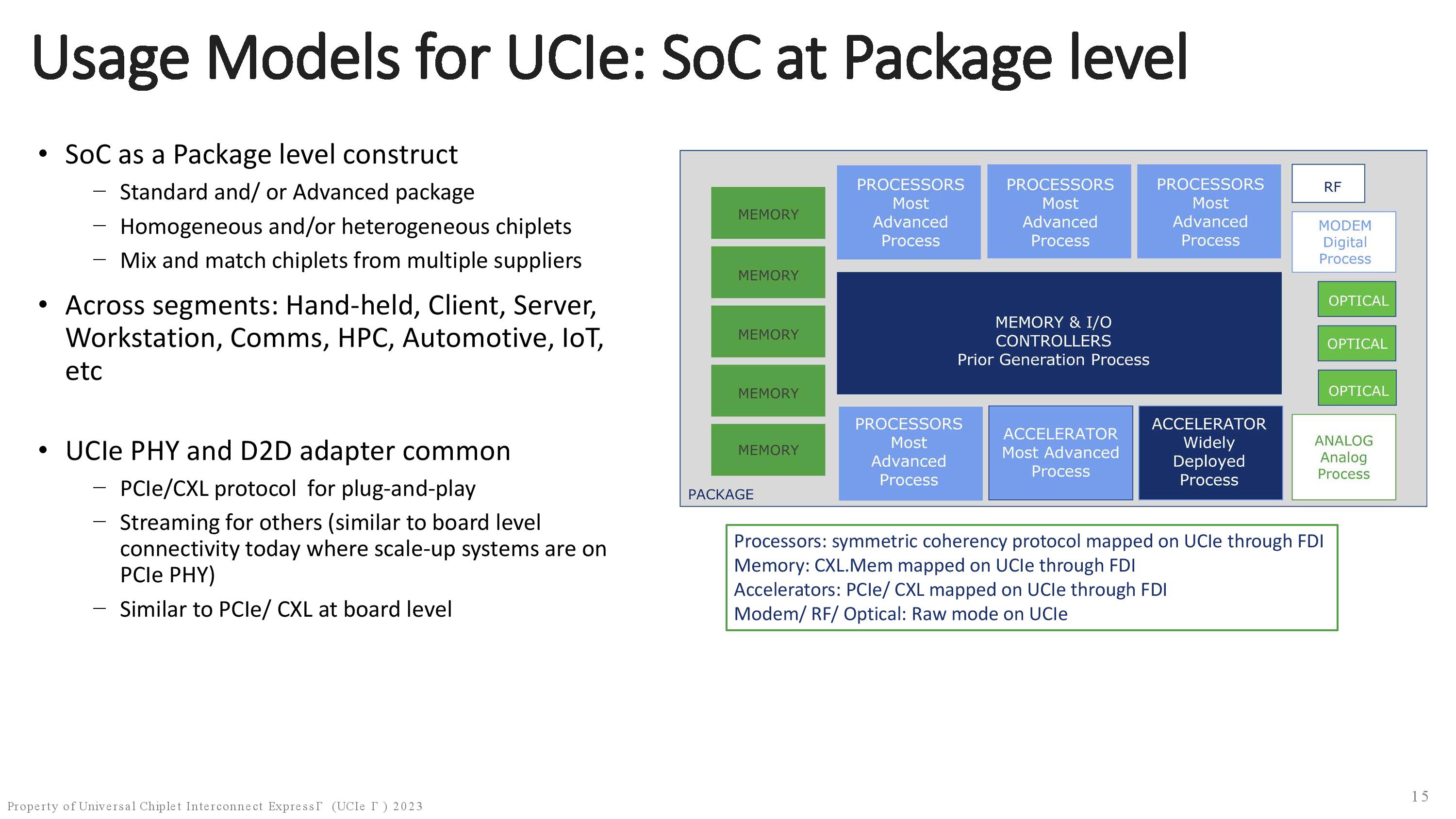

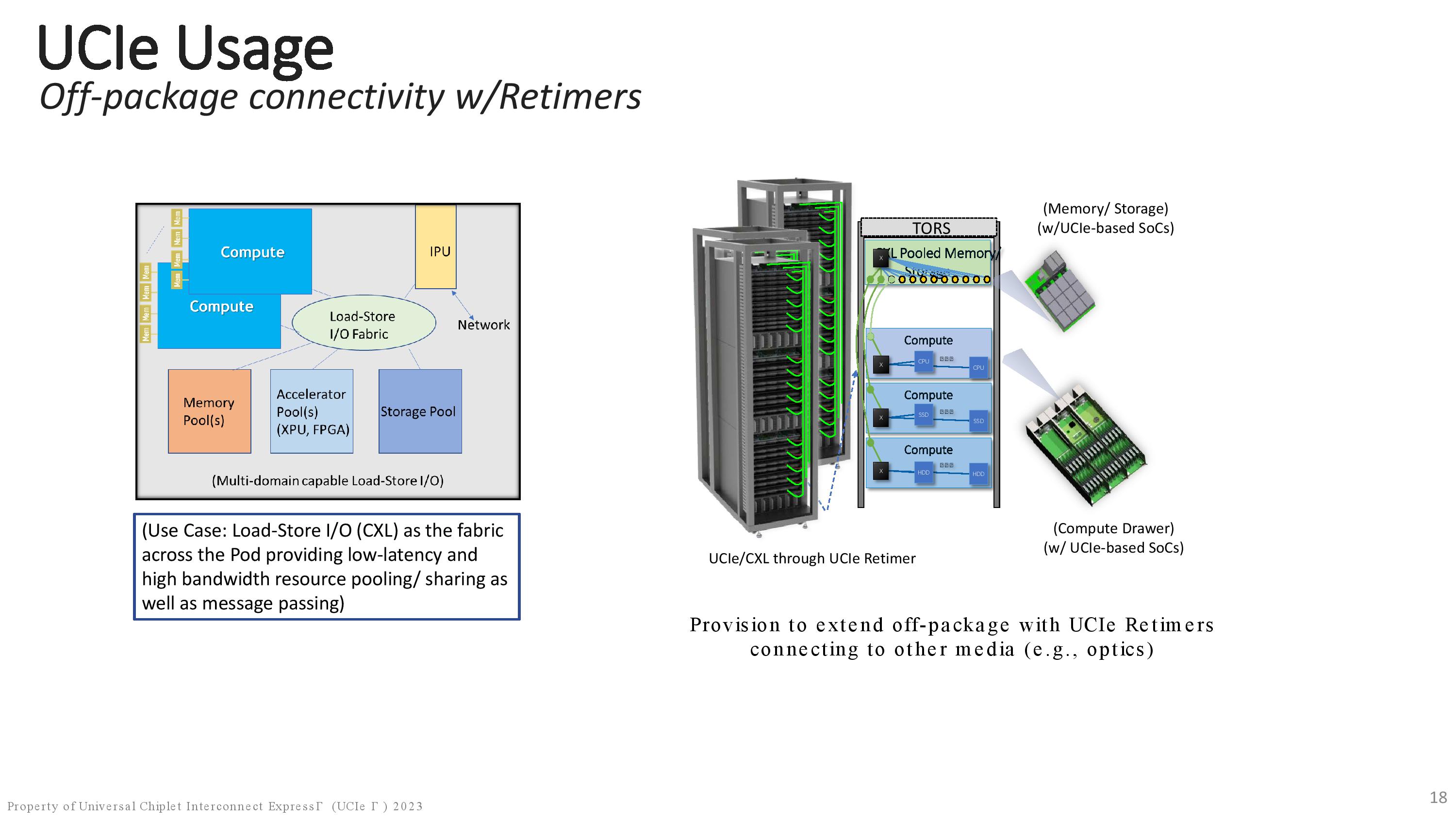

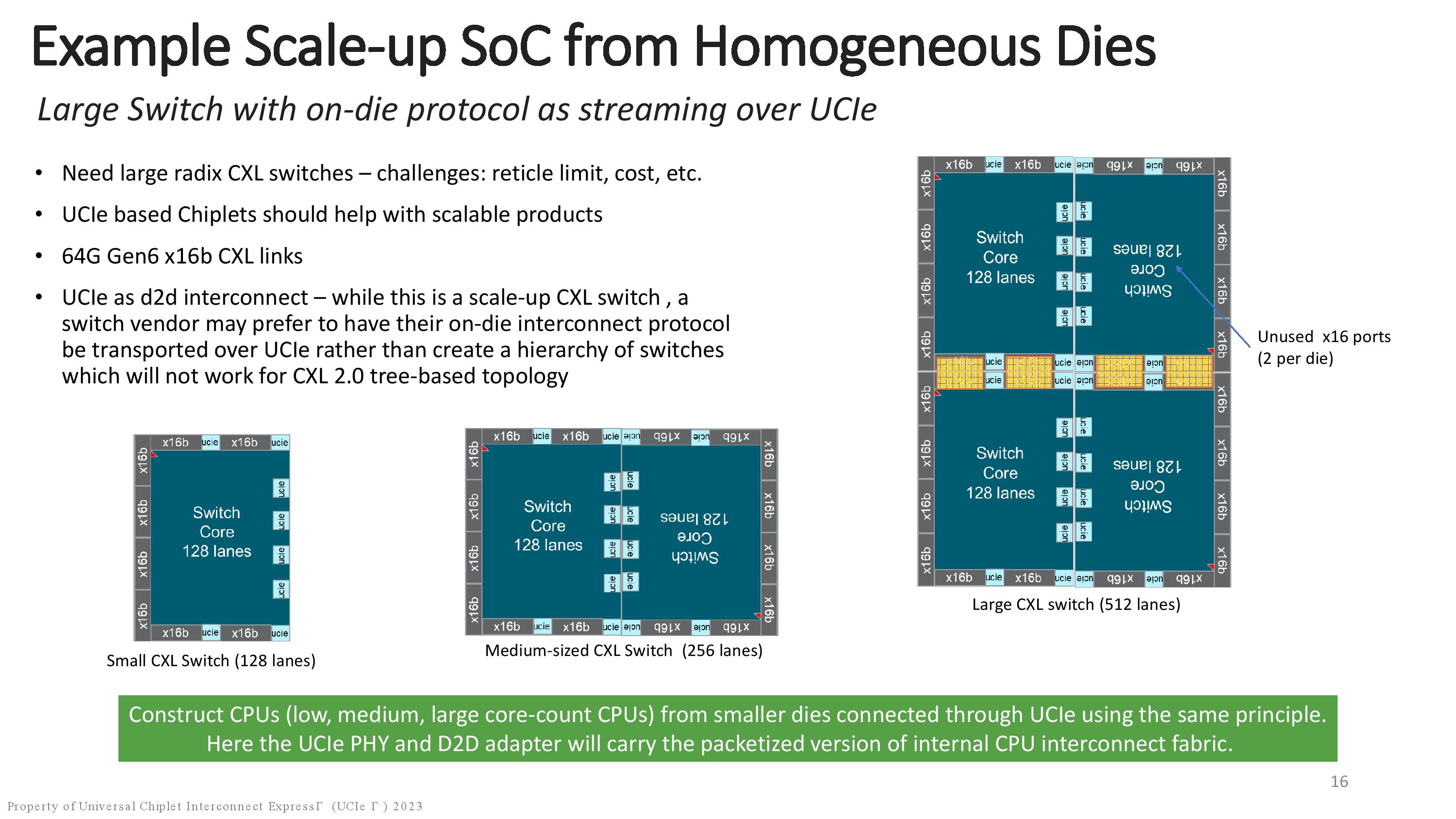

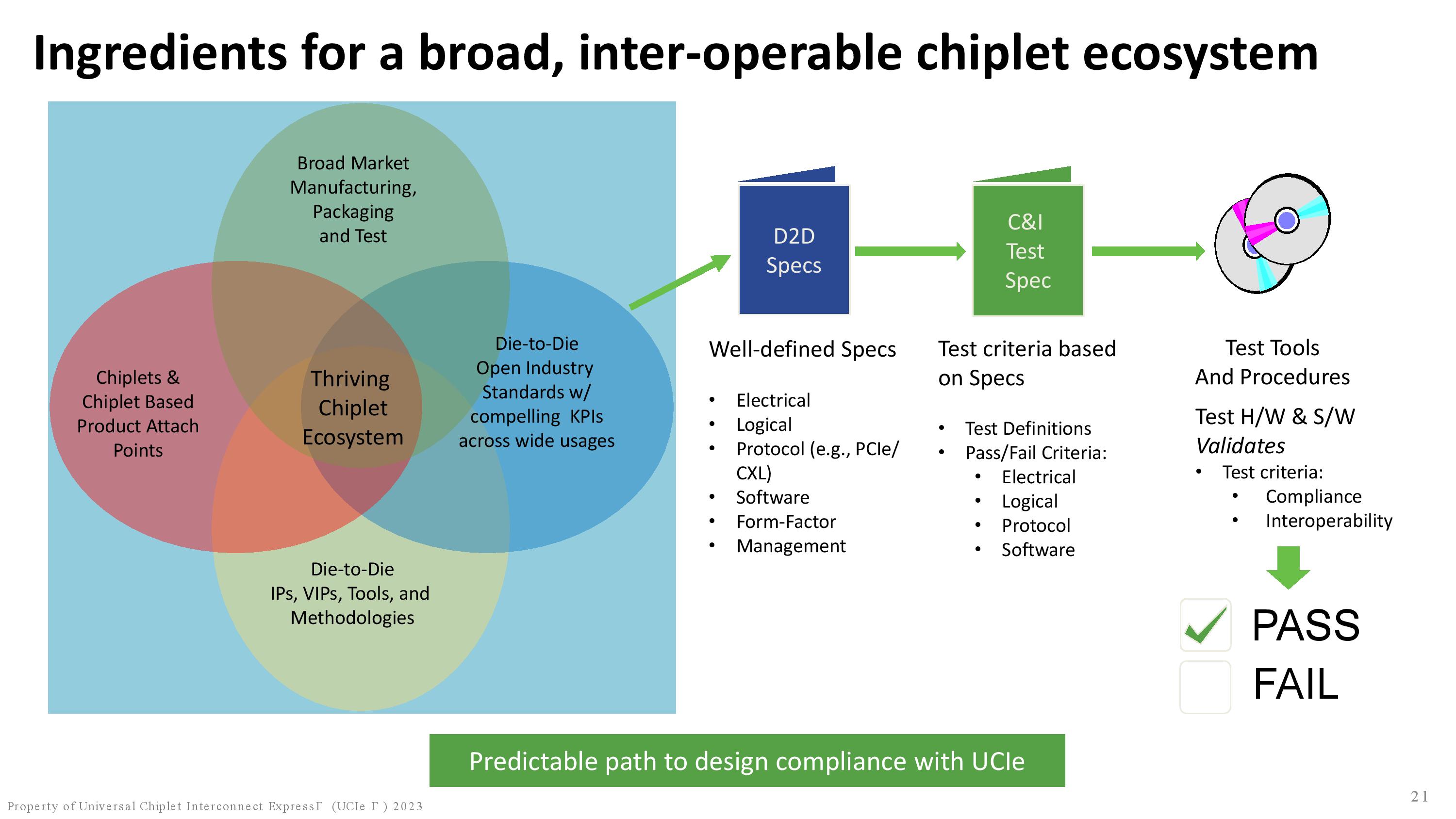

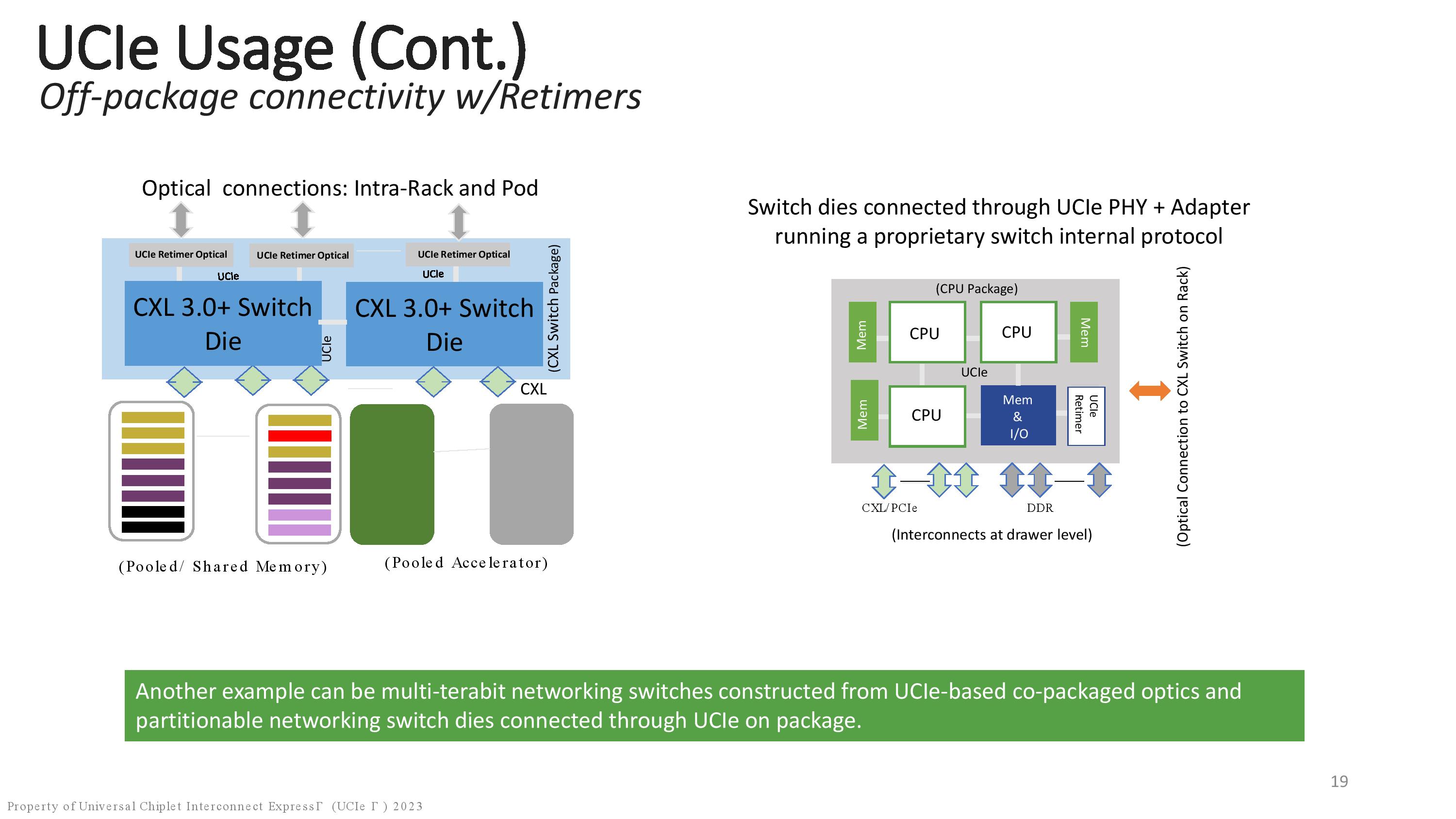

The Universal Chiplet Interconnect Express (UCIe) interface is supported by a wide range of industry stalwarts, like Intel, AMD, Arm, Nvidia, TSMC, and Samsung, among 120 others. This interconnect is designed to standardize the die-to-die interconnects between chiplets with an open-source design, thus reducing costs and fostering a broader ecosystem of validated chiplets.

Today’s multi-chiplet packages use proprietary interfaces and protocols to communicate with one another, making broad adoption of third-party chiplets a daunting task. The goal of UCIe is to create an ecosystem with a standardized interface so one day chipmakers will be able to simply select chiplets from other designers and snap them into their new designs with a minimum of design and validation work.

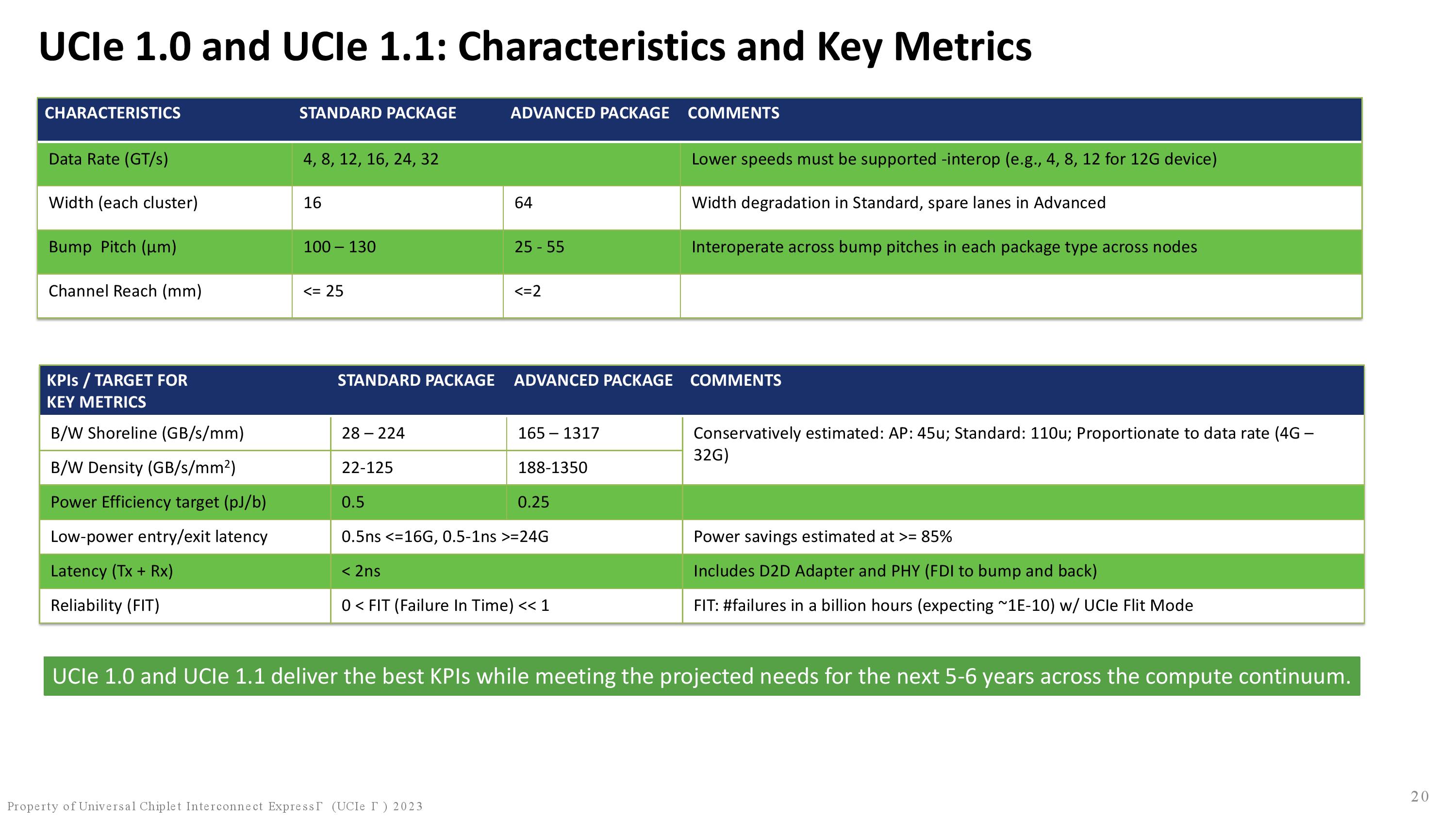

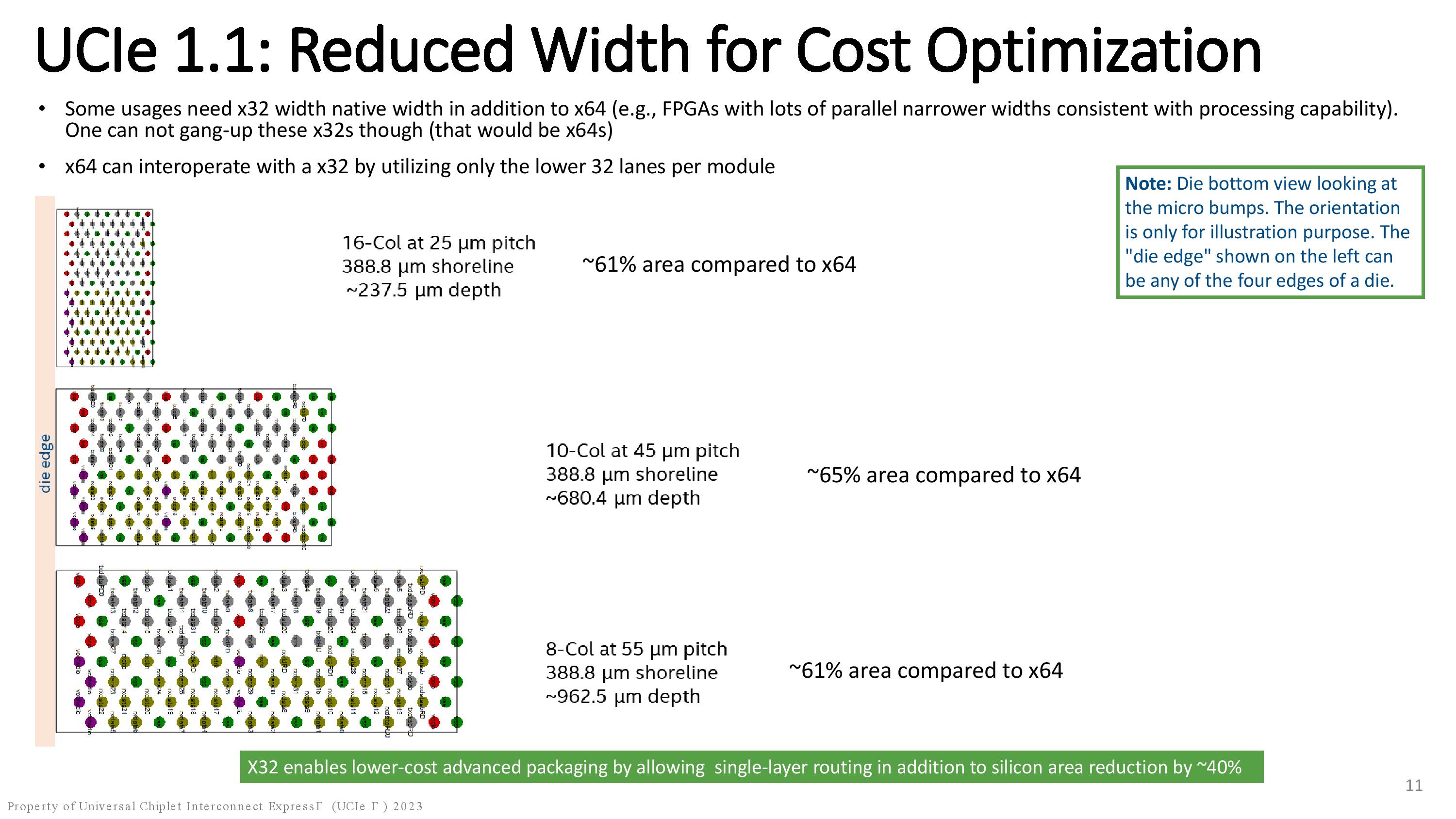

The UCIe consortium was created last year, deep-dive details here, and it has already enjoyed broad support for the chipmaking industry. The spec debuted at version 1.0, but has now moved on to the 1.1 spec outlined in the album above. The consortium has outlined very aggressive performance and area targets, carving the target markets into two broad ranges, with standard 2D packaging techniques and more advanced 2.5D techniques (EMIB, CoWoS, etc.). Naturally, the advanced packaging options provide higher bandwidth and density.

Intel’s chiplet-based processors, like Sapphire Rapids and the newly announced Meteor Lake, currently use a proprietary interface and protocol for communication between the chiplets, but Intel has announced that it will use the UCIe interface after its next-gen Arrow Lake consumer processors. AMD and Nvidia are also working on their own initiatives, and you can read about those efforts in those links. Neither has shown working silicon.

We’re here at the show and will update with additional details about the test chip as they emerge.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

bit_user ReplyIntel’s chiplet-based processors, like Sapphire Rapids and the newly announced Meteor Lake, currently use a proprietary interface and protocol for communication between the chiplets, but Intel has announced that it will use the UCIe interface after its next-gen Arrow Lake consumer processors.

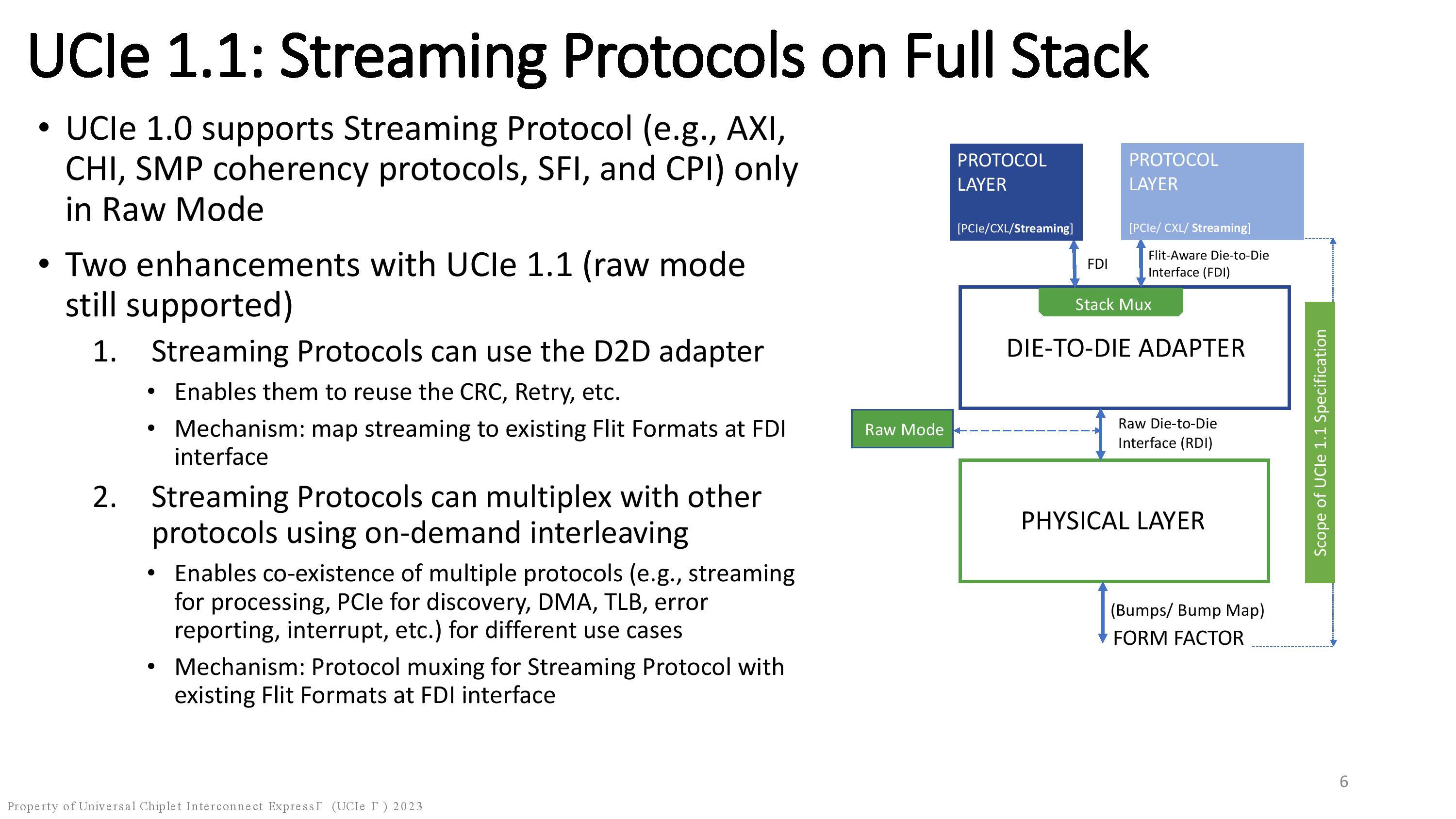

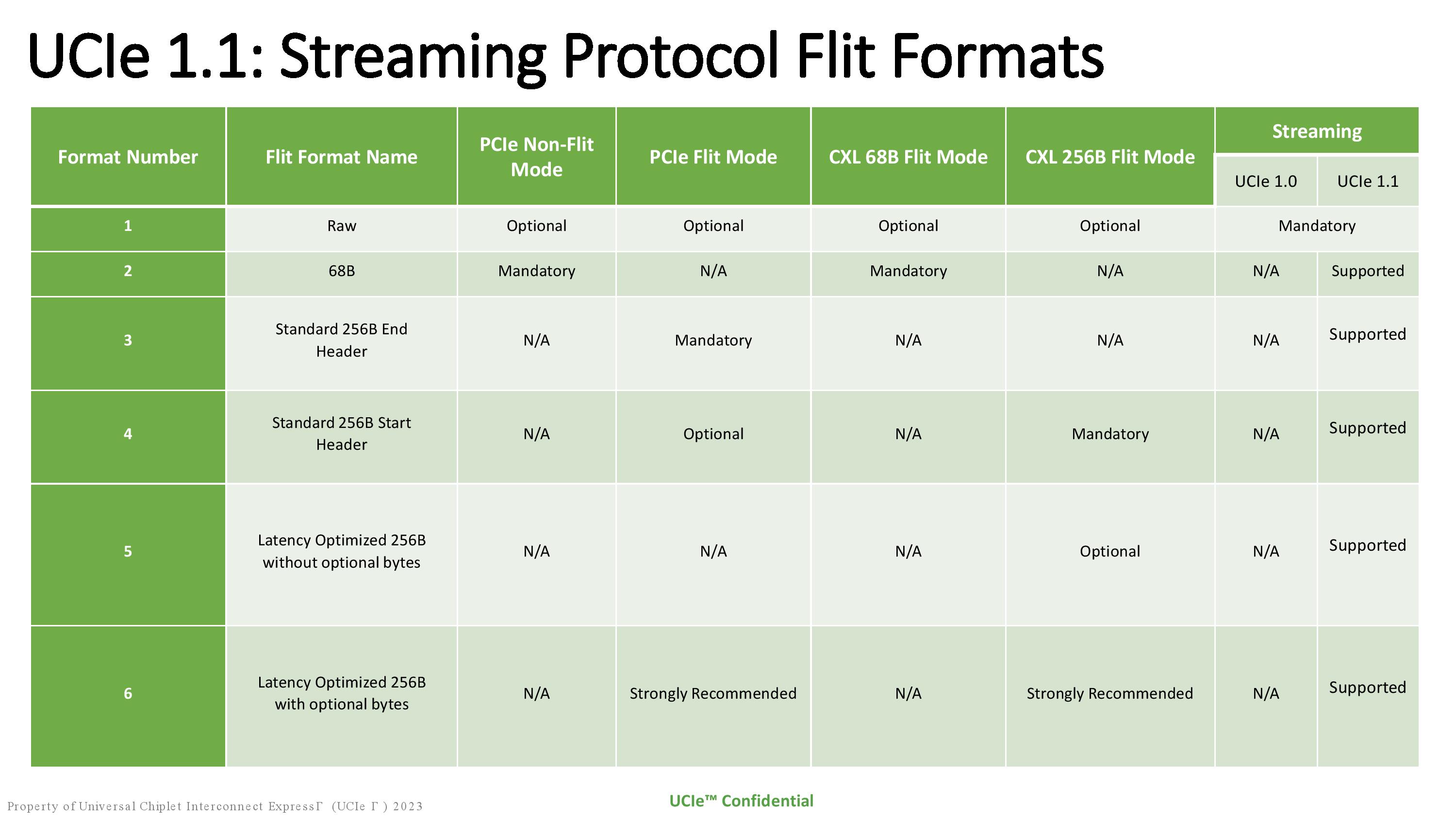

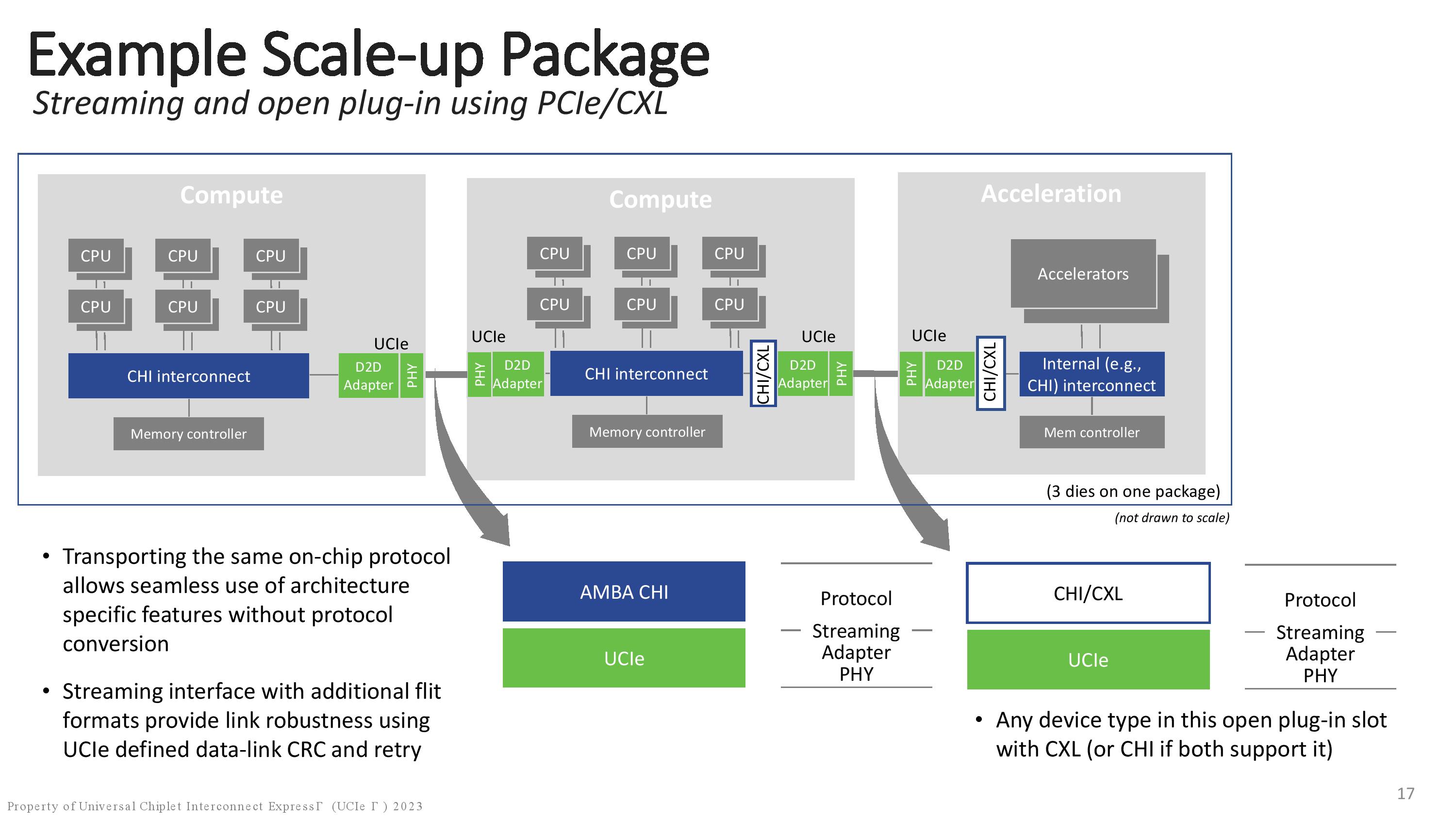

Actually, UCIe does allow for proprietary protocols. This was certainly necessary to gain widespread adoption by major players. That way, Nvidia can adopt it without foregoing NVLink and AMD needn't abandon Infinity Fabric - it's merely the physical and electrical aspects they'd benefit from. Even then, having standards should help with tooling, IP libraries, and ultimately time-to-market.

There's a good writeup of it, here:

https://www.anandtech.com/show/17288/universal-chiplet-interconnect-express-ucie-announced-setting-standards-for-the-chiplet-ecosystem

"at the protocol layer, chiplet makers have a few different options. The official standardized protocols for UCIe are PCI-Express and its cache-coherent cousin, Compute Express Link, ...

... the promoters have made it clear that UCIe isn’t locked to just PCIe/CXL. Future versions of the standard may add other protocols if something comes along and the owner is willing to donate it to the standard.

Finally, chipmakers are also free to use their own custom/bespoke protocols as well; they are not restricted to using just PCIe/CXL. UCIe supports a raw/streaming protocol option that allows any other protocol to be used. Both chiplets would need to support this custom protocol to make a connection, of course, but even in this case, this would allow a chipmaker to leverage the physical aspects of the UCIe standard to simplify their own design/production."

-

Paul Alcorn Reply

The article does not state that different protocols cannot be used. As I wrote in our initial coverage of the UXIe launch, "While the specification begins with PCIe and CXL as the current protocols, it will expand to include other protocols in the future." -- no need to quote AT at me.bit_user said:Actually, UCIe does allow for proprietary protocols. This was certainly necessary to gain widespread adoption by major players. That way, Nvidia can adopt it without foregoing NVLink and AMD needn't abandon Infinity Fabric - it's merely the physical and electrical aspects they'd benefit from. Even then, having standards should help with tooling, IP libraries, and ultimately time-to-market.

There's a good writeup of it, here:

https://www.anandtech.com/show/17288/universal-chiplet-interconnect-express-ucie-announced-setting-standards-for-the-chiplet-ecosystem"at the protocol layer, chiplet makers have a few different options. The official standardized protocols for UCIe are PCI-Express and its cache-coherent cousin, Compute Express Link, ...... the promoters have made it clear that UCIe isn’t locked to just PCIe/CXL. Future versions of the standard may add other protocols if something comes along and the owner is willing to donate it to the standard.Finally, chipmakers are also free to use their own custom/bespoke protocols as well; they are not restricted to using just PCIe/CXL. UCIe supports a raw/streaming protocol option that allows any other protocol to be used. Both chiplets would need to support this custom protocol to make a connection, of course, but even in this case, this would allow a chipmaker to leverage the physical aspects of the UCIe standard to simplify their own design/production." -

bit_user Reply

The part I quoted from your article (at the top of my post) really made it sound like Arrow Lake will switch to using one of the official UCIe protocols. My point was that even in its current incarnation, UCIe does not mandate the use of PCIe or CXL for chiplet communication.PaulAlcorn said:The article does not state that different protocols cannot be used. As I wrote in our initial coverage of the UXIe launch, "While the specification begins with PCIe and CXL as the current protocols, it will expand to include other protocols in the future."

It's not only future versions of UCIe that potentially allow for other protocols. I took care to underline that part, so it'd be hard to miss.

The diagram was included to show that the protocol is only a part of what UCIe defines. Even if you give up the protocol layer, there's still a lot else. You might be aware of that, but others might not be attuned to it.

It wasn't really directed at you, but rather anyone else in the comments. I don't presume authors read the comments (many/most don't) and I didn't even @-you, this time.PaulAlcorn said:no need to quote AT at me.

Again, thanks for your coverage. Try not to mind us nit-pickers, too much!

: )