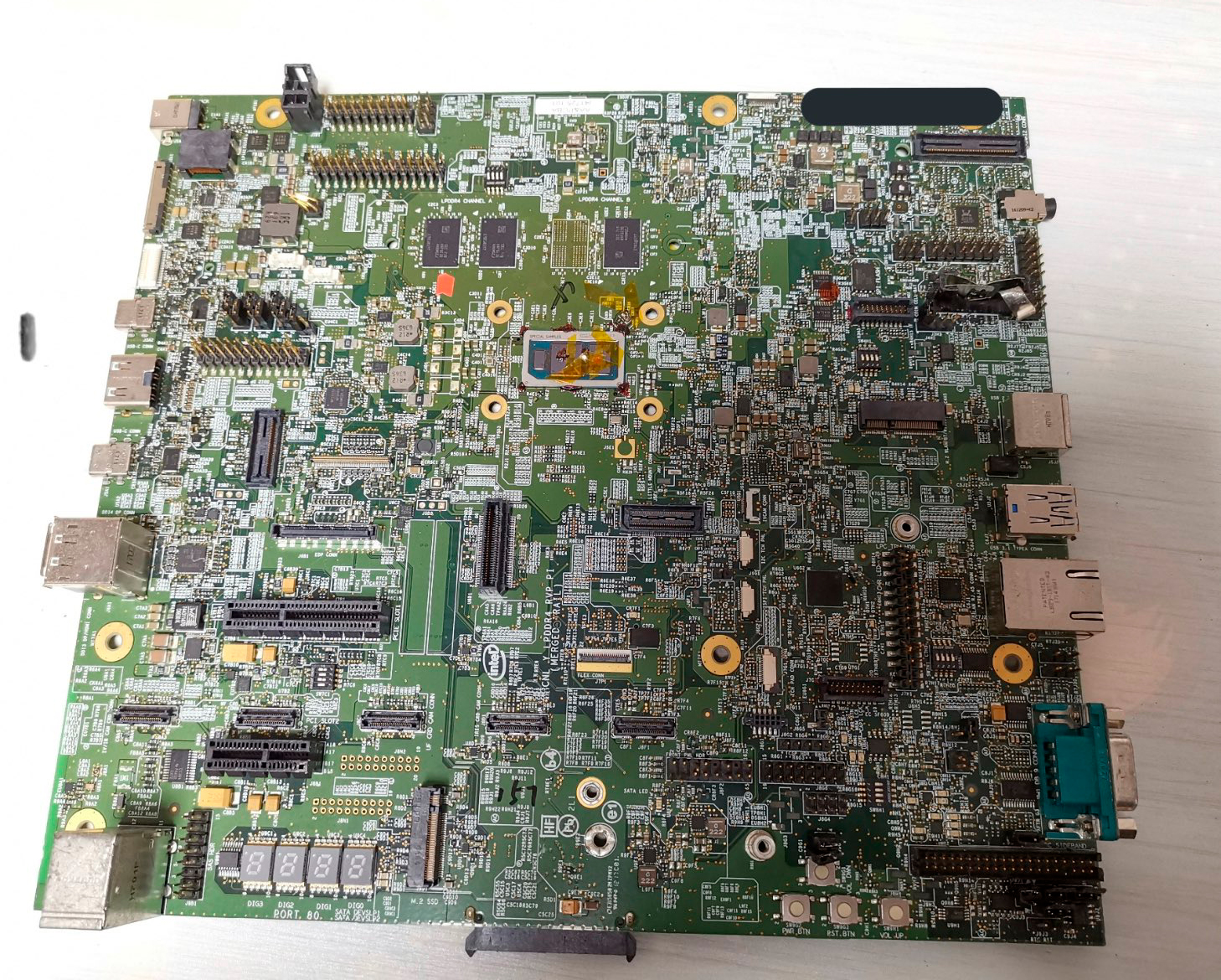

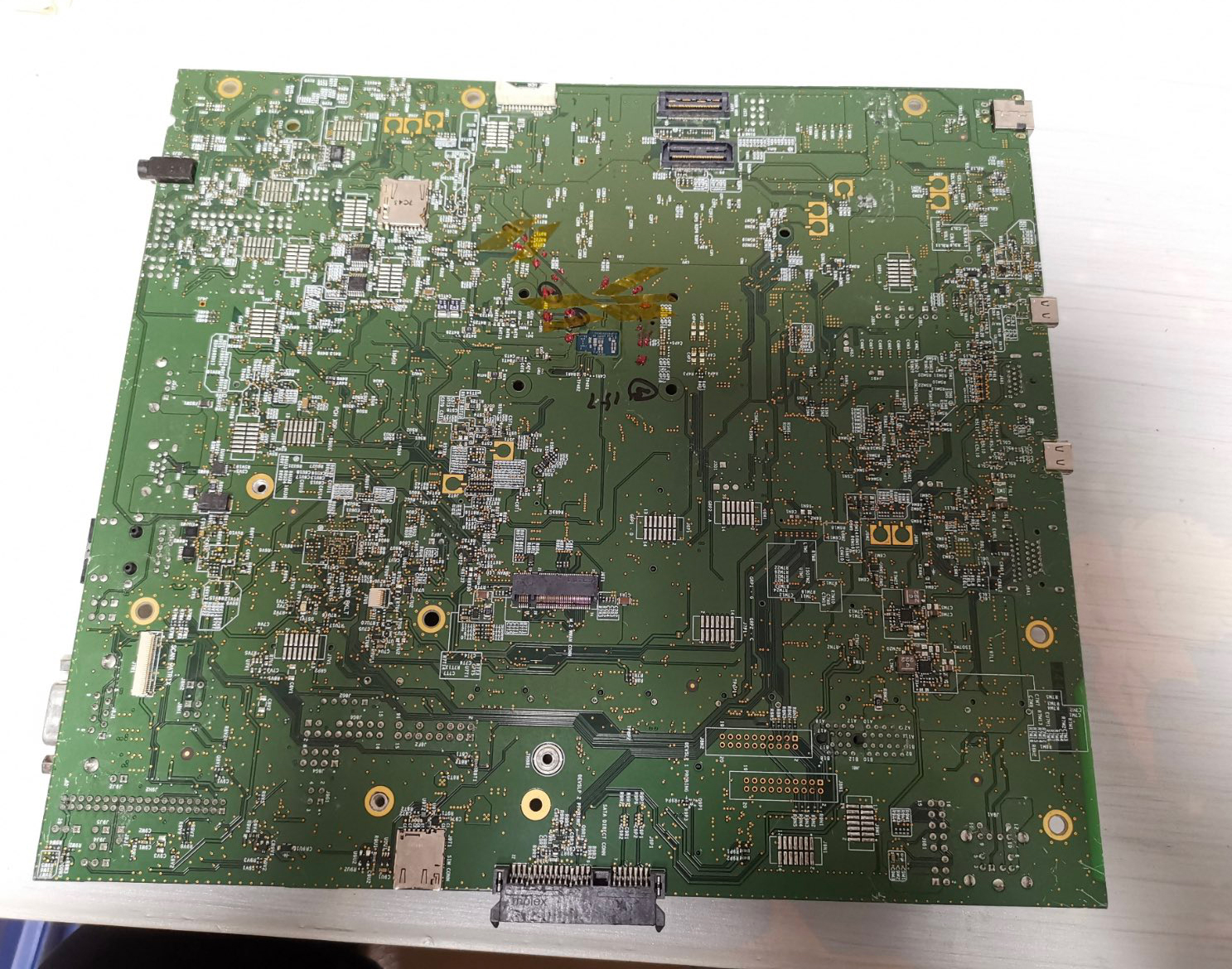

Rare Intel Cannon Lake CPU Emerges With Three Chiplets

A blast from the past

A mysterious Intel Cannon Lake prototype processor has surfaced in the wild, rocking up to three chiplets. Hardware leaker YuuKi_AnS shared the images on Twitter, and CPU expert SkyJuice60 detailed the third die's function.

The third chiplet reportedly serves as the CPU's Integrated Voltage Regulator (IVR), a feature that originated with Intel's Haswell (and Devil's Canyon) 4th Generation CPU architecture several years ago. But Cannon's implementation is known as a Multi-Chip Integrated Voltage Regulator (McIVR) due to the additional die.

IVR first debuted in Intel's 4th Generation Haswell architecture in 2013. IVR changed the way the motherboard and processor handled the power delivery. It transferred the CPU voltage regulation directly into the CPU die from the motherboard.

Intel said this greatly simplified the Haswell platform's power delivery design, with IVR being able to replace five voltage regulators on the mainboard down to just one inside the CPU. Another benefit to this design includes finer-grain voltage control for the processor. But in the end, Intel canceled IVR on all mainstream desktop architectures following 5th Generation Broadwell chips for unknown reasons. However, we believe its removal was related to thermal issues and die size constraints. Nonetheless, IVR reappeared in other architectures following Haswell, including a few mobile architectures and Intel's Skylake-X HEDT architecture.

It would seem that Intel also had plans to integrate IVR into its Cannon Lake mobile processors, with this prototype being proof of the idea. But, what makes IVR unique in Cannon Lake is its multi-chip implementation.

The approach makes a lot of sense from Intel's perspective and could significantly improve the chip's voltage headroom and temperature limitations. Previous IVR designs, particularly on Haswell, made the chip extra hot since the CPU cooler now had to deal with heat from the voltage regulator and the CPU cores, integrated graphics, and the CPU cache combined.

It wasn't a big deal for regular users, but it did become problematic with many overlockers having temperature limitations instead of voltage limitations on mid-range air coolers.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

On a mobile chip, the situation is very similar to overlockers. CPU coolers on notebooks are much smaller than desktop coolers, and as a result, you want as much thermal efficiency as possible from the CPU. Moving IVR to a separate die would do just that and disperse the heat to a different area, allowing the CPU cooler to handle heat transference more effectively.

It's a shame this triple chiplet design never came to the market. Cannon Lake was one of Intel's worst, if not the worst, architecture ever released, featuring a horrible implementation of Intel's first 10nm process (now rebranded to Intel 7), less than two years of support, and only one CPU supporting the architecture.

Aaron Klotz is a contributing writer for Tom’s Hardware, covering news related to computer hardware such as CPUs, and graphics cards.