Ryzen 9 7950X3D surfaces with 192MB L3 cache, 64MB more than retail CPU — may be an ES CPU or software detection error

An engineering sample that looks like a Windows bug, or vice versa?

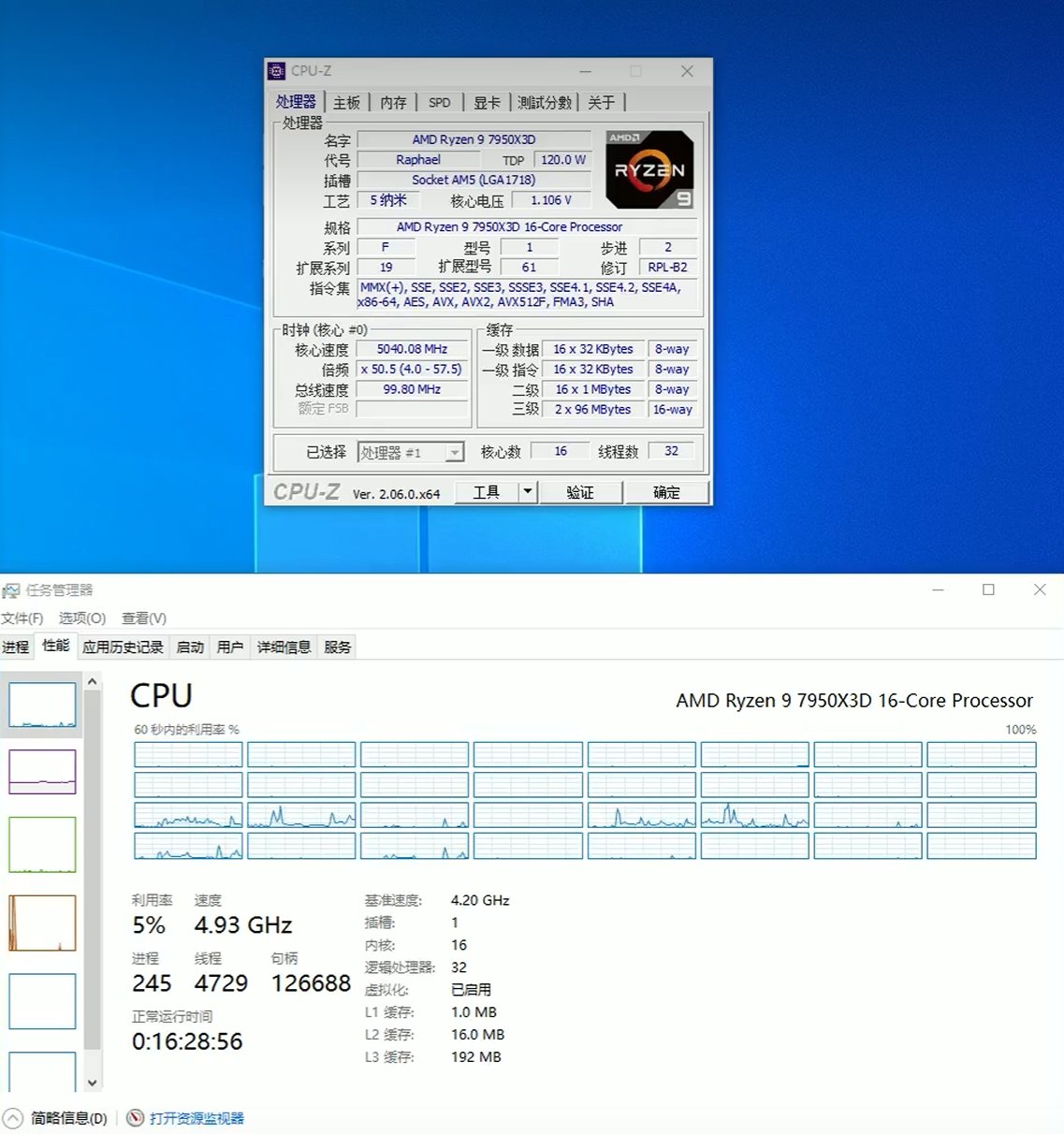

Maybe it was a Windows bug or a supply chain mistake, but an AMD Ryzen 9 7950X3D, one of the best CPUs, surfaced with 64MB more L3 cache than usual. The Ryzen 9 7950X3D 16-core processor typically ships with 128MB of L3 cache, but this one reported 192MB. X user HXL made the rare find and posted screenshots of the Bilibili video with the reported specifications.

While we expected to see a CPU with a 128MB L3 cache, we observed different specs. According to both Windows Task Manager and CPU-Z, the reported capacity of the L3 cache was 192MB. All of the other specifications look normal. AMD designed the Ryzen 9 7950X3D for gamers who wanted to enjoy CPU-limited games while still enjoying the productivity benefits of a 16-core CPU. It utilizes AMD’s second-gen 3D V-Cache and, according to our testing, surpasses Intel’s fastest chip.

Some responses to HXL’s screenshots suggested a bug in Windows. One user believes that it’s an old CPUID bug that erroneously reports 192MB on the L3 cache. Others suggested that the builder lucked out and got an engineering sample, such as a prototype with a double 3D V-Cache die. Unfortunately, the user didn’t perform any benchmarks to verify the integrity of the amount of reported L3 cache.

Article continues belowWhile a software bug is possible, we can’t discard the fact that the Ryzen 9 7950X3D could be an early engineering sample that AMD was playing with. The technology is there, where the chiplets add 64MB of 7nm SRAM cache stacked on top of each core complex die (CCD). It can produce up to 192MB of L3 cache per Ryzen processor.

Before AMD released the Ryzen 9 7950X3D in 2023, Gamers Nexus visited the company’s campus in Austin, Texas. During that visit, the team discussed the different configurations tested with AMD. Among these were samples with multiple 3D stacked cache dies, which could lead to the 192MB L3 cache configuration being considered. The chipmaker demonstrated an unreleased Ryzen 9 5950X3D with a 192MB L3 cache to Gamers Nexus, so we know at least one exists.

Ultimately, AMD may have opted not to manufacture the Ryzen 9 7950X3D in that configuration to maintain a uniform L3 cache pool. The engineers found that having multiple cache pools caused increased latency in most games, decreasing performance rather than increasing it. If an engineering sample is created, there’s always a chance of it slipping through the cracks. These prototypes are supposed to be recycled or destroyed, of course, but mistakes happen. It seems most likely this extremely rare CPU with an extra L3 cache is one of those engineering samples.

Alternatively, the Ryzen 9 7950X3D with 192MB L3 cache may be an engineering sample of AMD’s upcoming EPYC 4004 series, which are server-grade Zen 4 chips with 3D V-Cache for the mainstream AM5 socket.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Jeff Butts has been covering tech news for more than a decade, and his IT experience predates the internet. Yes, he remembers when 9600 baud was “fast.” He especially enjoys covering DIY and Maker topics, along with anything on the bleeding edge of technology.

-

kiniku Even a regular 7950X3D is a very impressive, sophisticated processor. If you want "it all", gaming, professional workloads, it delivers like no others. I am looking forward to seeing the 8000 series and its comparative performance. Maybe an 8800X3D?Reply -

Vanderlindemedia The amount of cache may simply line-up. Remember whole X3D variants are defected, not passing Quality coming off of Epyc line to begin with.Reply -

TechAndGame My 7950X3D also reports 192MB L3 cache, both in windows and in HWinfoReply

windows: K9BHcp4View: https://i.imgur.com/K9BHcp4.png

hwinfo: xyHDER8View: https://i.imgur.com/xyHDER8.png

aida64 cpuid: atQOHTrView: https://i.imgur.com/atQOHTr.png -

usertests Reply

Expected to be called 9000 series.kiniku said:Even a regular 7950X3D is a very impressive, sophisticated processor. If you want "it all", gaming, professional workloads, it delivers like no others. I am looking forward to seeing the 8000 series and its comparative performance. Maybe an 8800X3D?

If AMD wants to impress, they release a 9960X3D: 8 Zen 5 cores with 3D V-Cache, and 16 Zen 5c cores. None of the scheduling issues seen with 7950X3D/7900X3D, they would still only have to add 1 cache chiplet, and it would lead in multi-threading. -

Thunder64 Replyusertests said:Expected to be called 9000 series.

If AMD wants to impress, they release a 9960X3D: 8 Zen 5 cores with 3D V-Cache, and 16 Zen 5c cores. None of the scheduling issues seen with 7950X3D/7900X3D, they would still only have to add 1 cache chiplet, and it would lead in multi-threading.

But presumably at a significant clock speed deficit as neither 3D cache nor C cores have shown they can clock as high as regular cores yet. That could be a problem. -

slash3 This seems to be a side effect of Windows' VBS (Core Isolation) feature, where enabling it will cause the system to mis-report L3 cache size as 2 x 96MB.Reply

I tested it on my own 7950X3D and was able to reproduce the issue, as shown here.

a/54d8cdFView: https://imgur.com/a/54d8cdF

Enabling VBS shows 192MB in Task Manager, or 2 x 96MB in CPU-Z.

Disabling VBS (and rebooting) shows 128MB in Task Manager, and 96 MB + 32 MB in CPU-Z. -

vibraniumdroid Reply

That's quite interesting if true. Do you have a source for that? Couldn't find anything online.Vanderlindemedia said:The amount of cache may simply line-up. Remember whole X3D variants are defected, not passing Quality coming off of Epyc line to begin with. -

TerryLaze Reply

How do you figure that it wouldn't have any scheduling issues?!usertests said:Expected to be called 9000 series.

If AMD wants to impress, they release a 9960X3D: 8 Zen 5 cores with 3D V-Cache, and 16 Zen 5c cores. None of the scheduling issues seen with 7950X3D/7900X3D, they would still only have to add 1 cache chiplet, and it would lead in multi-threading.

Software doesn't understand, on its own, that the c cores are any different from any other cores, also I very much doubt they can fit 16c cores into the space of 8 normal cores, that would need a space benefit of at least 50% and the rumors are for about 35% ,so they would have to add one ccx more or change the size of it changing all of the tooling, and that's very doubtful as well. -

Amdlova Reply

Remember the all in one motherboard from amd? 4700s? That is a fail chip, bit they throw on the market to not loss a single penny...vibraniumdroid said:That's quite interesting if true. Do you have a source for that? Couldn't find anything online.

All chiplets are epyc cpus on mind. If they don't have the quality they throw to another class -

usertests Reply

Clock speed deficit, sure. Significant? Nah. The 3D cache cores would be the gaming cores, but still have respectable clocks despite losing a few hundred MHz turbo, and then the 16 C cores would be faster for multithreading than another 8 cores clocked higher.Thunder64 said:But presumably at a significant clock speed deficit as neither 3D cache nor C cores have shown they can clock as high as regular cores yet. That could be a problem.

The 7950X3D problem is that half the cores have tripled L3 cache, but the other half clock higher. The decision on whether or not it's beneficial to choose the extra cache or clocks varies by game or program. It's not obvious to a scheduler.TerryLaze said:How do you figure that it wouldn't have any scheduling issues?!

Software doesn't understand, on its own, that the c cores are any different from any other cores, also I very much doubt they can fit 16c cores into the space of 8 normal cores, that would need a space benefit of at least 50% and the rumors are for about 35% ,so they would have to add one ccx more or change the size of it changing all of the tooling, and that's very doubtful as well.

The hypothetical 8X3D+16 chip would have more cache and higher clocks on the X3D side. So when it uses the highest clocking cores, they also end up having the extra cache. No issues.

The Zen 4c core shrinks by 35.4% compared to a Zen 4 core. But the L3 cache also shrinks despite having the same 32 MB on the CCD, presumably from using a different cell library. I think this fact is often forgotten. I didn't remember it until I looked it up:

https://www.semianalysis.com/p/zen-4c-amds-response-to-hyperscale

The end result? An 8-core Zen 4 chiplet with 32 MB L3 cache (1 CCX) = 66.3mm^2. A 16-core Zen 4c chiplet with 32 MB L3 cache (2 CCXs) = 72.7mm^2. That's only 9.65% larger.