Samsung puts 3D DRAM on the roadmap, stacked DRAM to follow

At a sub-10nm node.

DRAM featuring 3D transistors has been discussed for years, but actual makers of memory have refrained from making any real announcements on the matter. However, Samsung decided to break the silence at Memcom last week and revealed some of its plans concerning 3D DRAM. As it turns out, the first 3D DRAM node is just a few years away.

The world's largest maker of memory plans to adopt DRAM with vertical channel transistors (VCT) starting from its 1st Generation sub-10nm process technology — if the slide that Samsung demonstrated at Memcom reflects the company's actual roadmap (and judging by the company's 10nm-class nodes, it does). The slide has been published by SemiEngineering and was republished by Fred Chen, a technology investigator.

Samsung reveals 3D DRAM in roadmap for 2025 and beyond. https://t.co/Wt4xgVKLSm pic.twitter.com/WWLmTPyqblMarch 31, 2024

A vertical channel transistor (VCT) can be a type of FinFET, in which the conducting channel is wrapped by a thin silicon 'fin,' forming the body of the device. A VCT could also be a gate-all-around (GAA) transistor, in which the gate material surrounds the conducting channel from all sides. Based on the image from the slide, we are dealing with a FinFET-based DRAM process technology.

That 1st Generation sub-10nm DRAM fabrication process is two generations away, as Samsung's latest DRAM production node is its 5th Generation 10nm-class (12nm) technology introduced in mid-2023. Based on the slide, Samsung preps two more 10nm-class production nodes, and the 1st Gen sub-10nm node is set to appear in the second half of the decade.

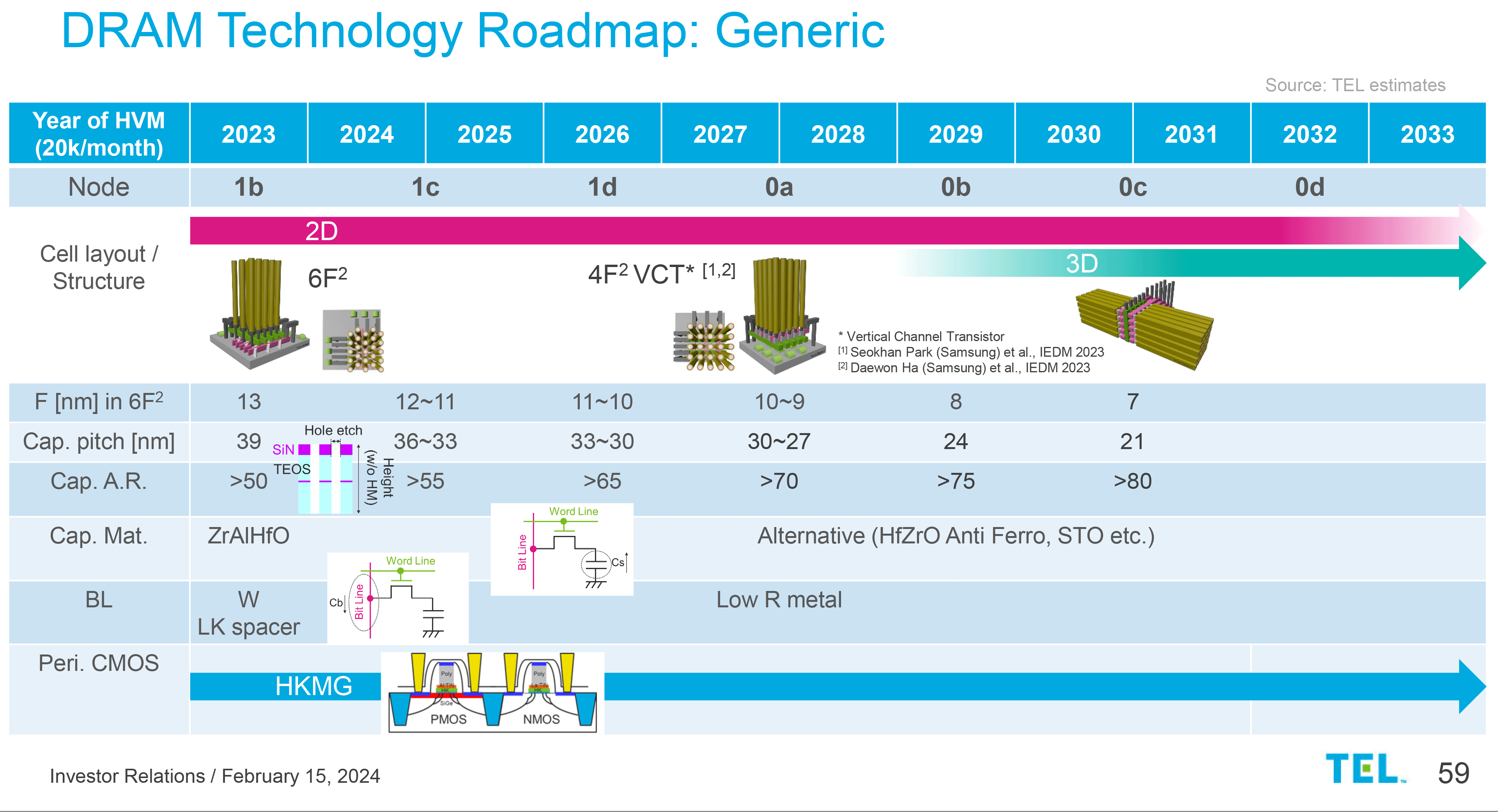

Normally, the adoption of 3D transistors for DRAM is associated with achieving a 4F^2 cell design, considered one of the most efficient memory cell layouts ever in terms of manufacturing costs. Tokyo Electron, a leading maker of wafer fab tools, expects DRAMs featuring VCTs and 4F^2 cell design to start emerging in 2027 – 2028. The company believes that to make VCT-based DRAMs; memory makers will have to adopt new materials for capacitors and bitlines.

Interestingly, Samsung plans to adopt a stacked DRAM process technology sometime in the early 2030s, enabling the company to tangibly increase the density of its memory devices in about ten years. At this point, we can only wonder what densities we'll be looking at in the next decade — though it's likely that we'll be dealing with next-generation DRAM technologies (e.g., DDR6).

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

usertests I hope someone gets there faster. For example, NEO Semiconductor:Reply

https://www.tomshardware.com/news/3d-x-dram-roadmap-1tb-die-density-by-2030 -

Notton What kind of technology are they using for sub-10nm?Reply

I distinctly remember there being a breakthrough with a new high-K material that allows 12nm capacitors, or something to that tune.

However, I don't think I've heard news of a breakthrough allowing sub-10nm capacitors. -

bit_user I find the title's use of the term "stacked DRAM" to be somewhat misleading. It's too easily confused with die-stacking, which already exists in the form of HBM and high-density DDR4 and DDR5 packages.Reply

Clearly, the article is talking about cell-stacking, akin to what NAND memory makers have been doing in their 3D NAND dies. -

gg83 From that one slide shared, it appears sub 10nm seems not easily obtainable with current tech. And the nm size refers to the capacitor size?Reply -

Max The Dragon Well, 3D dram, will make 128 GB+ consumer dimms possible?Reply

It will definitely lower the price of dram in future, as 3D technology made Nand so affordable and reliable.

Plus it can give more potential to make dimms more compact without performance penalty. -

Notton Reply

Yeah, DRAM is limited by the capacitor and its dielectric material.gg83 said:From that one slide shared, it appears sub 10nm seems not easily obtainable with current tech. And the nm size refers to the capacitor size?

The capacitor has to retain a charge to work, and won't hold a charge if shrunk too much.

Currently it's in the 14~12nm range.

If a better dielectric material can be made, then the capacitor can be shrunk.

AFAIK, Micron 1-gamma is a 10nm-class, but that's not supposed to arrive until 2025. -

Max The Dragon Reply

HBM is not a true "Stacking", and have nothing similar to true 3D, scince planar (2D) chips are just soldered on top of each others and those memory is highly unreliable (nearly all Radeon Vega 56 and 64 are dead now).bit_user said:I find the title's use of the term "stacked DRAM" to be somewhat misleading. It's too easily confused with die-stacking, which already exists in the form of HBM and high density DDR4 and DDR5 packages.

Clearly, the article is talking about cell-stacking, akin to what NAND memory makers have been doing in their 3D NAND dies.

High density DDR packages are still planar memory. And so its still share similar technology as pre 3D Nand. -

bit_user Reply

I can't comment on Vega 56/64 (though I have my doubts), but HBM is now used lots of server-grade products that are warrantied for probably 3-5 years of 24/7 usage. So, I call "BS" on the claim that HBM is fundamentally unreliable. If your statement about those Vegas is even true, you're just extrapolating from a single data point.Max The Dragon said:HBM ... is highly unreliable (nearly all Radeon Vega 56 and 64 are dead now).

Without getting into a quagmire about terminology, die-stacking in server DIMMs has absolutely been a "thing" since DDR4:Max The Dragon said:High density DDR packages are still planar memory. And so its still share similar technology as pre 3D Nand.

https://www.anandtech.com/show/14341/samsung-samples-32-gb-ddr4-memory-chips -

usertests Reply

https://semiwiki.com/semiconductor-manufacturers/samsung-foundry/319097-a-memorable-samsung-safe-event/Max The Dragon said:Well, 3D dram, will make 128 GB+ consumer dimms possible?

It will definitely lower the price of dram in future, as 3D technology made Nand so affordable and reliable.

Plus it can give more potential to make dimms more compact without performance penalty.

We are at 24 Gb DRAM dies right now, enabling 48 GB consumer DIMMs. 32 Gb will follow shortly, enabling 64 GB DIMMs. Motherboards are already adding support for it in advance of launch, CPU pages show 256 GB support (4 DIMMs), etc.

The Samsung roadmap above shows 48 Gb after a 4 year gap, not using 3D technology. So that gets us to the 96 GB DIMM.

3D DRAM should not only make 128 GB+ possible, it should make 1 TB+ possible. Cost per bit might not decrease as fast as capacity can increase, but we can accept that. -

bit_user Reply

Yeah, I recall recently seeing someone talking about 1 TB DIMMs. Found it:usertests said:3D DRAM should not only make 128 GB+ possible, it should make 1 TB+ possible.

https://www.tomshardware.com/news/micron-preps-32gb-ddr5-chips-opening-doors-to-1tb-modules