Does High-Speed DDR3 Help AMD's FX? Four 8 GB Kits, Reviewed

Rumor has it that fast DDR3 memory kits help uncork the performance of AMD's Bulldozer architecture. We grab four of the latest kits sporting data rates as high as 2800 MT/s with the goal of finding out. One contender rises to the top in this round-up.

Overclocking And Under-Latency Results

CAS latency is measured in cycles, but cycle times get shorter as frequency is increased. As an example, DDR3-2666 CAS 16 would have the same latency in real-time as DDR3-1333 CAS 8.

Real-time latency improvement has lagged behind frequency improvement for as long as most of us can remember, and Team Group's Xtreem modules push this setting to the 15-cycle limits of some motherboards with the programmed 11-15-15-31 timings of its DDR3-2800. We used its timings as the limit for our overclocking attempts.

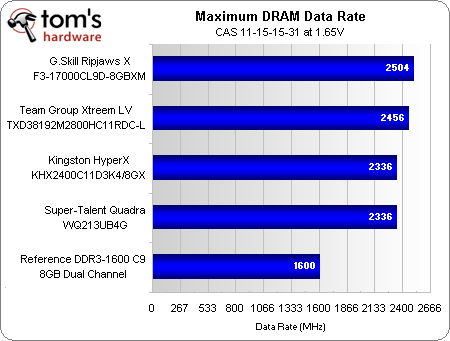

Surprisingly, G.Skill’s DDR3-2133 kit overclocked better than Team Group’s DDR3-2800 on this platform. Intel-optimized timings could bear part of the blame, but we did request that each manufacturer send its most AMD-optimized overclocking memory product, knowing ahead of time the platform we'd be using.

Article continues belowOur DDR3-1600 baseline remains at stock speed, showing how much further these overclocking-optimized modules can push the processor’s memory controller.

Of course, CAS 11-15-15-31 isn’t really needed at the motherboard’s top memory ratio. We went on to test how quickly each of these module sets could run at data rates from 1600 to 2400 MT/s.

| Best Timings at 1.65 V | ||||

|---|---|---|---|---|

| Row 0 - Cell 0 | DDR3-2400 | DDR3-2133 | DDR3-1866 | DDR3-1600 |

| Team Group Xtreem LV TXD38192M2800HC11RDC-L | 9-12-11-24 | 8-10-10-24 | 7-9-8-24 | 6-8-7-21 |

| G.Skill Ripjaws X F3-17000CL9D-8GBXM | 10-12-11-24 | 9-11-10-24 | 8-10-9-24 | 7-9-8-24 |

| Super Talent Quadra WQ213UX16G | Unstable | 9-12-10-28 | 8-10-9-25 | 7-9-8-22 |

| Kingston HyperX KHX2400C11D3K4/8GX | Unstable | 10-12-10-30 | 8-10-9-25 | 7-9-8-22 |

| Reference DDR3-1600 C9 8GB Dual Channel | Row 5 - Cell 1 | Row 5 - Cell 2 | Row 5 - Cell 3 | 9-9-9-28 |

Proving that it didn't send us a one-trick pony, Team Group’s top-rated DDR3-2800 also tops all of our latency tests.

Note that tRAS appears unrealistically long for all of our tests. That’s because we set it to its best performing setting. Whilst some of these modules could operate stable at half the shown tRAS, any tRAS setting outside of the 21-24 cycle range would cause a stumble in Sandra's Memory Bandwidth benchmark module. This appears to be AMD-specific, since we’ve achieved higher performance at far lower tRAS on several Intel processors.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: Overclocking And Under-Latency Results

Prev Page Test Setup And Benchmarks Next Page DDR3-1600 Performance-

Rockdpm Interesting!. Still would wait for Pile driver. But since i do have a Kingston 8GB kit and a Sabertooth 990FX... may just have to try it one dayReply -

jdwii Great article this proves a lot of rumors!Reply

People can finally stop saying how unfair it is to test Amd with slower ram when it supports higher speed ram even though higher speed ram cost more money. It would actually be unfair to Intel its not their fault Amd needs higher speeds to compete(which it doesn't) with Intel's 1333 ram controller.

Ram speeds do how ever make a big difference on APU's. -

mayankleoboy1 would love to see the same review for Ivy Bridge processors with and without iGPU HD4000.Reply

and do include more tests in the review. -

Crashman sarinaideMore of the cheap stuff is my mantra.Yeh yeh, but I really can't complain about paying $70 for 8GB of DDR3-2133, especially when it overclocks like that.Reply -

Reynod AMD has enjoyed the performance benefits of an integrated memory controller for more than twice as long as Intel. And yet, it seems that Intel sets today's standard for acceptability.Reply

Replace the last word with "performance" crash.

Good article which gets answers a couple of questions people have been asking - well done !!

:) -

jaquith Thomas thanks for the review.Reply

First note:

*KHX2400C11D3K4/8GX - is a Quad Channel kit specifically designed for the X79 ; link http://www.kingston.com/us/company/press?pagename=n1111c&year=2011&prLanguage=english_emea

*WQ213UB4G vs WQ213UX16G (kit) - is ONE stick of RAM (not a matched kit) and its 'kit version' is Quad Channel kit specifically designed for the X79 ; link http://www.supertalent.com/datasheets/WQ213UX16G.pdf

After that it makes sense that those (2) "kits" (in one case 4 individual sticks) failed @ Rated, and I wasn't interested in researching the others. I've seen other more in-depth testing on the AMD FX-8150 indicating that overall there's a slight advantage for the DDR3-1866 kits on a most of the AMD FX processors. Though @ 4AM 'to me' I'll edit this post after a few cups of coffee.

The 'ideal' AMD kits have JEDEC 'SPD' @ Rated 'cloned' (XMP) encoding which is optimized for AMD and sometimes slightly different so you're not 'stuck' as you put it @ DDR3-1333. Those are the better KITS to test on the AMD FX lines. -

SteelCity1981 Ram sppeds on a Bulldozer CPU means little and this just proves that so it doesn't matter if you are using DDR3 1600 ram or buying high performance RAM that can overclock to DDR3 2800 your not really seeing hardly any improvement with Bulldozer by doing so.Reply -

RAM speed also has a HUGE impact in controlled cache environments:Reply

http://thessdreview.com/our-reviews/romex-fancycache-review-ssd-performance-at-13gbs-and-765000-iops-in-60-seconds-flat/

Even the best SSDs can barely muster 100,000 IOPs, yet even slow RAM can easily exceed 700,000 IOPs.

Bandwidth, throughput, and latency are equally insane. RAM puts SSDs to shame exponentially more than SSDs put hard drives to shame. Contrary to what many "enthusiasts" believe, RAM timings are virtually irrelevant. Frequency is by far, much more important.