Intel's 15 Most Unforgettable x86 CPUs

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

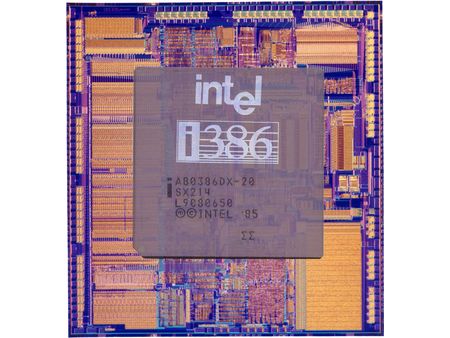

386: 32-Bit and Cache Memory

Intel’s 80836 was the first x86 with a 32-bit architecture. Several versions of this processor were offered. The two best known are the 386 SX (Single-word eXternal), which had a 16-bit data bus, and the 386 DX (Double-word eXternal) with a 32-bit data bus. Two other versions are worth noting, though: the SL, which was the first x86 to offer management of a cache (external) and the 386EX, used in the space program (the Hubble telescope uses this processor).

| Code name | P3 |

| Date released | 1985 |

| Architecture | 32 bits |

| Data bus | 32 bits |

| Address bus | 32 bits |

| Maximum memory | 4096 MB |

| L1 cache | 0 KB (controller sometimes present) |

| L2 cache | no |

| Clock frequency | 16-33 MHz |

| FSB | same as clock frequency |

| FPU | 80387 |

| SIMD | no |

| Fabrication process | 1,500-1,000 nm |

| Number of transistors | 275,000 |

| Power consumption | 2 W @ 33 MHz |

| Voltage | 5 V |

| Die surface area | 42 mm² @ 1µ |

| Connector | 132 pins |

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: 386: 32-Bit and Cache Memory

Prev Page 80286: 16 MB Of Memory, But Still 16 Bits Next Page The 486: An FPU And Multipliers TooTom's Hardware is the leading destination for hardcore computer enthusiasts. We cover everything from processors to 3D printers, single-board computers, SSDs and high-end gaming rigs, empowering readers to make the most of the tech they love, keep up on the latest developments and buy the right gear. Our staff has more than 100 years of combined experience covering news, solving tech problems and reviewing components and systems.

-

Arkz great article with only a few slight errors (like saying the core2duo has 1-4 cores... i don't think there's a 1 cored version lol)Reply

Looking forward to the AMD article. -

aleluja To correct you. Core 2 Duo has ONLY 2 cores, not more, not less.Reply

Core 2 Quad, has 4 cores and Core Solo has 1 core.

-

@ArkzReply

Yes there is a singal core,

http://en.wikipedia.org/wiki/List_of_Intel_Core_2_microprocessors#Single-Core_Mobile_processors

Ok it is not under the same branding but it is part of the same microarchitecture -

-Fran- I might be wrong, but i resemble that the Pentium 166 (32bits adress bus and all) had support for 4Gb of memory. I remember IBM sold it's top line (at that time) with 64Mb support (even with SDR PC100/66 support). Correct me if i'm wrong please.Reply -

neiroatopelcc The core 2 does supply 1-4 cores - 2 cores per die, where one might be disabled, and one or two dies on a socket. It's no less right to call a core2duo a cpu with 1-4 cores, than it is to put the pentium d on the same page as a single core prescot, as it's the very same principle.Reply -

cangelini Arkzgreat article with only a few slight errors (like saying the core2duo has 1-4 cores http://en.wikipedia.org/wiki/Coree ... i don't think there's a 1 cored version lol)Looking forward to the AMD article.Reply

Thanks for the heads-up! I tweaked that passage to better represent the Core 2 architecture's available configurations! -

randomizer vosesterOk it is not under the same branding but it is part of the same microarchitecture Exactly. The article says:Reply

ArticleThere are many versions of the architecture, resulting in configurations with a different number of cores

There is no mention of the branding, so there is no actual error there, just misinterpretation. -

ImSpartacus Arkzgreat article with only a few slight errors (like saying the core2duo has 1-4 cores... i don't think there's a 1 cored version lol)Looking forward to the AMD article.Reply

http://www.newegg.com/Product/Product.aspx?Item=N82E16819116039

Yes, it isn't called a "Core 2 Duo," but it uses the Core architecture and only has a single core enabled.

But I will have to say, there aren't any 3 core models... -

magicandy Good to hear you're not only doing an AMD article, but an ATI one as well (in response to the Nvidia article you did earlier, assuming). A sign of class from the new Tom's is a welcome one.Reply -

harrycat88 I wish they would get rid of those stupid SNAP Linkbubless and Inteltex misguiding links. Who ever invented those stupid annoying double lined text popups should have been burned at the stakeReply