Intel Moves From Dual Core To Double Core

Intel's Double Core Design Approach

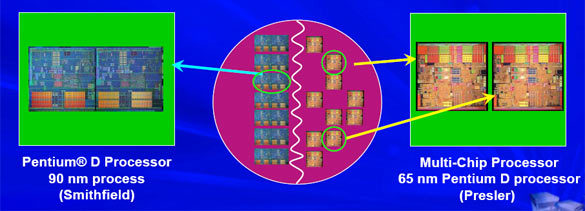

There are three possible ways to create a dual core chip today. The first is to use a monolithic die, which is what Intel is doing with the latest Itanium chip based on the Montecito core. The second is combining two cores on a single die, which we have already seen in the Pentium D Smithfield. The third option is to place two dies into one package. The concept of having a monolithic dies gives developers more opportunities to share certain processor units and potentially helps to increase performance, while the other solutions are more economic to implement.

The last option certainly is the most economic way to go dual core, as it allows the company to maximize yield rates across different products. A functionality test of each chip reveals whether there are production-related issues. Should there be problems within the L2 cache area or functional units that are not used for lower-end processors, these units can be disabled; for example, the unit could have its L2 cache size cut down to 512 kB or 256 kB to make it a future 65 nm Celeron.

Those chips that pass the function test will now be speed and voltage rated. Specimens with high clock speed tolerances will become fast single core Pentium 4 processors, while the others can be matched and fit into double core Pentium D models.

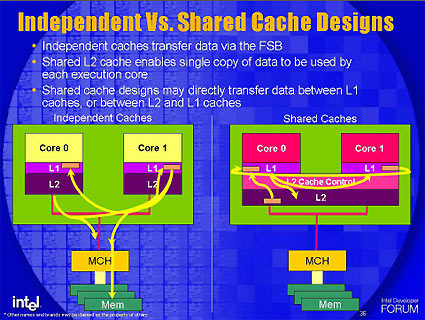

There is, however, one major disadvantage to pooling two basically independent cores into one package. Each time one core needs to access data the other one is working with, the system bus has to be utilized. It is not hard to imagine that this can cause a considerable overhead. And this is not only the case for the double core 65 nm Presler chips, but also for the 90 nm Smithfield dual core, which is little more than two cores merged into one die. On the other hand, a shared cache design raises the problem of cache allocation for each core, which is why neither AMD nor Intel have this type of product yet.

Intel announced its intention to introduce a shared L2 cache design with its upcoming micro architecture in H2/2006 - Woodcrest in servers, Conroe in desktops and Merom in mobile computers). We would expect AMD to do the same with the launch of its socket M2 based Windsor (dual core) and Orleans Athlon 64 processors, named Revision F. However, the information that has been available to us does not yet indicate an early adoption of such a design. Still, this is still far enough away that any judgment now would be premature.

This is a functional diagram of the Pentium D 800 series based on the Smithfield core. Presler will be exactly the same thing, with the two cores physically moved away from each other.

According to current documents, AMD does is not going after a unified L2 cache for dual processors. Yet.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: Intel's Double Core Design Approach

Prev Page 65 nm Intel Double Core Preslers Forward Next Page Presler Processor Details

Patrick Schmid was the editor-in-chief for Tom's Hardware from 2005 to 2006. He wrote numerous articles on a wide range of hardware topics, including storage, CPUs, and system builds.