Phison S10: Toshiba MLC And TLC Versus Micron L95B MLC

Phison offered to let us test its S10 controller with three flash types that will ship in 2015: Toshiba's A19 TLC, 15nm MLC and Micron L95B 16nm MLC.

Technical Specifications

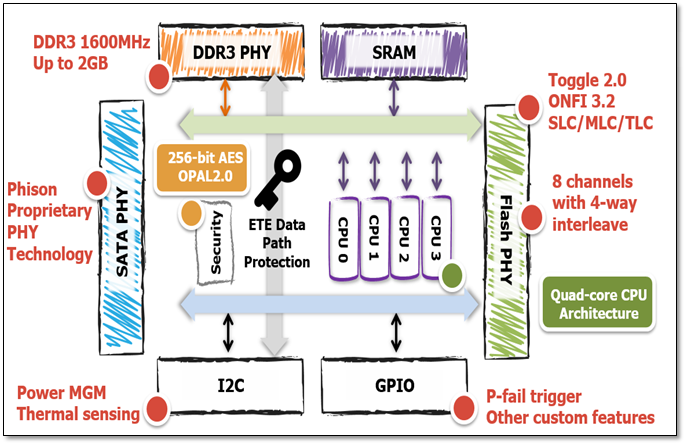

Phison's S10 controller consists of a quad-core CPU, 32 flash CEs (expanded to 64 CEs), DDR3 support, a 256-bit AES on-the-fly engine and end-to-end data path protection.

Before we dive into the flash, let's take a closer look at the S10 and why we chose to use it for this project. Phison is an agnostic controller manufacturer. The company doesn't produce NAND, so it doesn't favor one type of memory over another. In order to thrive, Phison has to support every type of flash.

Phison doesn't sell retail products. Instead, it enables the companies you've purchased SSDs from to create new offerings. The S10 controller we're using today is already shipping inside of Corsair's Neutron XT, the HyperX Savage, Patriot's Inferno and Mushkin's Striker. Some of those drives use Toshiba A19 MLC flash and others use Micron L95B 16nm MLC.

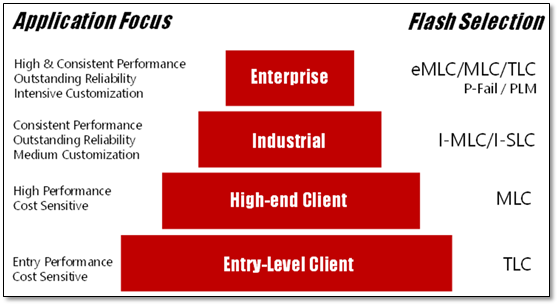

Article continues belowPhison is working on firmware that will enable more advanced features, allowing the S10 to work in more markets. At Computex, we saw designs like the enterprise 2TB model with full host power fail protection. The S10 is a Swiss Army controller that can take on any role through quality engineering. Moving forward, the S10 should address the following markets:

Enterprise

Hyperscale computing requires consistent performance and low latencies. The choice of NAND is what defines whether an SSD can handle read-intensive or write-intensive workloads. You'll see those characteristics in the drive-write-per-day (DWPD) specifications.

In addition, the PLM features on S10-based drives provide protection against sudden power loss, which is key to the zero-downtime requirement of many enterprises. This is especially useful if a storage system does not enjoy the benefit of SSDs in RAID.

Industrial

Industrial SSDs are often utilized in environments with hostile temperatures, vibration and humidity. The S10 controller supports industrial-grade options from -40 to 85 degrees C. The PLM features also come in handy for industrial applications, since some of those demand zero downtime as well.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

High-end Client

The quad-core S10 controller enables performance that can almost saturate the SATA interface. It's a top performer in several of our performance benchmarks. Gaming enthusiasts should be excited by its high I/O per second and 560 MB/s throughput.

Entry-level Client

The S10 has a strong ECC engine to enable TLC-equipped SSDs for the entry-level client market, where price is the king. The major challenge of TLC is its endurance and performance. Data protection features help extend the SSD's useful life. And we expect the performance of S10-equipped SSDs with TLC flash to compete with existing SSDs armed with MLC NAND, making the transition from MLC to TLC largely transparent.

Now, let's look at the advanced features built into the S10.

Quad-core CPU: the S10 is equipped with quad-core CPU, three of which are dedicated to flash management, sustaining performance when the SSD is in a dirty state. The smaller the swing, the lower the command latency.

256-bit AES Engine: the S10 offers AES-256 encryption options for corporate demands (like TCG Opal) and government regulation (like FIPS-140-2). TCG Opal 2.0 Self-Encryption Drive Technology is also supported, protecting sensitive data from loss, re-purposing or end-of-life.

Eight-Channel and 2TB Support: the S10 operates with eight flash channels and four-way interleaving. It is designed to have enough drive power to support up to 2TB of capacity without sacrificing performance. It also has optional support for full device capacity without over-provisioning.

TLC Support: the S10 is Phison’s first SSD controller supporting TLC. Its BCH ECC engine is specially designed for 1y/1znm TLC flash.

Power-Fail Circuit: the S10 reference design enables full power-loss protection. An on-board capacitor provides the power needed for the controller to flush data from the DRAM to NAND, where it's secured.

End to End Data Path Protection: this enterprise feature detects and corrects bit errors within the controller data paths.

SmartECC: the ECC scheme implements multiple levels of correction to not only provide the basic ECC engine capability that flash requires, but also extends NAND durability with the addition of page RAID ECC Parity. The Multi-Level ECC scheme can be summarized as follows:

• Level 1: Read Retry

• Level 2: Standard BCH ECC Parity in spare area

• Level 3: Page RAID ECC Parity

Page RAID ECC Parity is able to recover otherwise uncorrectable ECCs with following steps:

1. Uncorrectable error is detected

2. SmartECC engine starts to reconstruct the defective data by using RescueParity that was previously generated and stored in other pages.

3. The recovered data will be stored in a new page. The original block will be marked bad.

SmartRefresh: this feature is to designed fight read disturb. There are two triggering schemes: run-time media scan (RS) and idle-time media scan (IS).

SmartFlush: this is a proprietary algorithm to minimize DRAM utilization for user data. There are two main features:

Smart On-the-fly Flushing (SOF)

• Constant flushing to minimize the time data stays in the cache.

• Re-organize random data chucks in cache before flushing to NAND to reduce WAF.

Smart Triggered Flushing (STF)

• Link Loss Triggering

• DevSlp Triggering

• Idle-Time Triggering

GuaranteedFlush: the Flush Cache command is a standard SATA command to ensure specific data is saved to NAND instead of the DRAM cache, which can help protect important user data against power loss. However, due to the pair-page effect of flash, data written before the Flush command may be affected by data written afterwards.

P-Fail (Full Power Loss Protection) Circuit: for mission critical applications, where full data integrity is desired, the S10 provides the capability to use its on-board capacitor to fully protect un-recoverable data in the DRAM during a power loss event. When voltage drops below a threshold, the power detection circuit kicks in, and the firmware prepares for exit strategies for a safe shut down.

Chris Ramseyer was a senior contributing editor for Tom's Hardware. He tested and reviewed consumer storage.

-

James Mason Replywhoa, where did you guys get some 4800GB just for the battery life tests?

Yeah so many typos I almost thought they actually did get 5 terabyte SSDs somehow.

-

Frozen Fractal I was arranging a chart while reading this article to see who actually wins. Seems like Toshiba 15nm MLC wins the test, with Micron 16nm MLC close on tail and TLCs wayyyy off :D.Reply

It is kinda disappointing to see TLCs being outperformed so brutally. I guess increased SLC buffer should mitigate the problem? Samsung already has like this in the EVO 2TB so what do you think Chris?

Also, does lithography has anything to do with performance? I mean Micron's NANDs are close to Toshiba's MLCs and Micron's cells are just 1nm bigger than Toshiba's MLCs. Can this be co-related somehow? -

WyomingKnott It is so cool that they provided these for a head-to-head comparison. Finally, a comparison with all other variables really held even.Reply