Intel 3 '3nm-class' process technology is in high-volume production: Intel

A datacenter-oriented node.

Intel on Wednesday said that its 3nm-class process technology called Intel 3 has entered high volume production at two sites as well as provided some additional details about the new production node. The new process brings in both higher performance and higher transistor density as well as supports voltages of 1.2V for ultra-high-performance applications. The node is aimed at Intel's own products as well as at foundry customers. It will also evolve over the coming years.

"Our Intel 3 is in high volume manufacturing in our Oregon and Ireland factories, including the recently launched Xeon 6 'Sierra Forest' and 'Granite Rapids' processors," said Walid Hafez, Foundry Technology Development Vice President at Intel.

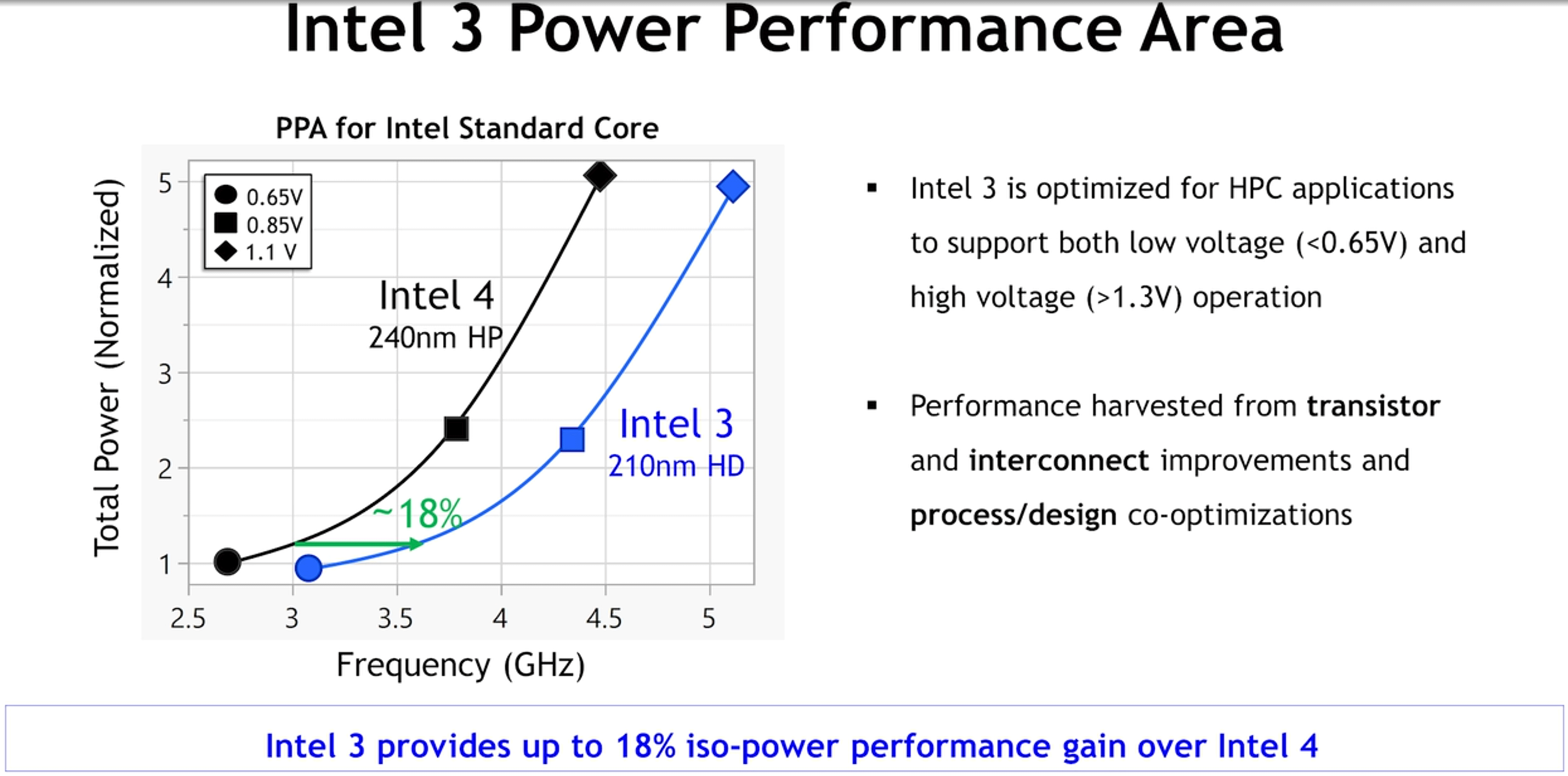

Intel has always positioned its Intel 3 fabrication process to be aimed at datacenter applications that require leading-edge performance enabled by revamped transistors (compared to Intel 4), their power delivery circuitry with reduced transistor via resistance, and design co-optimization. The production node supports both <0.6V low voltage as well as >1.3V high voltage for maximum loads. When it comes to performance, Intel promises that the new node will enable 18% higher performance at the same power and transistor density compared to Intel 3.

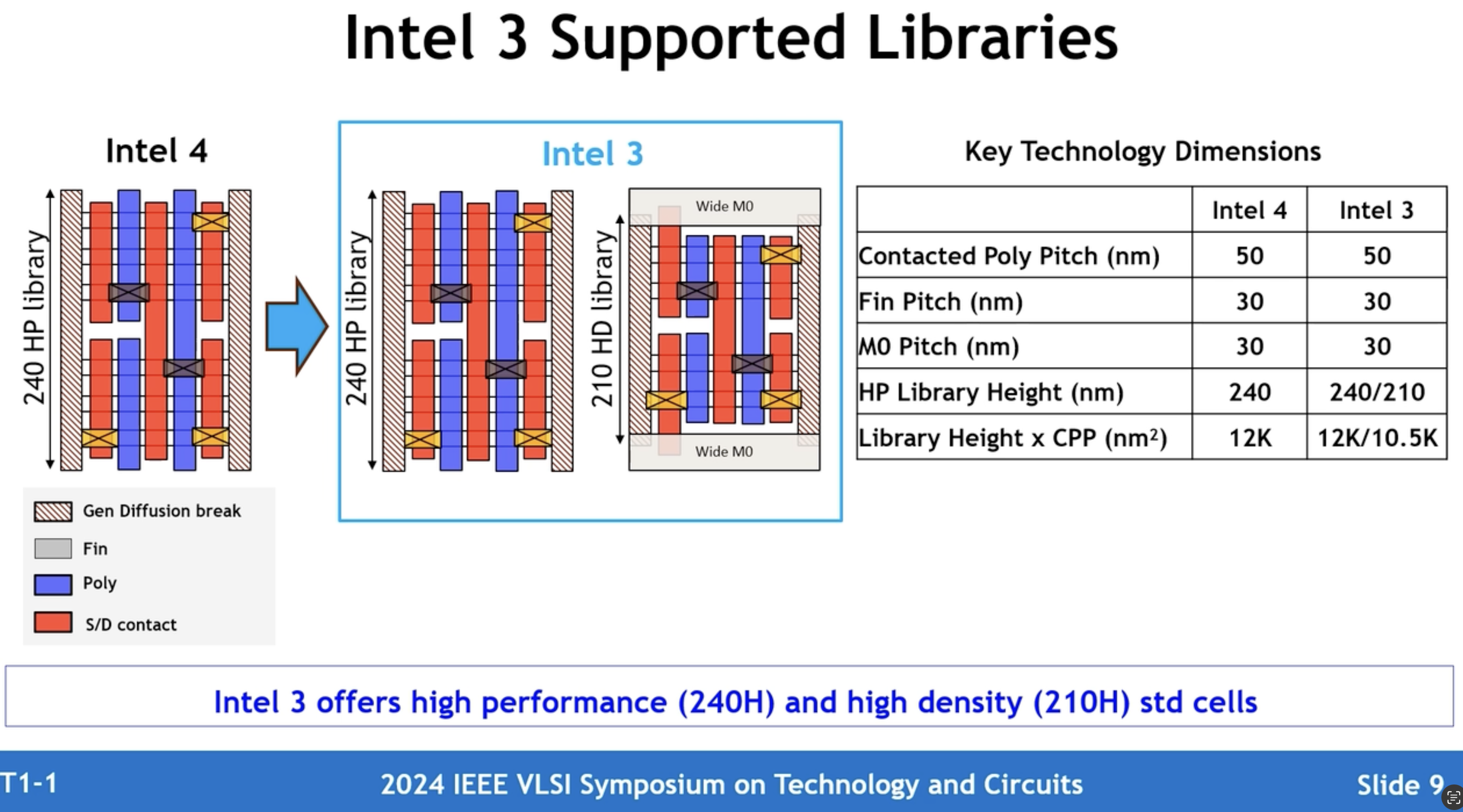

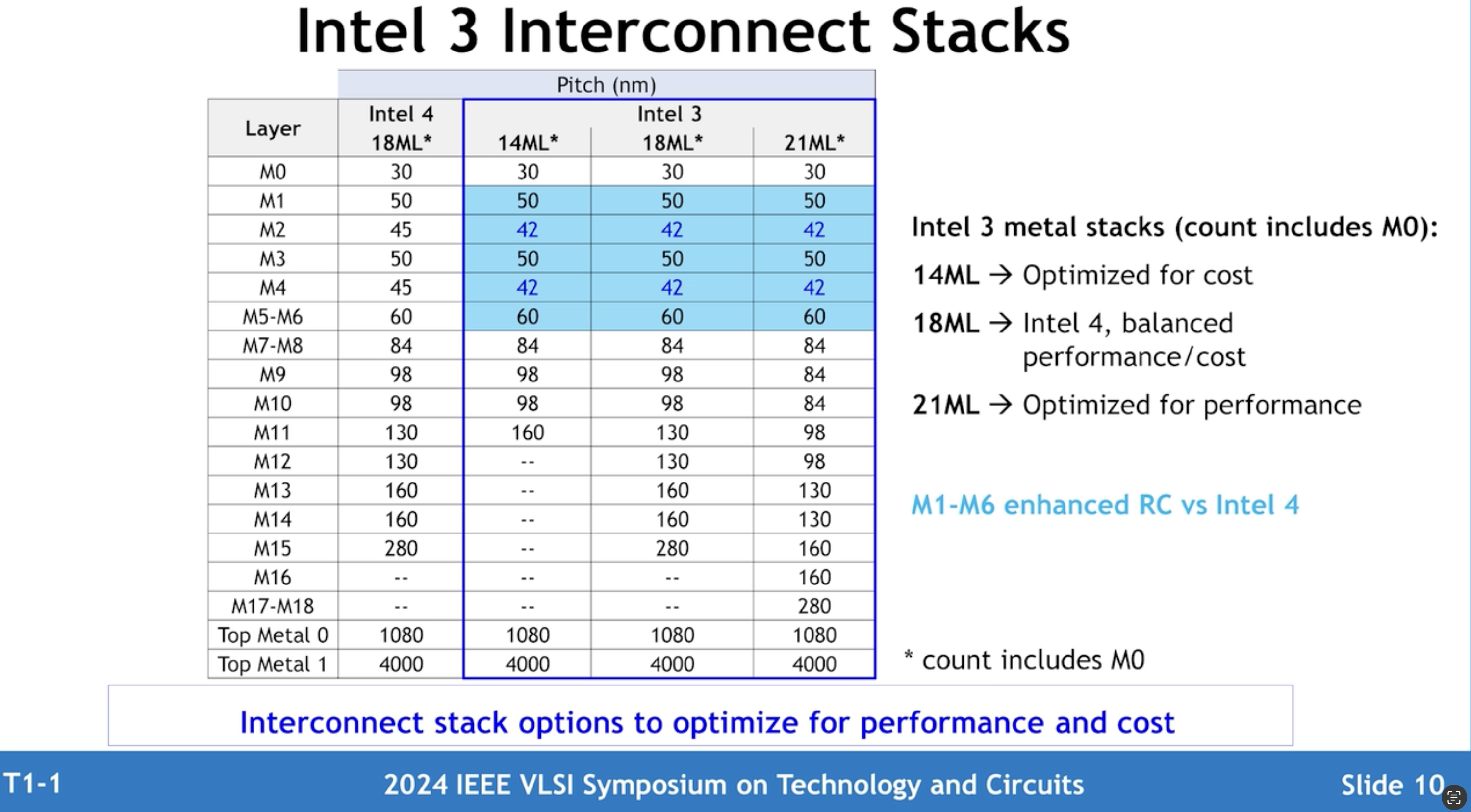

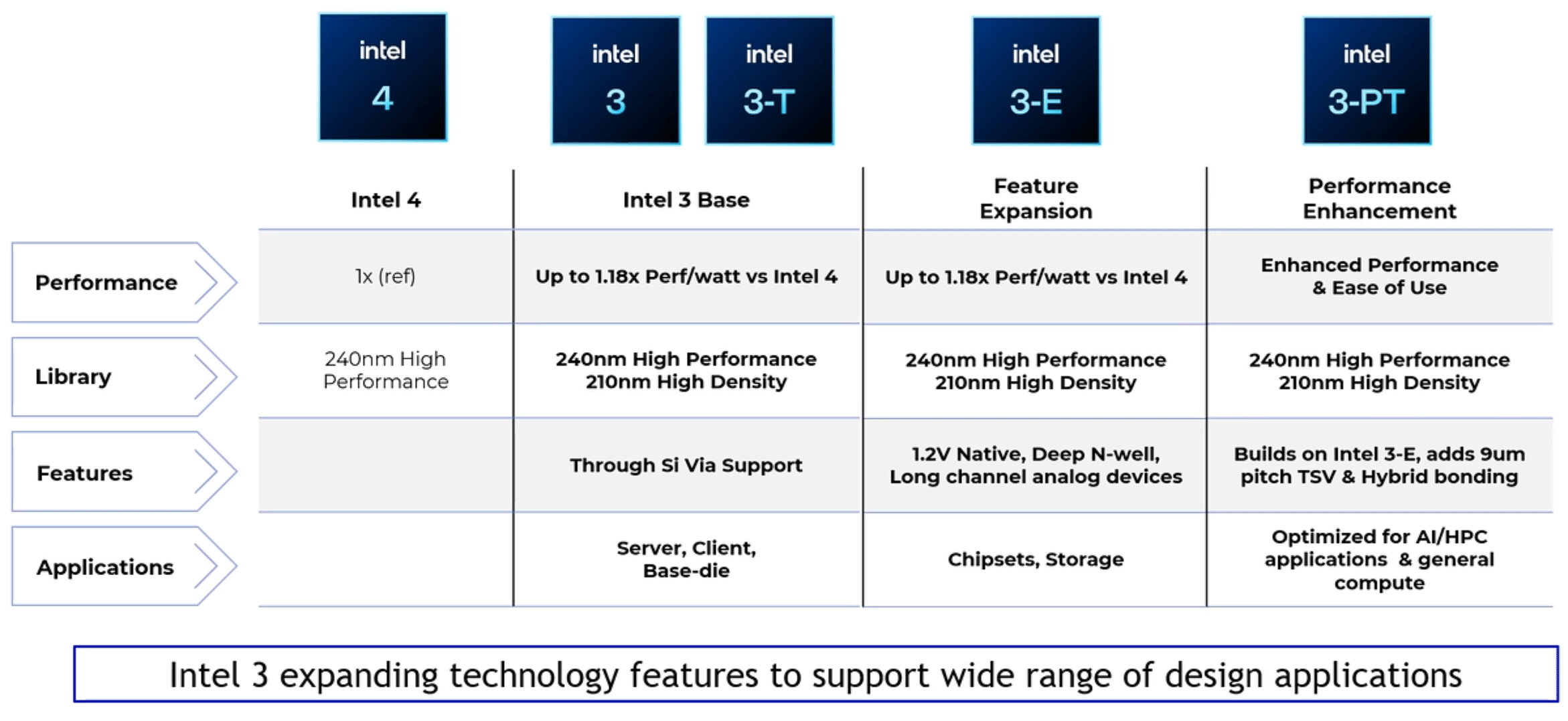

Article continues belowTo get the best combination of benefits for performance and density, chip designers will have to use a combination of 240nm high performance and 210nm high density libraries. Furthermore, Intel clients can choose between three metal stacks: 14 layers for costs, 18 layers for an optimal balance between performance and cost as well as 21 metal layers for higher performance.

For now, Intel will use its 3nm-class process technology to make its Xeon 6 processors datacenters. Eventually Intel Foundry will use the production node to manufacture datacenter-grade processors for its customers.

In addition to base Intel 3, the company will also offer Intel 3T that supports through silicon vias and can be used as a base die. In the future, Intel will offer feature-enhanced Intel 3-E for chipsets and storage applications, and performance-enhanced Intel 3-PT that can be used for a wide range of workloads, such as AI/HPC and general purpose PCs.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

The Historical Fidelity Well it’s official, now Intel’s nm designation is copium. Intel 3 is classified as 5nm according to IEEE specifications with 50nm gate pitch and 30nm interconnect pitch. TSMC N3 actually beats IEEE specifications for 3nm at 48nm gate pitch and 23nm interconnect pitch.Reply -

thestryker Reply

I'm sure the IEEE would be surprised to know they set industry specifications for process nodes good thing you're here to let everyone know.The Historical Fidelity said:Well it’s official, now Intel’s nm designation is copium. Intel 3 is classified as 5nm according to IEEE specifications with 50nm gate pitch and 30nm interconnect pitch. TSMC N3 actually beats IEEE specifications for 3nm at 48nm gate pitch and 23nm interconnect pitch. -

The Historical Fidelity Reply

I’m pretty sure IEEE knows about their own “Semiconductor Standards Association” and their yearly “International Roadmap for Devices and Systems” reports.thestryker said:I'm sure the IEEE would be surprised to know they set industry specifications for process nodes good thing you're here to let everyone know. -

NinoPino Reply

Sssssh, don't say it to Intel investors. 😀The Historical Fidelity said:Well it’s official, now Intel’s nm designation is copium. Intel 3 is classified as 5nm according to IEEE specifications with 50nm gate pitch and 30nm interconnect pitch. TSMC N3 actually beats IEEE specifications for 3nm at 48nm gate pitch and 23nm interconnect pitch. -

thestryker Reply

Which doesn't set "measurement" standards for the industry and is based on what the industry is doing and thus shifts categorization accordingly. If you look at earlier reports what you're claiming defines 3nm was 5nm as IRDS is based on what is happening not setting standards. GMT is no more a "standard" than LMC is they're just measurement techniques.The Historical Fidelity said:I’m pretty sure IEEE knows about their own “Semiconductor Standards Association” and their yearly “International Roadmap for Devices and Systems” reports. -

bit_user Reply

Seems like a foregone conclusion, given that Sierra Forest launched and that's based on Intel 3. So is Granite Rapids, which they say is on track.The article said:Intel on Wednesday said that its 3nm-class process technology called Intel 3 has entered high volume production at two sites as well as provided some additional details about the new production node.

I'm not saying the extra details aren't nice for some, but if you were paying attention this should come as no surprise. -

ToBeGood Reply

Hi TSMC fanboy,NinoPino said:Sssssh, don't say it to Intel investors. 😀

Sssssh, just want to say to you quietly that N3E is N5++ is a 5nm class device, N3B != N3E

Sssssh, Intel Sierra Forest is now out as well, just same time frame is Apple M4,

Sssssh, Intel catch up with TSMC.

Sssssh, do let the TSMC shareholder knows. -

bit_user Reply

What's funny about this claim is that Lunar Lake supposedly used TSMC N3(B?) because it was the best-performing node available to the designers, at the time. So, what do you suppose it says that the designers chose it over Intel 3?ToBeGood said:Sssssh, Intel catch up with TSMC. -

thestryker Reply

To be fair to Intel here the chances of Intel 3 being available for LNL is approximately zero due to capacity (Intel 4 and 3 use the same equipment and fabs). That being said I'd be surprised if Intel 3 would have been as good for it as N3B (the high density might be for high efficiency mobile, but not enough details to know one way or the other).bit_user said:What's funny about this claim is that Lunar Lake supposedly used TSMC N3(B?) because it was the best-performing node available to the designers, at the time. So, what do you suppose it says that the designers chose it over Intel 3?