AMD EPYC Genoa-X Wields 1.3 GB of L3 Cache, 96 Cores

Second-Gen 3D V-Cache Debuts on EPYC Genoa-X.

AMD announced a range of new products today at its Data Center and AI Technology Premiere event here in San Francisco, California. The company shared more details about its EPYC Genoa-X processors with up to 1.1GB of L3 cache, which are shipping now.

AMD also detailed its 5nm EPYC Bergamo processors for cloud-native applications and announced its Instinct MI300 processors that feature 3D-stacked CPU and GPU cores on the same package with HBM, along with a new GPU-only MI300X model that is also used to bring eight accelerators onto one platform that wields an incredible 1.5TB of HBM3 memory. All three of these products are available now, but AMD also has its EPYC Sienna processors for telco and the edge coming in the second half of 2023.

AMD EPYC Genoa-X

Much like its predecessor, Milan-X, AMD's new Genoa-X is designed for a range of technical workloads, like CAD design flows and EDA. The chip follows the same design philosophy of the company's previous-gen EPYC Milan-X processors, which employ 3D V-Cache, a novel new technique that uses hybrid bonding to fuse an additional 64MB of 7nm SRAM cache vertically atop the Ryzen compute chiplet, thus tripling the amount of L3 cache per die. AMD employs its second-gen 3D V-cache with Genoa-X, and you can read the deep-dive details of the hybrid bonding technology here and here.

| Processor | Price (1KU) | Cores/Threads | Base/Boost Clock (GHz) | L3 Cache (L3 + 3D V-Cache) | TDP | cTDP (W) |

| Genoa-X 9684X | $14,756 | 96 / 192 | 2.55 / 3.7 | 1,152 MB | 400W | ? |

| EPYC 7773X | $8,800 | 64 / 128 | 2.2 / 3.5 | 768MB | 280W | 225-280W |

| Genoa-X 9384X | $5,529 | 32 / 64 | 3.1 / 3.9 | 768MB | 320W | ? |

| EPYC 7573X | $5,950 | 32 / 64 | 2.8 / 3.6 | 768MB | 280W | 225-280W |

| EPYC 7473X | $3,900 | 24 / 48 | 2.8 / 3.7 | 768MB | 240W | 225-280W |

| Genoa-X 9184X | $4,928 | 16 / 32 | .55 / 4.2 | 768MB | 320W | ? |

| EPYC 7373X | $4,185 | 16 / 32 | 3.05 / 3.8 | 768MB | 240W | 225-280W |

Genoa-X brings the Zen 4 architecture to bear and kicks the L3 cache up a notch with up to 1.1 GB of L3, a 43% increase over the 768 MB found on the previous-gen model. Genoa-X also tops out at a 96-core model, a marked increase over the previous-gen's peak of 64 cores. The chips drop directly into existing SP5 sockets, thus leveraging the existing server and workstation ecosystem. The chips top out with a 400W TDP with the 96-core model and extend down to 320W with the 16-core chip.

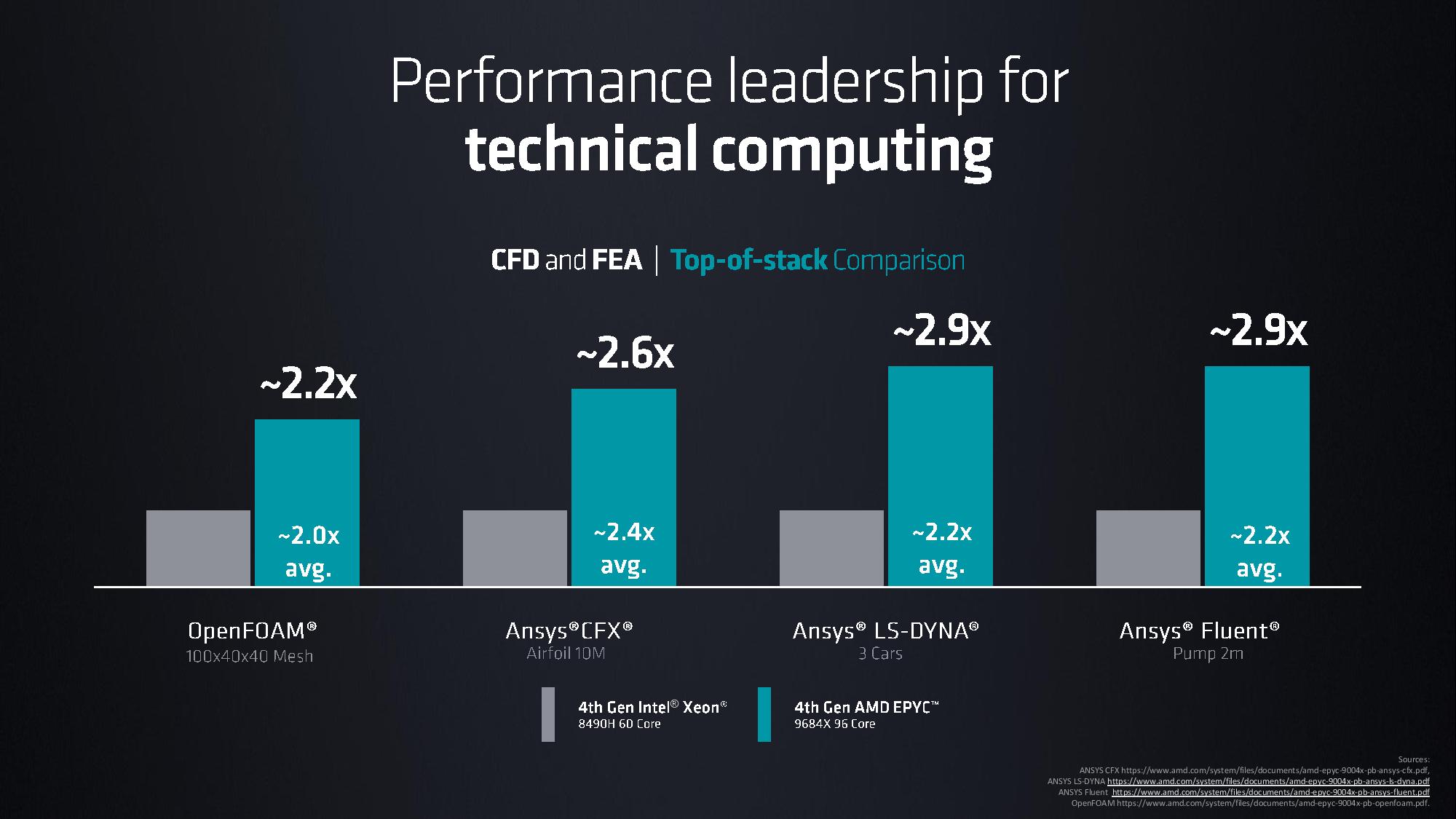

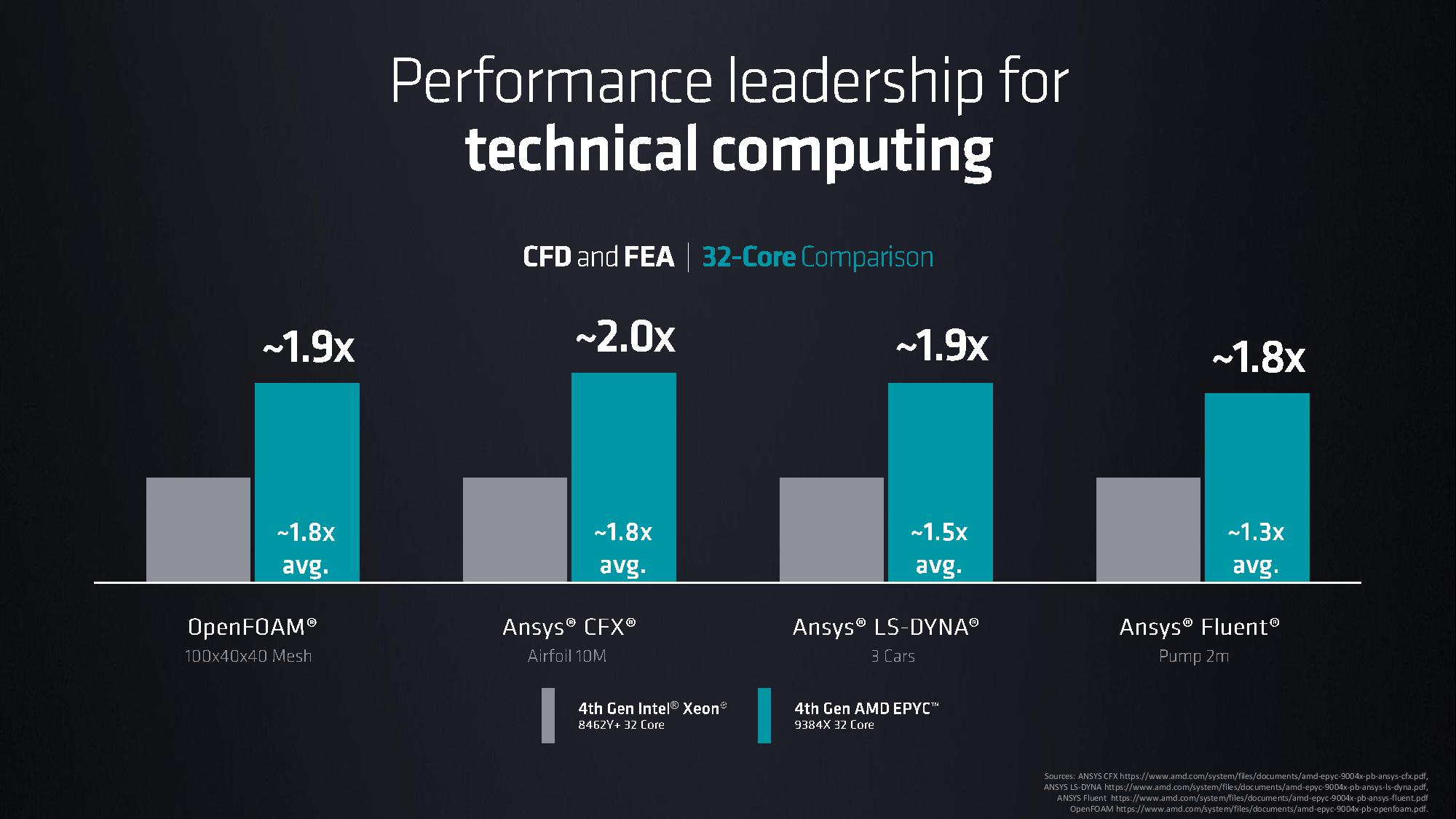

AMD provided benchmarks showing Genoa-X going head-to-head with Intel's 80-core 8490H Xeon with impressive gains, and a comparison with an Intel Xeon with the same number of cores, again exhibiting marked performance gains in various technical workloads.

Microsft also announced that its Azure cloud have general availability of its new HBv4 and HX-series instances with Genoa-X, and new HBv3 instances. Azure also provided benchmarks to show the performance gains, which top out at 5.7X gains.

We're running down more details about the chips, stay tuned for updates.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

abufrejoval I'm tempted to ask "but does it run Windows 95?"Reply

I am trying to think which OS variants I was actually operating when main memory was around 1GB.

I believe Windows 95 and its ilk actually topped out at 512MB, so Windows NT 3.51 or 4.0, perhaps 2000 seem likely, I held on to AMD K2/KIII very long before I went with various AMD64 until the Q6600 thrashed them. But since AMD64 meant bridging the 4GB barrier of 32-bit, that must have been later.

Anyhow, at this point you'd want a RAM-less mode supported by the chip, if only for kicks, which allows you to actually run a fully functional 64-Bit OS only from cache... -

derekullo I got me a 1.3 gigabytes of cacheReply

I never feed trolls and I don't read bash

Installed a fiber line in my house

Always at my PC, double-clickin' on my mizouse

...forgive me -

hotaru.hino Reply

Considering LGR couldn't get MS-DOS working properly on a Ryzen 1700, I'd say no. He got FreeDOS to work, but I don't know if Windows 95 can be installed on top of that.abufrejoval said:I'm tempted to ask "but does it run Windows 95?"

I am trying to think which OS variants I was actually operating when main memory was around 1GB.

I believe Windows 95 and its ilk actually topped out at 512MB, so Windows NT 3.51 or 4.0, perhaps 2000 seem likely, I held on to AMD K2/KIII very long before I went with various AMD64 until the Q6600 thrashed them. But since AMD64 meant bridging the 4GB barrier of 32-bit, that must have been later.

Anyhow, at this point you'd want a RAM-less mode supported by the chip, if only for kicks, which allows you to actually run a fully functional 64-Bit OS only from cache...

The only problem with running in cache only is the 1.3GB of LLC is spread around the chiplets, so you'd actually have a NUMA system if you could even treat cache like addressable memory. -

bit_user Reply

Fun idea, but I think the L3 on each chiplet is only populated by the cores on that chiplet. So, to run in a DRAM-less mode (which would encounter all kinds of practical obstacles, let's be clear), you'd be limited to just 128 MB.abufrejoval said:Anyhow, at this point you'd want a RAM-less mode supported by the chip, if only for kicks, which allows you to actually run a fully functional 64-Bit OS only from cache... -

bit_user Reply

Unlike Windows 3.1, I don't think Win 95 booted into DOS, first.hotaru.hino said:Considering LGR couldn't get MS-DOS working properly on a Ryzen 1700, I'd say no. He got FreeDOS to work, but I don't know if Windows 95 can be installed on top of that. -

snemarch Reply

It KindaSorta™️ does – and if you boot to straight DOS mode, you can even run "win" to start from there. WinME was somewhat... different.bit_user said:Unlike Windows 3.1, I don't think Win 95 booted into DOS, first.

I used to run a manually stripped-down 95sr2 (I think I got it down to like 15 megs?) as basically a supercharged dos extender – didn't use a whole lot of Windows apps at the time, but it let me do preemptive multitasking of DOS applications, and the disk caching was a lot faster and more stable than smartdrv. -

sferguson Reply

When was himem.sys (it’s been a while, I might be remembering the wrong name) developed? I remember that file being present in some DOS systems that I used, but that might have been around the time of 98se… that took max RAM to 768MB, if I am remembering correctly.abufrejoval said:I'm tempted to ask "but does it run Windows 95?"

I am trying to think which OS variants I was actually operating when main memory was around 1GB.

I believe Windows 95 and its ilk actually topped out at 512MB, so Windows NT 3.51 or 4.0, perhaps 2000 seem likely, I held on to AMD K2/KIII very long before I went with various AMD64 until the Q6600 thrashed them. But since AMD64 meant bridging the 4GB barrier of 32-bit, that must have been later.

Anyhow, at this point you'd want a RAM-less mode supported by the chip, if only for kicks, which allows you to actually run a fully functional 64-Bit OS only from cache... -

bit_user Reply

According to this, it came with Windows 2.1 and MS DOS 5.0:sferguson said:When was himem.sys (it’s been a while, I might be remembering the wrong name) developed? I remember that file being present in some DOS systems that I used,

https://en.wikipedia.org/wiki/HIMEM.SYS

IIRC, what it did was to let you access the 64 kB segment at the top of the address range. That's something even a 286 could do (hence, the logic of including it with Windows 2.1).

EMM386 was another popular "hack", during the late DOS era. -

snemarch Reply

Not just that, it also implemented the XMS spec which gave access to the above-1-megabyte memory. EMM386 did the same, but using the EMS specification (which required using a bank area for copying to/from extended memory, whereas XMS iirc allowed physical access if you went to protected mode). Also, EMM386 set up VM86 mode, which meant some DOS extenders weren't able to load (but it had a way to do it, because Windows needed to be able switch to protected mode even if EMM386 was loaded). Also, throwing in VCPI as a keyword if anybody feels like going on a nostalgia trip.bit_user said:IIRC, what it did was to let you access the 64 kB segment at the top of the address range. That's something even a 286 could do (hence, the logic of including it with Windows 2.1).

The details are a bit hazy, it's been a couple of decades since I messed with DOS related technologies 😅 -

bit_user Reply

DPMI (DOS Protected Mode Interface) was the one which stuck in my head. I thought that's what EMM386 implemented, but I could easily be wrong about that.snemarch said:Also, throwing in VCPI as a keyword if anybody feels like going on a nostalgia trip.

Back in the day, all I really wanted was flat, 32-bit addressing. I had a 386 with 8 MB of RAM, but did all my programming on 16-bit DOS. When I eventually upgraded to Win NT 4.0, it felt so freeing to be able to malloc multiple arrays > 64 kB.