AMD Shares New CPU Core Roadmap, 3nm Zen 5 by 2024, 4th-Gen Infinity Architecture

To Infinity Architecture, and beyond

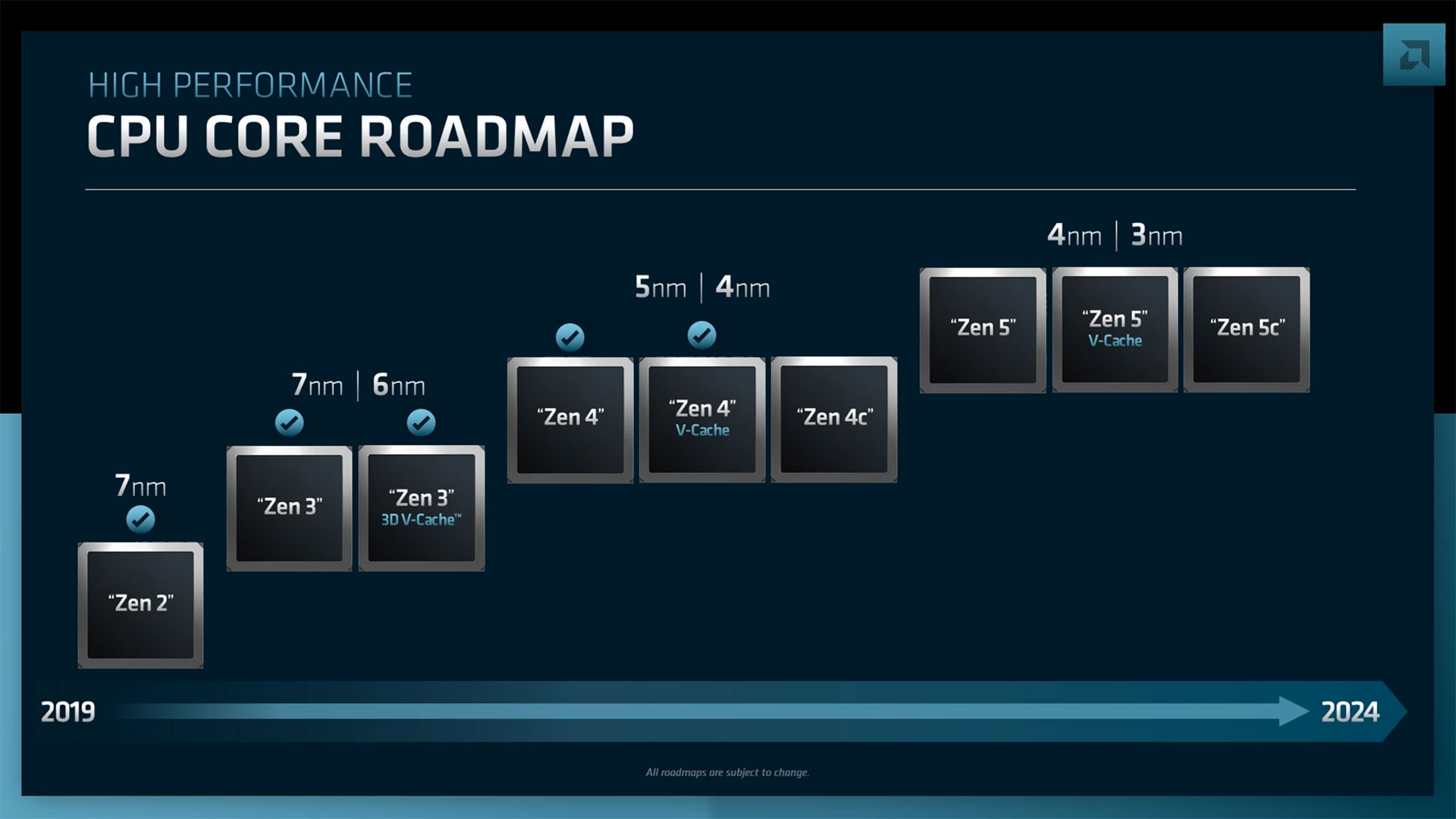

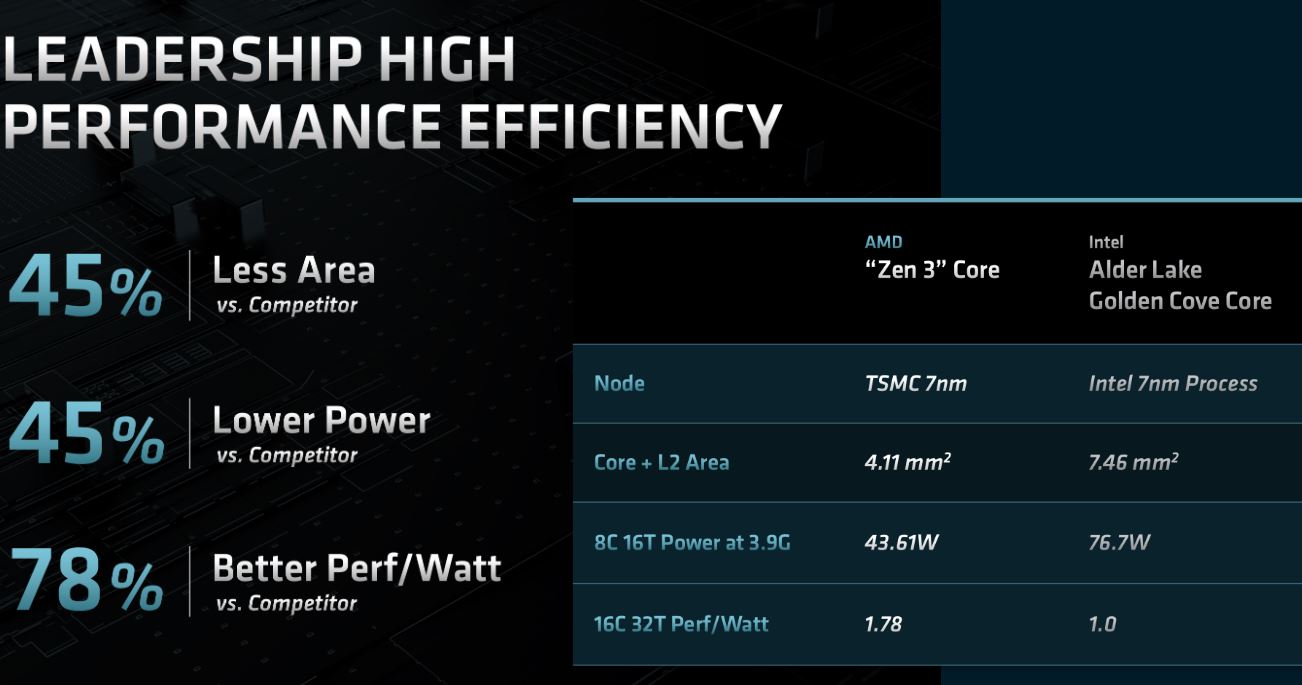

AMD shared a new core roadmap at its Financial Analysts Day 2022, outlining its projected architectural and process node enhancements through 2024. The roadmap includes 5nm and 4nm CPUs based on the Zen 4 architecture, which will include Ryzen 7000 chips, along with 4nm and 3nm processors based on the Zen 5 architecture. In addition, AMD teased some initial details about the 3nm Zen 5 chips that will come to market in 2024 and shared details about the new 4th-gen AMD Infinity Architecture.

- AMD GPU Roadmap: RDNA 3 With 5nm GPU Chiplets Coming This Year

- AMD Zen 4 Ryzen 7000 Has 8–10% IPC Uplift, 35% Overall Performance Gain

- AMD CDNA 3 Roadmap: MI300 APU With 5X Performance/Watt

- AMD’s Data Center Roadmap: EPYC Genoa-X, Siena, and Turin

- AMD Laptop, Desktop Roadmap: Zen 5 Strix Point, Granite Ridge in 2024

AMD CPU Core Roadmap

AMD’s CPU core roadmap isn’t broken into specific years, instead giving us a range from 2019 to the end of 2024. The Zen 4 chips will ship by the end of this year, so we can assume the Zen 4 section of the above roadmap begins in 2022.

Moving forward, AMD’s cores will come in three flavors: The standard cores that are listed merely as ‘Zen 4,’ the 3D V-Cache equipped cores, and ‘Zen 4c’ density-optimized cores. Zen 4 will come in the already-announced 5nm variants, but we’ll also see 4nm cores. These 4nm Zen 4 cores could serve as a broad refresh generation for all chips, or AMD could choose to only use 4nm for certain classes of chips as we see with the 7nm Zen 3 Ryzen desktop PC models and the 6nm Zen 3 Ryzen Mobile processors.

The same rules apply to the Zen 5 cores: AMD has split Zen 5 cores into standard, 3D V-Cache, and ‘ Zen 5c’ variants. The Zen 5 era will debut with a 4nm process, presumably from TSMC, and 3nm variants will also be on offer, though the timing of their arrival isn’t clear. AMD’s CPU roadmap slide ends in 2024, so these cores will debut in 2024.

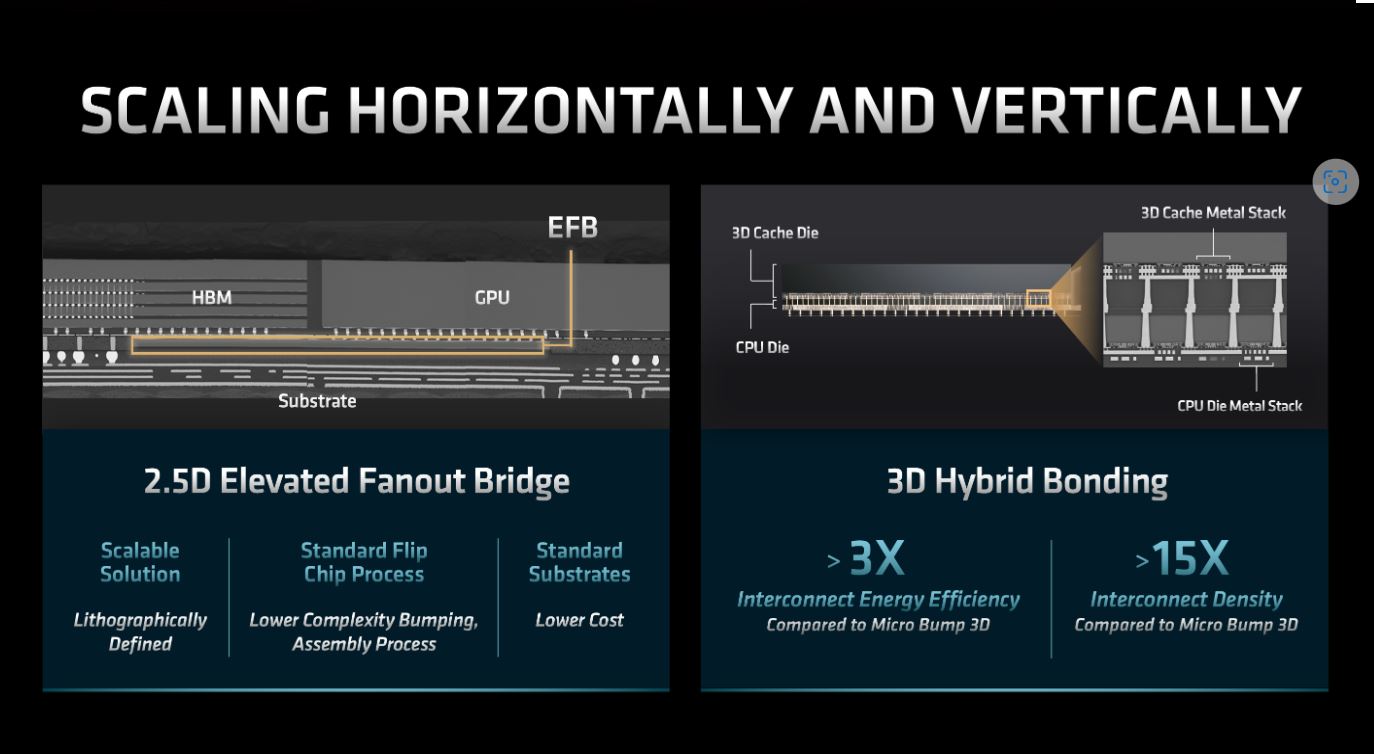

AMD’s Zen 3 cores equipped with 3D V-Cache are already on the market with the Ryzen 7 5800X3D, our current best CPU for gaming, and the Milan-X processors. These chips have a chunk of SRAM melded on top of their compute dies via an innovative hybrid bonding process. AMD says 3D V-Cache chips will become a fixture across its chip families in certain strategic products, but hasn’t committed to any specific number of SKUs for any given family.

The Zen 4c and Zen 5c cores are conceptually similar to the efficiency cores (e-cores) that we see with other types of chip architectures in both Arm and x86 flavors. AMD will use these cores to craft ultra-dense server chips that are optimized for heavily-threaded cloud workloads. AMD also disclosed today that the ‘c’ cores support threading, so the upcoming EPYC Bergamo chips, which feature the Zen 4c cores, will come with an astounding 128 cores and 256 threads.

These 'c' cores are smaller than the standard Zen 4 core that will debut in Genoa, with certain unneeded functionality removed to improve compute density. The chips have a density-optimized cache hierarchy to increase core counts, thus addressing cloud workloads that need higher thread density. This could mean that the chips have a smaller cache(s), or perhaps a cache level has been removed, but AMD hasn't shared details. The Zen 'c' cores support the full Zen 4 ISA — unlike Intel does with Alder Lake, AMD won't disable some features like AVX.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

AMD Zen 5 Architecture

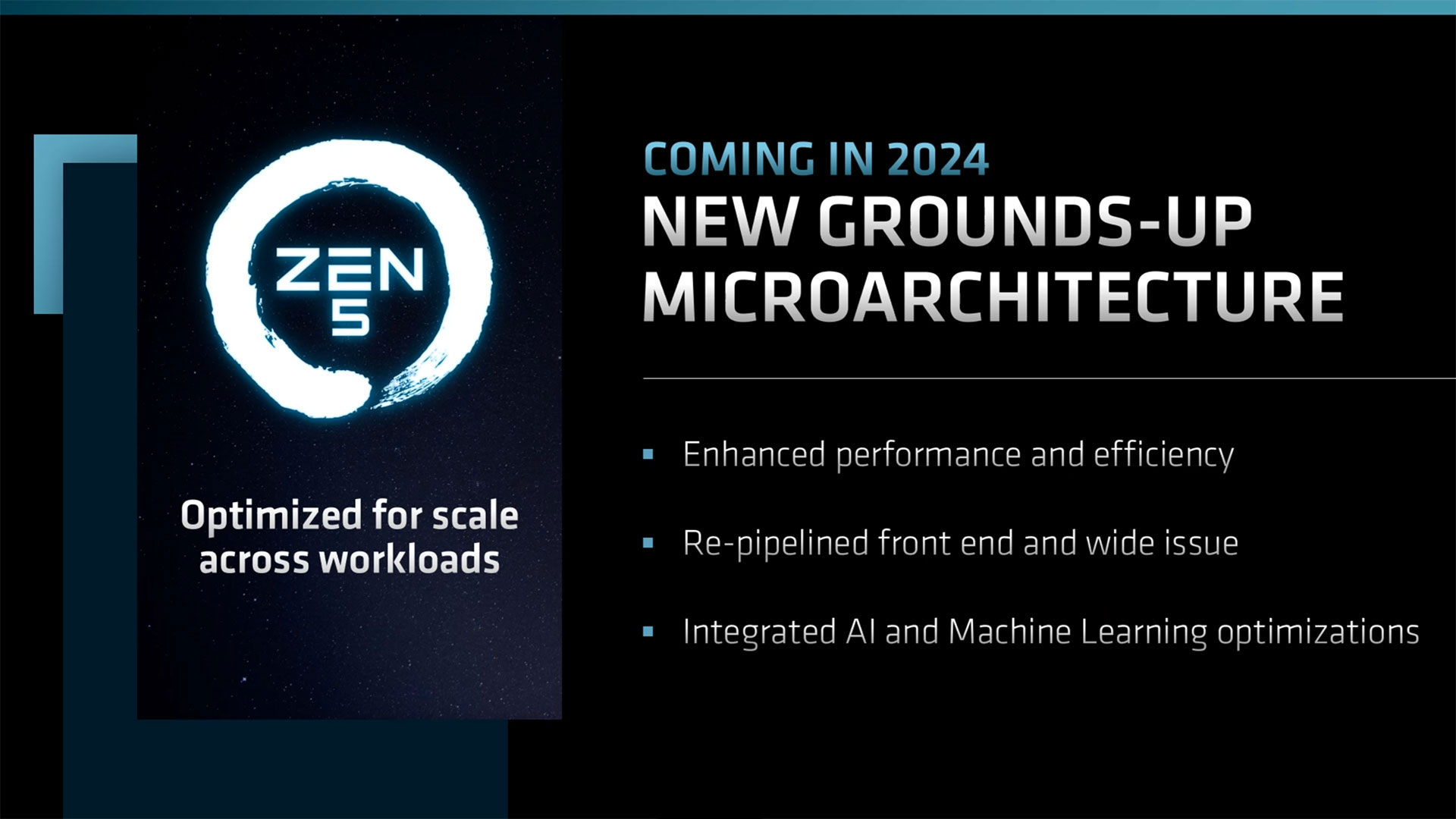

AMD announced that its Zen 5 architecture will come to market in 2024. We can expect a much more significant generational improvement from Zen 5 than we see with Zen 4 due to a new grounds-up redesign of the microarchitecture. As you would expect, AMD targets improved performance and efficiency for the design. AMD says it accomplishes those goals by leveraging a re-pipelined front end and increased issue width.

AMD also points to integrated AI and machine learning optimizations, which could come as hardware support for newer numerical formats or matrix multiply units. As expected, these early details are rather spartan.

AMD’s 4th-Gen Infinity Architecture

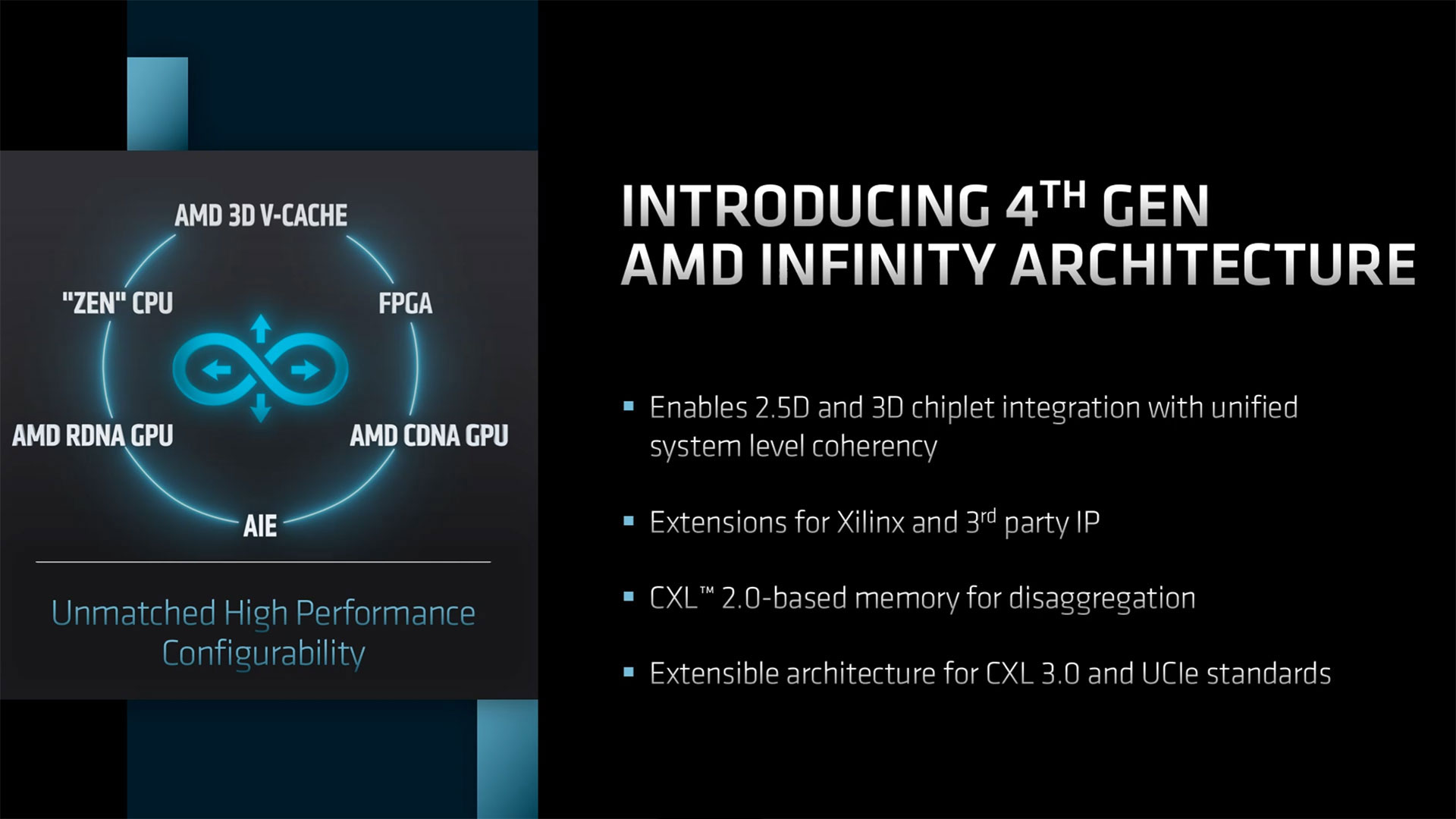

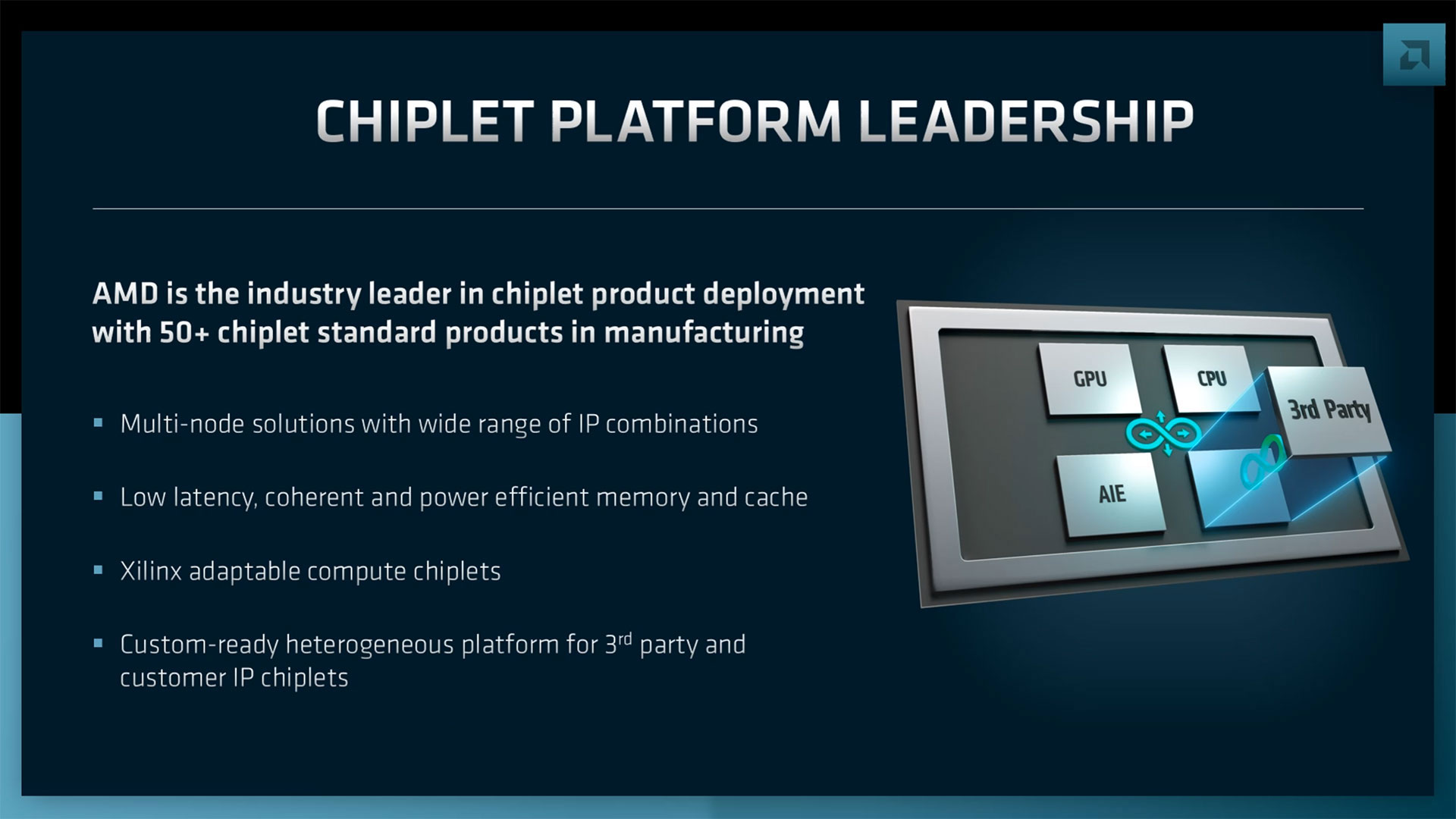

AMD’s early adoption of a chiplet-based architecture was made possible by the Infinity Architecture. This interconnect ties together chiplets, memory and I/O dies, and AMD even uses it to connect accelerators, like its GPUs, for data center applications. The overarching Infinity Architecture is a key component of the company’s chipmaking tool chest, allowing it to tie together chiplets and other components. Now AMD plans to widen the umbrella and add extensions that support the Xilinx IP it recently acquired. AMD will also support IP from third-party vendors, thus giving it access to a wider range of additives.

CXL is an industry-standard cache-coherent interconnect that provides an interface between CPUs and other devices, like GPUs, FPGAs, and memory devices. AMD joined the broadly-supported CXL consortium in 2019, and will now support CXL 2.0-based memory with its 4th-Gen Infinity Architecture. That means we’ll see devices like Samsung’s 512GB CXL Memory Expander supported by AMD processors, probably specifically for the data center. AMD also plans to support CXL 3.0.

AMD also joined the Universal Chiplet Interconnect Express (UCIe) consortium this year. UCIe aims to standardize die-to-die interconnects between chiplets with an open-source design, thus reducing costs and fostering a broader ecosystem of validated chiplets. AMD reiterated its commitment to the UCIe standard for its future Infinity Architecture iterations.

All these tools give AMD the lead in chiplet-based products, with more than 50 products on the market already. The addition of industry-standard interconnects will certainly broaden the company’s scope, particularly when it chooses to integrate chiplets from outside vendors.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.