Mockup of AMD's Zen 4 Raphael CPU Appears With Potential Specs

Hardware leaker ExecutableFix has provided further details on AMD's next-generation Zen 4 processor. This new information comes in hot on the heels of the recent sneak peek at the AM5 socket.

The AM5 socket has been rumored to shift over to a Land Grid Array (LGA) design, meaning the pins are in the socket instead of on the processor. If true, AM5 would mark a turning point in AMD's history. Although AMD utilizes the LGA design for its HEDT (High End Desktop) and server platforms, the chipmaker has never employed the layout on a mainstream consumer platform. It's debatable on whether a LGA design is safer over a Pin Grid Array (PGA) design for the end user. Some might argue that having the pins in the socket means you no longer have to worry about bending the processor pins during installation. On the flipside, it's not unusual for motherboards to arrive with bent pins or cases of users accidentally dropping a processor into the socket and bending the pins in the process.

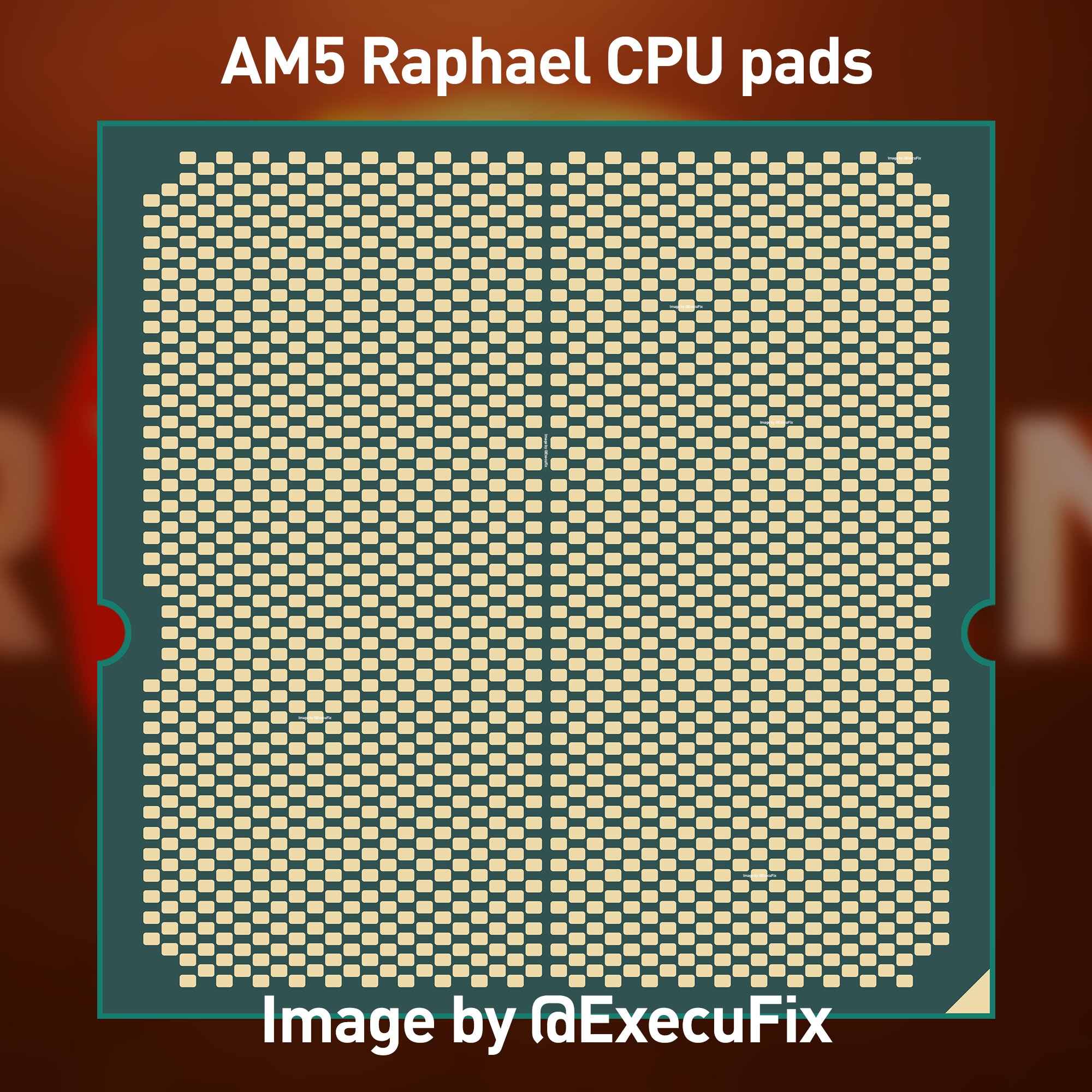

According to ExecutableFix, Zen 4 (presumably Raphael) processors will be the first Ryzen mainstream chips to arrive without pins. The markup of how the processor may look appears intriguing. The leaker previously claimed that Zen 4 will employ the LGA1718 package, so the chip should have 1,718 contacts. Curiously, the contacts appear to be divided into two sections. The layout is similar to AMD's Ryzen Threadripper and EPYC processors. Although we didn't count the contacts, we can assume that each section holds 859 contacts.

Despite the increased pin count, ExecutableFix stated that the AM5 socket measures 40 x 40mm, so it should still be a square shape. What we don't know is that if the AM5 socket will retain the locking mechanism or the mounting holes. At this point, it's anyone's guess whether consumers will need to invest in a new cooler, or if existing cooling solutions are still viable with a mounting converter kit.

AMD Zen 4 Raphael Specifications

| Header Cell - Column 0 | Zen 4* | Alder Lake* | Zen 3 |

|---|---|---|---|

| Codename | Raphael | Alder Lake | Vermeer |

| Branding | Ryzen 6000 | Core 12000-series | Ryzen 5000 |

| Lithography | 5nm | 10nm | 7nm |

| Socket | LGA1718 | LGA1700 | AM4 |

| Maximum Cores | 24 | 16 | 16 |

| Memory Support | DDR5 | DDR5 / DDR4 | DDR4 |

| PCIe Support | PCIe 4.0 x 28 | PCIe 5.0 x 16, PCIe 4.0 x 8 | PCIe 4.0 x 24 |

| Maximum TDP | 170W | ? | 105W |

*Specifications are unconfirmed.

Zen 4 will likely continue to leverage a chiplet design. It wouldn't surprise us one bit if AMD added another core complex die (CCD) to Zen 4 to offer more cores. Zen 3 maxes out at two CCD with eight cores each, which is how the Ryzen 9 5950X got up to 16 cores. An additional CCD would push the core count up to 24, but that is pure speculation for now. However, it would certainly explain the increased TDP (thermal design power) ratings with Zen 4 chips.

If ExecutableFix's information is accurate, the Zen 4 processors could debut with a 120W TDP. There's mention of a special edition 170W SKU, although the leaker didn't provide any details. The extra pins should help improve power delivery as well as increase I/O connectivity.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

As for memory support, Zen 4 will no doubt support DDR5 memory. It seems logical since Intel is already embracing DDR5 with its upcoming 12th Generation Alder Lake processors, and AMD probably doesn't want to be left in the dust. However, Zen 4 doesn't seem to carry over support for DDR4, unlike Alder Lake.

While the rumors still have Zen 4 on the PCIe 4.0 interface, ExecutableFix believes that processors will offer 28 PCIe 4.0 lanes. For comparison, existing Zen 3 chips deliver 24 PCIe 4.0 lanes. It's only a four-lane increase, nevertheless, it should be sufficient enough for motherboard vendors to offer at least some connectivity improvements.

Intel's Alder Lake is due in late 2021 to early 2022. If leaked roadmaps are to be trusted, Zen 4 might not land until the fourth quarter of 2022. In that case, Zen 4 or Ryzen 6000's target will probably be Raptor Lake, which is the rumored successor to Alder Lake.

Zhiye Liu is a news editor, memory reviewer, and SSD tester at Tom’s Hardware. Although he loves everything that’s hardware, he has a soft spot for CPUs, GPUs, and RAM.

-

InvalidError Reply

I'd say that would definitely be within the realm of possible or even expected on 5nm. If not for Zen 4, practically certain for Zen 5.CerianK said:12C/24T chiplets? -

CerianK Reply

I was extrapolating from the table in the article that listed the maximum cores as 24, which only makes sense to me in terms of 2x12 core chiplets.InvalidError said:I'd say that would definitely be within the realm of possible or even expected on 5nm. If not for Zen 4, practically certain for Zen 5.

I guess the question I was really asking is (something like): Where did that '24' figure come from (specific core count leak?) and/or how might it have been inferred from other data (land count or other specs?)? -

InvalidError Reply

3x8 would be feasible too: 5nm chiplets will be smaller, the IOD may also shrink a bit, and the new package will likely have its pinout significantly re-arranged to better accommodate the chiplet-based setup.CerianK said:I was extrapolating from the table in the article that listed the maximum cores as 24, which only makes sense to me in terms of 2x12 core chiplets. -

Kamen Rider Blade I'm thinking that the future will eventually have:Reply

_4x Core CCX dies

_6x Core CCX dies

_8x Core CCX dies

12x Core CCX dies

All, using the same Core designs of course.

This way AMD can Mix & Match to get up to 12x Cores per CCD.

Having 4x CCX dies of varying core counts will allow AMD to create CCD's ranging from 4-12 Core CCD's based on pairings and offer a wider, more fine tuned range of Cores for all segments (Budget/Consumer/Prosumer/Enthusiast/Enterprise).

And given how good the yields are, only having to disable 1-2x Cores because of Yield reasons makes sense IMO.

I also don't see AMD moving past 2 CCD's for the consumer end.

Any CPU with higher CCD count would go towards a new higher tier of CPU.

Personally, I think ThreadRipper will be the High End for Consumer and AMD should launch a new Mid Tier platform.

I wouldn't be surprised if they brought back the FX line and made that a mid tier CPU platform. -

InvalidError Reply

The 8-cores CCDs on 7nm are only 81mmsq in size and that is probably close to about as small as you can go before wasting a disproportionately large amount of wafer space on cutting lines between dies. You also need chips to be of a certain minimum size to fit all of the power and IO balls under them. Going any lower than 8-cores per CCD wouldn't make much sense. Going up to 12 cores however would keep CCD size around 80mmsq and allow AMD to keep practically the same substrate layouts it got used to with Zen 2&3.Kamen Rider Blade said:Having 4x CCX dies of varying core counts will allow AMD to create CCD's ranging from 4-12 Core CCD's -

hotaru.hino Plot twist, it's a 4x6 configuration instead (from defective 8-core CCXes) , especially if they shrink the I/O die since I believe the current ones are still 14nm. If they drop it to 7nm, which at this point is mature, that could provide enough room to make a baby Threadripper/EPYC. Though the 2x12 configuration would make the most sense. It's not like core counts have to be natively a power of 2.Reply

A 3 chiplet configuration I can't picture because of the problem trying to make the dies equidistant from the I/O die to ensure equal latency without doing something dumb-sounding like lengthening the traces for the other two chiplets. -

Kamen Rider Blade Reply

AMD still needs to cater to lower Core Markets / Budget markets.InvalidError said:The 8-cores CCDs on 7nm are only 81mmsq in size and that is probably close to about as small as you can go before wasting a disproportionately large amount of wafer space on cutting lines between dies. You also need chips to be of a certain minimum size to fit all of the power and IO balls under them. Going any lower than 8-cores per CCD wouldn't make much sense. Going up to 12 cores however would keep CCD size around 80mmsq and allow AMD to keep practically the same substrate layouts it got used to with Zen 2&3.

Making a new Die Mask for 4x Core & 6x Core CCX's makes sense.

Especially as yields for 8-cores are getting better over time.

The PCB Substrate is a seperate issue from the Polymer CCD package that holds the CCX's. -

InvalidError Reply

They can have APUs for that.Kamen Rider Blade said:AMD still needs to cater to lower Core Markets / Budget markets.

Making a new Die Mask for 4x Core & 6x Core CCX's makes sense. -

Kamen Rider Blade Reply

Given the lack of yields on APU's and the entire Mobile Market needs APU's on top of DeskTop APU's.InvalidError said:They can have APUs for that.

I don't see that happening any time soon.

I can't see AMD giving up on 4/6 core low end Ryzens anytime in the future, especially since Intel is in that market competing for the DeskTop market.

And DeskTop APU's are a seperate market that is going to need it's own MoBo types, which will eventually happen.