Lunar Lake MX will be Intel's first high-performance CPU to use outsourced TSMC node for x86 cores — reportedly uses N3B process

All in on IDM 2.0.

Intel's x86 chips are now forging into new territory — leaked slides published by prominent hardware leaker @YuuKi_AnS (yet quickly removed) indicate that the compute tile of the Lunar Lake MX processors will be made using TSMC's N3B fabrication technology, marking the first time Intel has used outsourced process node tech for its highest-end x86 cores. Intel's Lunar Lake processors are set to feature an all-new microarchitecture designed from the ground up to offer breakthrough performance-per-watt efficiency, primarily for mobile devices, but it is unclear how old the slides are — these could reflect an older plan for the series.

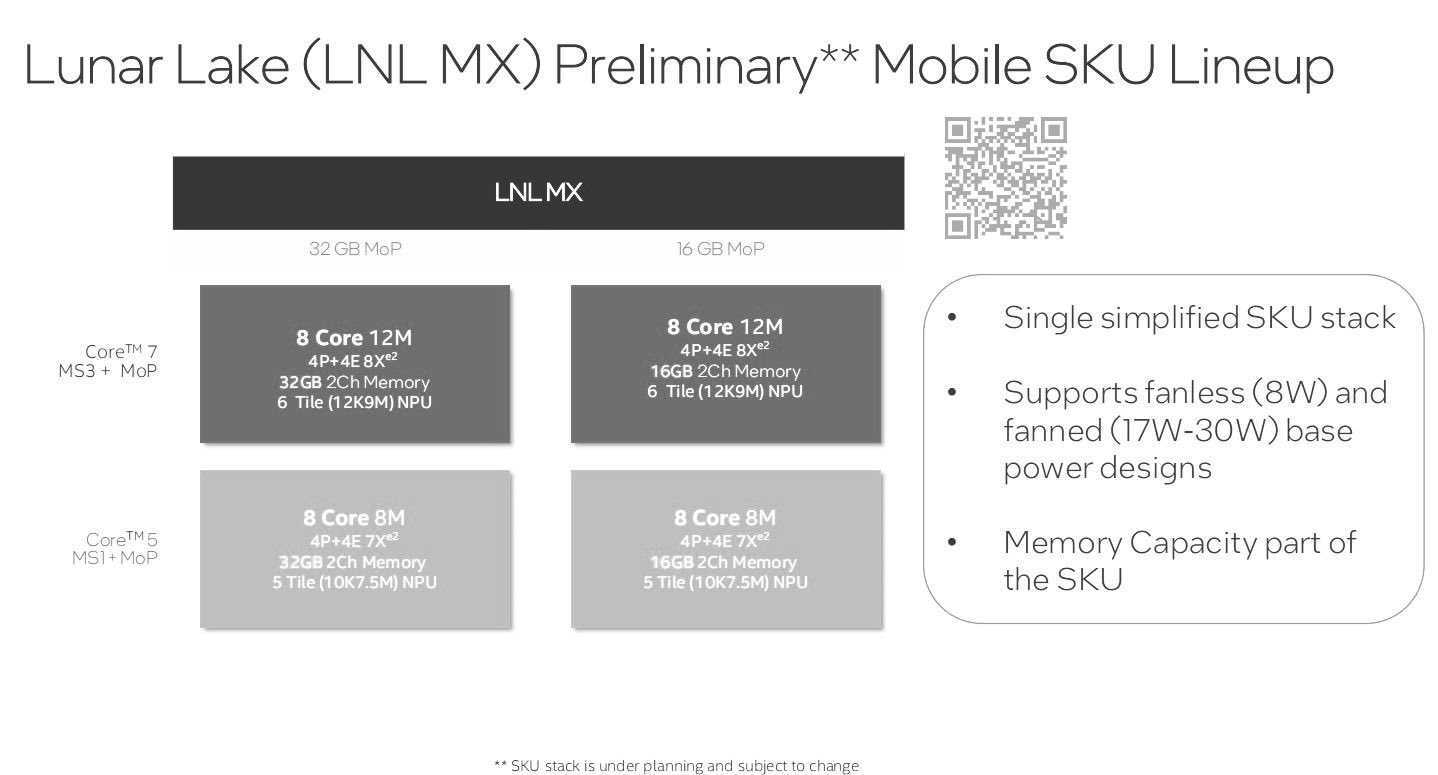

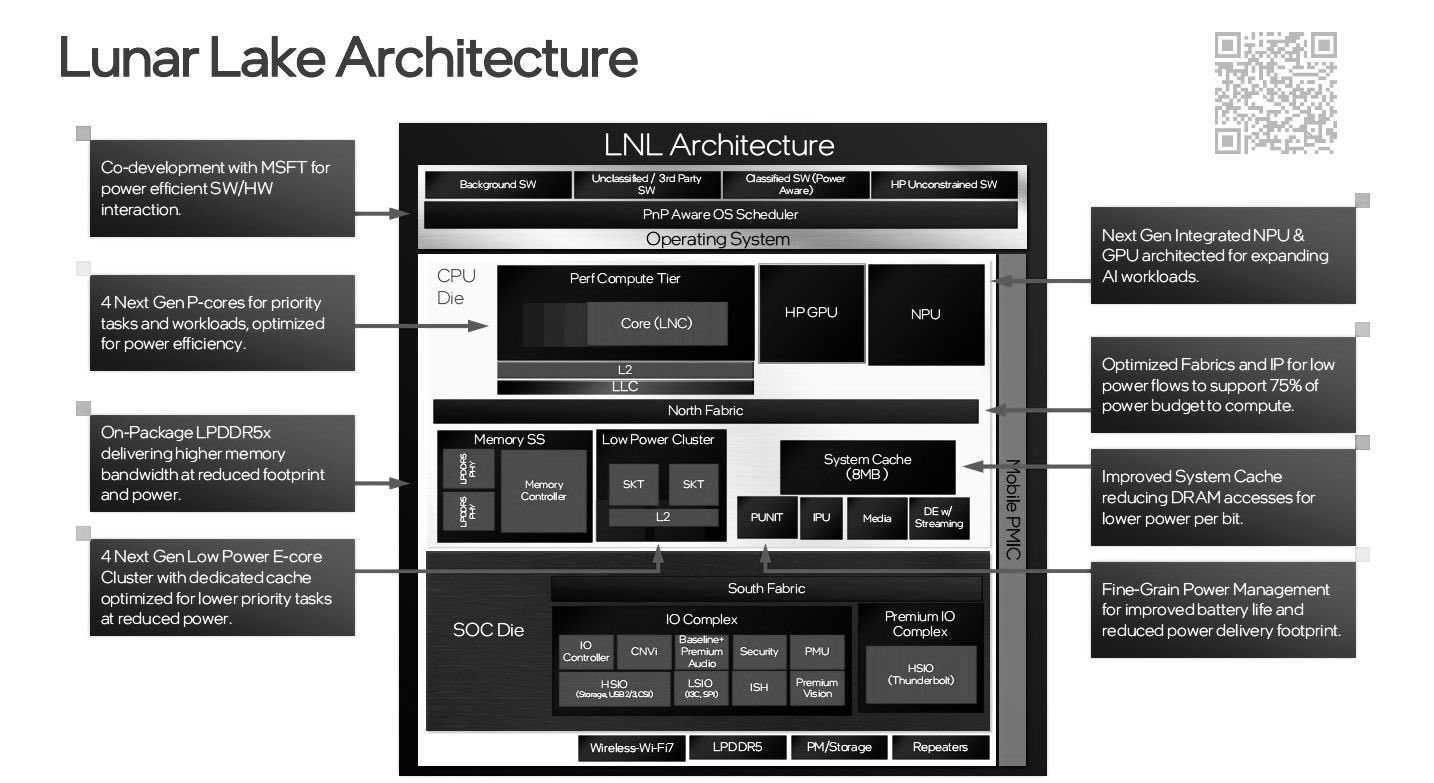

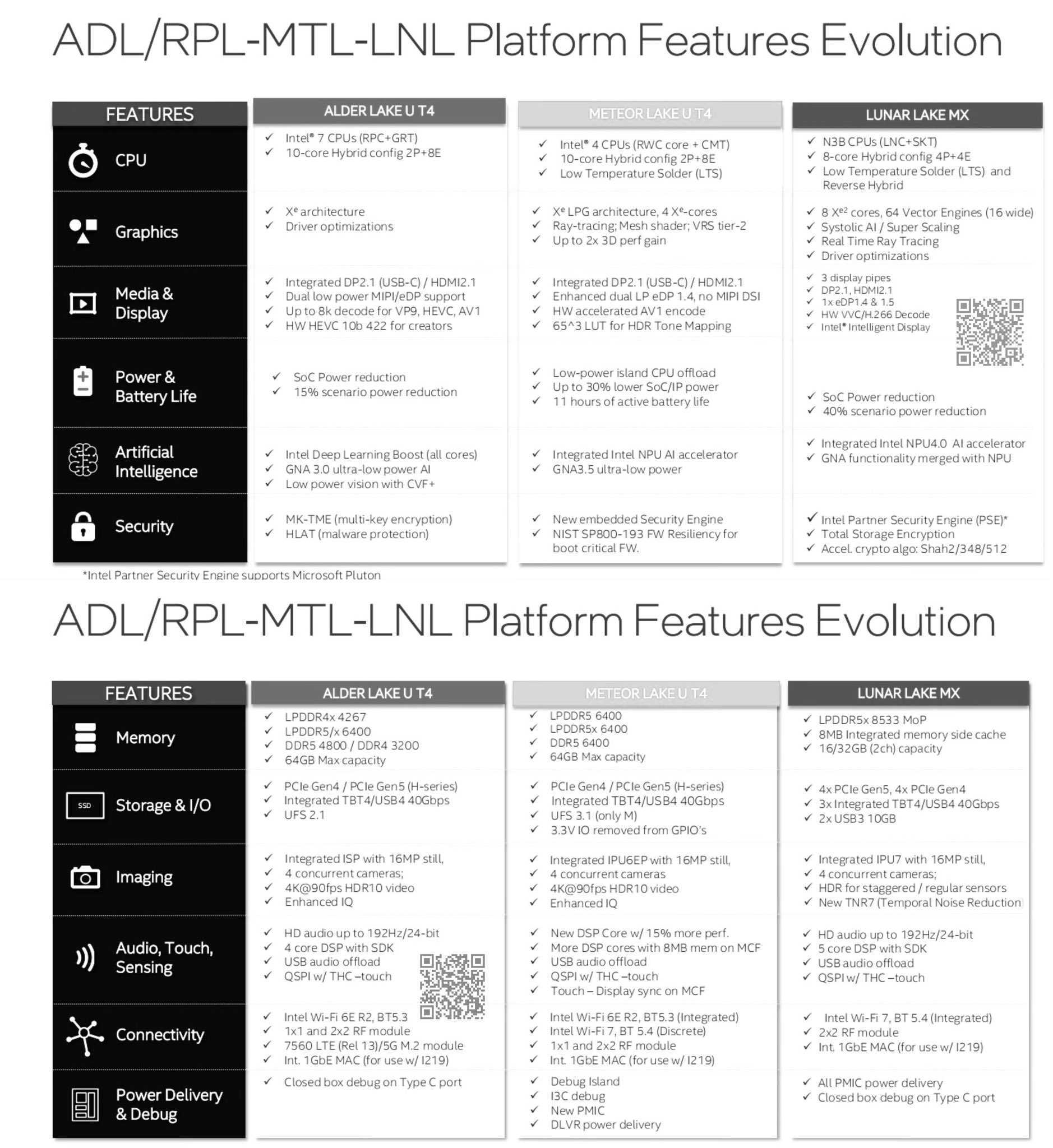

According to the slides, Intel's Lunar Lake MX platform lineup will offer processors with up to eight general-purpose cores (four high-performance Lion Cove and four Skymont energy-efficient cores), 12MB cache, up to eight Xe2 GPU clusters, and up to a six-tile NPU 4.0 AI accelerator. Depending on the power target, the platform will support 8W fanless as well as 17W – 30W fanned designs.

The compute tile will purportedly be produced on TSMC's 3nm-class N3B process technology. Meanwhile, Intel itself indicated that its Lunar Lake CPUs will use its own 18A (1.8nm-class) fabrication process.

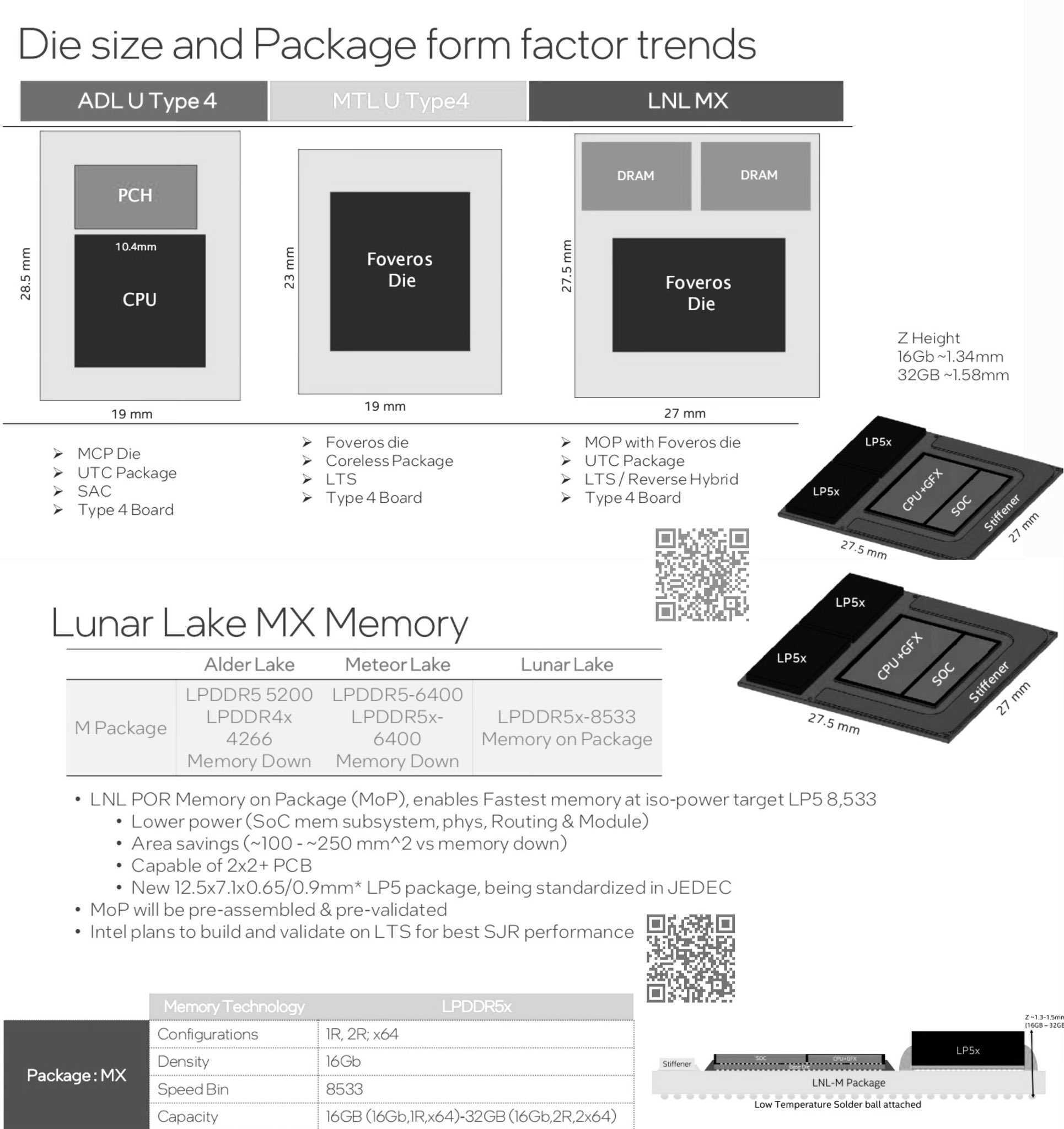

Intel's Lunar Lake MX platform will retain Intel's multi-chiplet Foveros3D-interconnected design approach. Still, to reduce its physical footprint, Intel plans to pack the CPU, GPU, and memory controller into the same tile while putting everything else into the SoC tile, according to the slides.

In addition, Intel's Lunar Lake MX is aimed primarily at laptops, and it is set to come with 16GB or 32GB of LPDDR5X-8533 memory-on-package, which will further reduce the platform's footprint and improve performance.

Based on Intel's estimates presented in the slides, its Lunar Lake MX design will save 100 to 250mm^2 of space compared to typical designs with memory outside the CPU package.

While it is odd to see Intel using TSMC's N3B process technology to build its Lunar Lake MX processors, it is not completely unexpected. Since the company wants to put CPU and GPU cores into the same piece of silicon, it might just make more sense to build everything on TSMC's N3B because GPUs tend to be bigger than CPUs and re-architecting Xe2 GPU for Intel's 18A node could take more time than the company would like to spend on its low-power mobile processor.

Nonetheless, this is the first time Intel will use a third-party process technology for one of its flagship CPUs, highlighting the flexibility of its IDM 2.0 approach to design and manufacturing.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

thisisaname Apple has all of TSMC's 3nm production? so where and when are these being produced?Reply -

TerryLaze What exactly in these slide is supposed to show that intel will use tsmc n3b for the mx compute tiles?! Am I just blind?! Can somebody point it out?Reply -

NinoPino The "High performance" of the title and the "mobile" in the article sounds strange.Reply

Most notable, the fact that Intel use TSMC N3P instead of the superior-multi-pluri-acclamed Intel 18A seems to implicitly means that TSMC is better on efficency, or that Intel have problems with future nodes. -

kwohlt Reply

No, just that LNL is a 2024 product and 18A is a 2025 node.NinoPino said:The "High performance" of the title and the "mobile" in the article sounds strange.

Most notable, the fact that Intel use TSMC N3P instead of the superior-multi-pluri-acclamed Intel 18A seems to implicitly means that TSMC is better on efficency, or that Intel have problems with future nodes. -

rluker5 Reply

Under the Lunar Lake MX section of the first slide "N3B CPUs (LNC + SKT)"TerryLaze said:What exactly in these slide is supposed to show that intel will use tsmc n3b for the mx compute tiles?! Am I just blind?! Can somebody point it out?

I'm assuming that the LNC and SKT are the same as in the 3rd of 4 slides below that where the LNC is labeled with the high performance cores and SKT is labeled with the e-cores.

This, and the Intel quote of 18A for Lunar Lake could be resolved by TSMC making the lower clocking, more efficient low power CPUs and Intel making the higher powered, higher performance ones.

It is also coming with Pluton. I knew that day would come eventually. MTL might even have it as their "new embedded security engine" sounds a lot like the "intel partner security engine".

On the plus side it does seem better synced with the OS for better thread management and the power claims are getting ridiculous. And the iGPU is as well. -

JamesJones44 Reply

Apple's deal saw them book 90% of the N3 capacity till the end of the year. If this is going to be produced next year, access to the N3 nodes should not be an issue.thisisaname said:Apple has all of TSMC's 3nm production? so where and when are these being produced? -

thestryker Reply

Given the timing of LNL, the leaks and the way Intel has been referring to it I'm not sure there's going to be a high performance version. It should be using the same p-cores as ARL and likely the same e-cores as well (though there are competing leaks on this). It seems like Intel will be splitting low power and high power which makes sense if they're going to do more on package with low power.rluker5 said:This, and the Intel quote of 18A for Lunar Lake could be resolved by TSMC making the lower clocking, more efficient low power CPUs and Intel making the higher powered, higher performance ones. -

DavidC1 Reply

No.NinoPino said:The "High performance" of the title and the "mobile" in the article sounds strange.

Most notable, the fact that Intel use TSMC N3P instead of the superior-multi-pluri-acclamed Intel 18A seems to implicitly means that TSMC is better on efficency, or that Intel have problems with future nodes.

Intel won't use Intel 3 because servers will take up all the wafers, and even if they have some left over, N3 is better for lower power. 20A can't be used because 20A is just like Intel 4 in that it doesn't have all the libraries necessary for I/O and SoC tiles, so they can't use that. 18A can't be used since Lunar Lake is coming this year and is way too late.

Arrowlake can use 20A because it'll have a different tile configuration, similar to Meteorlake and can use Intel process just like Meteorlake does. There's no doom and gloom anywhere here.

This is so Intel can de-couple process from design which means process won't hinder design and design won't hinder process. At this point process team is better and design team is questionable, but it is what it is. -

cyrusfox This is a fascinating leak, really interested to see how cpu performs Internal produced vs external. Should lunar be compared against Meteor or Arrow though? And when will we see it launched? Meteor is landing in December, Arrow sometime next year.Reply