Micron Preps 32Gb DDR5 Chips, Opens Door to 1TB Modules

32GB DDR5 DRAM ICs incoming.

Micron was the first company to introduce 24Gb DDR5 memory devices as well as start shipping actual modules on their base last fall. As it turns out, as part of Micron's HBM3 Gen2 announcement, the company wants to maintain the lead and is prepping to mass produce 32Gb DDR5 ICs as well high-capacity memory modules in the first half of 2024, the company revealed today.

Micron's monolithic 32Gb DDR5 IC will be made on Micron's 1β (1-beta) fabrication technology, which is the company's most advanced production node and also the last fabrication process that does not use extreme ultraviolet lithography. For now, Micron has not disclosed the data transfer rates it expects from its 32Gb devices, though given the fact that these will be Micron's 3rd Generation DDR5 ICs, expect them to be reasonably fast.

One of the things that modern DRAM fabrication technologies allow memory makers to do is to build high-capacity monolithic memory devices. After Micron built its 24Gb memory IC on its 1α (1-alpha) process technology last year, it was logical for the company to proceed with a 32Gb device with its 1β node and this is exactly what it is doing.

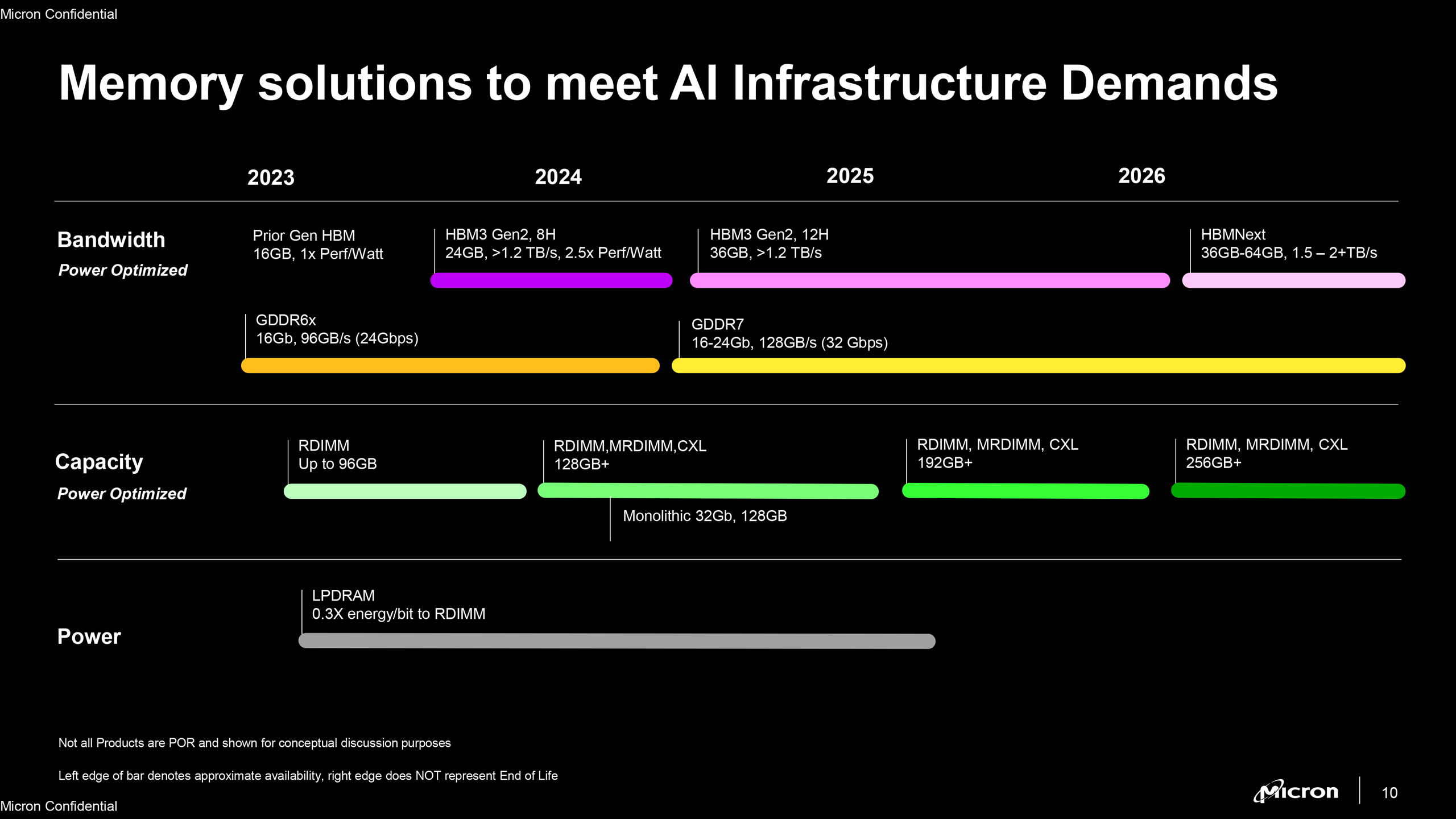

32Gb DDR5 DRAM ICs will be particularly useful for datacenter-grade memory modules as they obviously benefit from high-capacity DRAMs. But while 32Gb devices open doors to 1TB DDR5 modules (which use 32 8-Hi 32Gb stacks), Micron is not jumping the gun here and will only offer 128GB DDR5 modules based on these ICs next year. Going forward the company plans 192GB and 256GB DDR5 modules.

Meanwhile, 512GB and 1TB memory sticks are not currently listed in the roadmap, possibly because Micron still considers such memory sticks as niche devices that it might make available for select clients.

Speaking of niche types of memory products: Micron's roadmap published on Wednesday reiterates Micron's plans to mass-produce 16Gb and 24Gb GDDR7 memory chips with a 32 GT/s data transfer rates sometimes in mid-2024 as well as HBMNext memory in 36GB and 64GB stacks offering 1.5TB/s 2+ TB/s bandwidth per module sometime in 2026 or later.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

HideOut They are showing a picture of a chart regarding the HBM3+ stuff, for ddr5 RAM sticks. OoppppsReply -

Geef Calculations: 1Gb = 125MBReply

So 32Gb would equal 4GB.

If Micron is just now coming up with 4GB memory sticks I think they might be a little behind the curve.

:ROFLMAO: -

thestryker Reply

You don't seem to understand that it's referring to the individual memory chips on the memory sticks. At the client level 32GB of DDR5 has 16 individual chips because they're 16Gb, 48GB also has 16 chips because they're 24Gb so this would allow for 64GB with the same number of chips. In theory this would allow client devices to have 256GB maximum DRAM capacity.Geef said:Calculations: 1Gb = 125MB

So 32Gb would equal 4GB.

If Micron is just now coming up with 4GB memory sticks I think they might be a little behind the curve.

:ROFLMAO: -

Hotrod2go Great they can pack more density into an IC chip is what this tells me. Opening the door to bigger capacity UDIMMs for DDR5.Reply

There OC potential will be limited though compared to bigger die manufacturers (at present). -

dk382 24Gb GDDR7 is the real story here, in my opinion. The excuse Nvidia and AMD roll out for why the 4060 and 7600 can't be more than 8GB is that they have 128-bit busses. With 24Gb modules, they'd be able to do 12GB on 128 bits. Or 16GB on 192 bits. Ideally, they get their heads out of their rears and increase the bus width of low-end and midrange parts, but the option to have 24Gb modules is quite nice as well.Reply -

Kamen Rider Blade ReplyGoing forward the company plans 192GB and 256GB DDR5 modules.

@ 4 GiB DDR5 DRAM Packages

192 GiB = 1⅓H.3R.2S DIMMs

256 GiB = 1⅔H.4R.2S DIMMS

Perfect for Enterprise Server racks where 3 Row and 4 Row DIMMs would make sense.

A friend of mine has been eagerly waiting for 128GB DDR5 DIMM Modules.

So the fact that they're coming next year, his personal Rendering Station will be very happy. -

bit_user Reply

Apart from anything else, you can also just look at the slide.usertests said:I think you mean 32 Gb, not 32 GB.

Fair point: they should've said Gib, which is equivalent to 128 MiBGeef said:Calculations: 1Gb = 125MB

When talking about networking speeds or disk capacity, we usually mean G (i.e. 10^9). When talking about RAM, we usually mean Gi (i.e. 2^30).

Yes, and the article also talks about 8-high stacking, which just confirms the 32 Gb figure is referring to a single 2D die.thestryker said:You don't seem to understand that it's referring to the individual memory chips on the memory sticks. At the client level 32GB of DDR5 has 16 individual chips because they're 16Gb, 48GB also has 16 chips because they're 24Gb so this would allow for 64GB with the same number of chips. In theory this would allow client devices to have 256GB maximum DRAM capacity.

"32Gb devices open doors to 1TB DDR5 modules (which use 32 8-Hi 32Gb stacks)"

32 Gib/die * 8 dies/stack * 32 stacks/module = 8192 Gib/module

8192 Gib/module / 8 bits per Byte = 1024 GiB/module

That's where the headline figure of 1 TiB/module comes from. -

bit_user Reply

With 32 Gib dies, the max UDIMM size will probably be just 64 GiB. That's because I think UDIMMs are limited to dual-rank, which I believe limits you to 16 chips. Stacking the dies probably pushes past the point where you need registers (i.e. RDIMMs).mikewinddale said:128 GB UDIMMs or RDIMMs?