Router SoC 101

Do you ever wonder what goes on inside a router? In this article, we take a close look at the SoCs inside of them, which help us manage and maintain our connected lives.

Processors And Transceivers

The Processor

Any host processor can, theoretically, act as a networking processor, but the hardware in commercial routers is optimized to handle very specific networking tasks. These include key look-up (database look-up using a key), computation, data bit-field manipulation, queue management, pattern matching and control processing. A GPU, for example, would yield less-than-optimal results as the brains of a router (though the reverse problem, gaming on a networking processor, would run up against fundamental limits pretty quickly).

Before HD (or 4K) streaming video, multiple devices communicating over the same home network or intensive network gaming, wasting a multi-core processor on routing tasks was unheard of, even in the prosumer segment. Clearly, this has changed. Processor performance, especially on older routers, can bottleneck the bandwidth of ISPs serving gigabit-class Internet.

Beyond cores and clock rates, CPU specifications can quickly become mind-numbing. But in the networking world, they can generally be split into their instruction set architectures (ISAs): ARM and MIPS.

Article continues belowOf course, there are other architectures other than ARM and MIPS used in networking devices. These are usually dedicated co-processors like DSPs, cryptographic processors, media accelerators and so on.

ARM

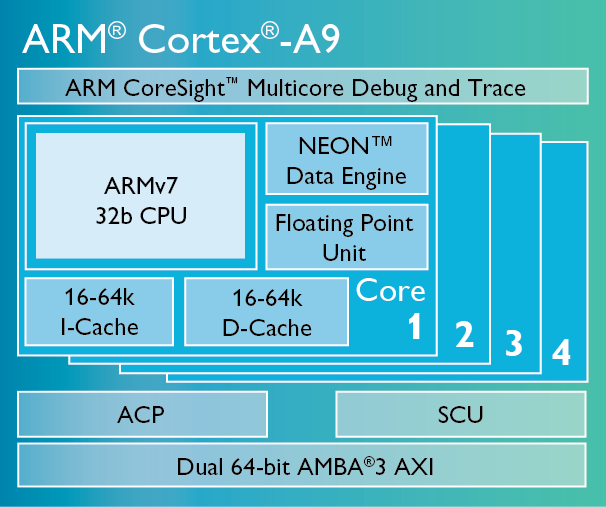

ARM Cortex-A refers to a series of microprocessors designed by ARM Holdings PLC. The company doesn't manufacture the hardware, but instead licenses its designs. The suffix "A" stands for "applications," hinting that the A series is meant for general-purpose use. There are also "M" (for microcontroller) and "R" (for real-time) families.

The implementations most commonly found in modern networking devices are the older Cortex-A9 or Cortex-A5 chips. Both are based on the 32-bit ARMv7 architecture.

The Cortex-A9 was introduced in 2007. It features L1 instruction and data caches that can be configured independently to 16, 32 or 64KB; up to 8MB of L2 cache and clock rates as high as 2GHz. Cortex-A9 processors are included in many current SoCs, including the Apple A5 and A5X; Broadcom BCM11311; Nvidia Tegra 2, 3 and 4i; and even Sony's PlayStation Vita.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

The Cortex-A5 hit the market in 2009 as a less powerful alternative to the A9 for low-end and mid-range consumer devices. It's available with between one and four cores, and includes from 4KB to 64KB of L1 instruction/data cache. It is used on many transceiver SoCs.

MIPS

The MIPS architecture (short for microprocessor without interlocked pipeline stages) was introduced in 1981 by John L. Hennessy of Stanford University. It is currently developed by MIPS Technologies, which has been part of the UK-based Imagination Technologies group since 2013. MIPS uses a reduced instruction set computer (RISC) architecture, enabling specialized chips with low power consumption that are widely used in embedded systems for routers. There are two instruction set versions currently in use: the 32-bit MIPS32 and 64-bit MIPS64. Both were introduced in 1999.

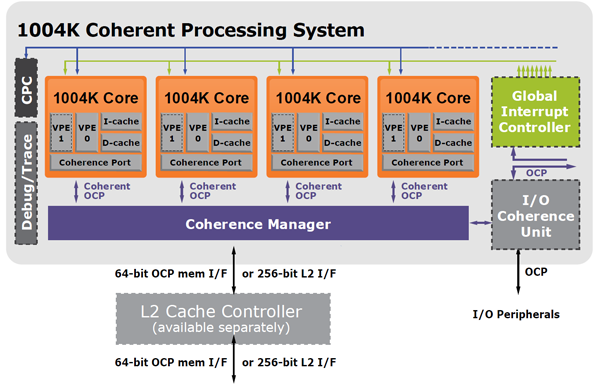

MIPS32 is used in various microarchitecture families—namely, 4K/E, 24K/E, 34K, 74K, 1004K, 1074K/f, microAptiv, interAptiv and proAptiv. The latter three are the most current, introduced in 2012.

The microAptiv, interAptiv and proAptiv microarchitectures typically come with 32x 32-bit general-purpose registers (up to 64x are allowed). The architecture allows for up to 8MB L2 cache, and current implementations operate at frequencies as high as 1.5GHz. MIPS32 is meant to be upward-compatible with MIPS64, which means its features are supposed to be a subset of what MIPS64 offers. Both utilize fixed-length commands in a three-operand format and a load/store data model, catering to high-level programming languages.

Chips based on MIP32 include Broadcom's BMIPS3000, BMIPS4000 and BMIPS 5000; BCM53001 and BCM1255; Ingenic Semiconductor XBurst 1; and Baikal Electronics P5600. Chips using the 64-bit MIP64 architecture include Broadcom's BCM1125H and BCM1255; the Cavium octa-core processors CN30xx, CN31xx, CN36xx and CN38xx; Octeon Plus: CN5xxx, Octeon II: CN6xxx, and Octeon III: CN7xxx; Ingenic Semiconductor XBurst 2, NEC VR4305 and VR4310.

Transceivers

A transceiver is a device that combines a data transmitter and receiver in a single package. Most commercial routers have transceivers with integrated radio/antenna systems, and most often, a small controller or dedicated chip on the board handles radio functions. While "transceivers" are most commonly associated with radio frequency (RF) signals, they have analogs in other transmission standards, though few (if any) of these analogs will be seen in a commercial router for home/small-business use. The Ethernet versions of transceivers are MAUs (medium attachment units), while fiber and 10GbE have their own set of acronyms (GBIC, XAUI, etc.) to describe transceiver devices.

Although the trend toward complete SoC solutions continues unabated, many new devices tend to take the transceiver plus processor card approach. Ensuring backward compatibility with older 802.11b/g/n networks—and avoiding a complete redesign with a router refresh, where new functionality can be thrown in just by adding another card—is a big factor. It should also be noted that many packages called "SoCs" omit the actual transmission-receipt function, instead providing a PCI/PCIe slot for the router manufacturer to fill with a network card.

Current page: Processors And Transceivers

Prev Page Router SoC Functional Components Next Page Chipsets-

bwhiten Uhhhh...Those first pictures are not "schematics". They are CAD renderings of the box and main board at best, but definitely not schematics.Reply -

EdJulio ReplyUhhhh...Those first pictures are not "schematics". They are CAD renderings of the box and main board at best, but definitely not schematics.

Thanks, bwhiten. Updated the caption...

-

bit_user Nice article!Reply

Small, irrelevant fact: MIPS was once owned by SGI and used in their servers and workstations. They even used a MIPS CPU in the N64, which they designed for Nintendo. In fact, that was largely the outcome of a previous (if not the first) wave of VR hype. But, I digress...

Also, most people consider ARM to be RISC. Or, at least as much as anything is, these days. Indeed, the name once stood for Advanced RISC Machines.

But I didn't know what MIPS originally stood for, so thanks for that. I wonder whether or how long that remained true of their architectures. -

EdJulio Reply17548227 said:Nice article!

Small, irrelevant fact: MIPS was once owned by SGI and used in their servers and workstations. They even used a MIPS CPU in the N64, which they designed for Nintendo. In fact, that was largely the outcome of a previous (if not the first) wave of VR hype. But, I digress...

Also, most people consider ARM to be RISC. Or, at least as much as anything is, these days.

Thanks! I'll share this with Gene! Cheers!!! -

bit_user Reply

Thanks, but I did say it was irrelevant. It really has no bearing on the routers using these chips.17548234 said:Thanks! I'll share this with Gene! Cheers!!! -

GeneFabron ReplyNice article, is there any more on how tech works? Like cpu and gpu?

Hi QuangT, we have a Wireless Routers 101 http://www.tomshardware.com/reviews/wireless-routers-101,4456.html and a PSUs 101 http://www.tomshardware.com/reviews/power-supplies-101,4193.html article, and there will be more coming soon! -

Gabriel_1965 Question: I've seen a router with 72 cores would that be made to be a 72 core pic and I could use the cores for multi ore computing?Reply