Extreme Overclocking: 10 Ryzen CPUs Under LN2

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Preparing The RAM

During our first extreme overclocking sessions, we didn't put much effort into preparing the memory. We simply installed the modules into slots with their factory heat sinks in place. This strategy didn't work all that well, as we had to stop our tests multiple times when the hardware refused to start up. Although we can't say for sure, it's likely that humidity around the memory stick closest to the pot was responsible for these failures.

After drying the hardware, everything worked once again. And since this happened more than once, removing the RAM sinks just seemed like a prudent idea.

If you choose to follow suit, be careful: some heat spreaders are so firmly attached to the memory chips that they can pull ICs right off the PCB. To improve our chance of success, we warmed the module up first. Even then, it took a lot of effort to achieve our goal.

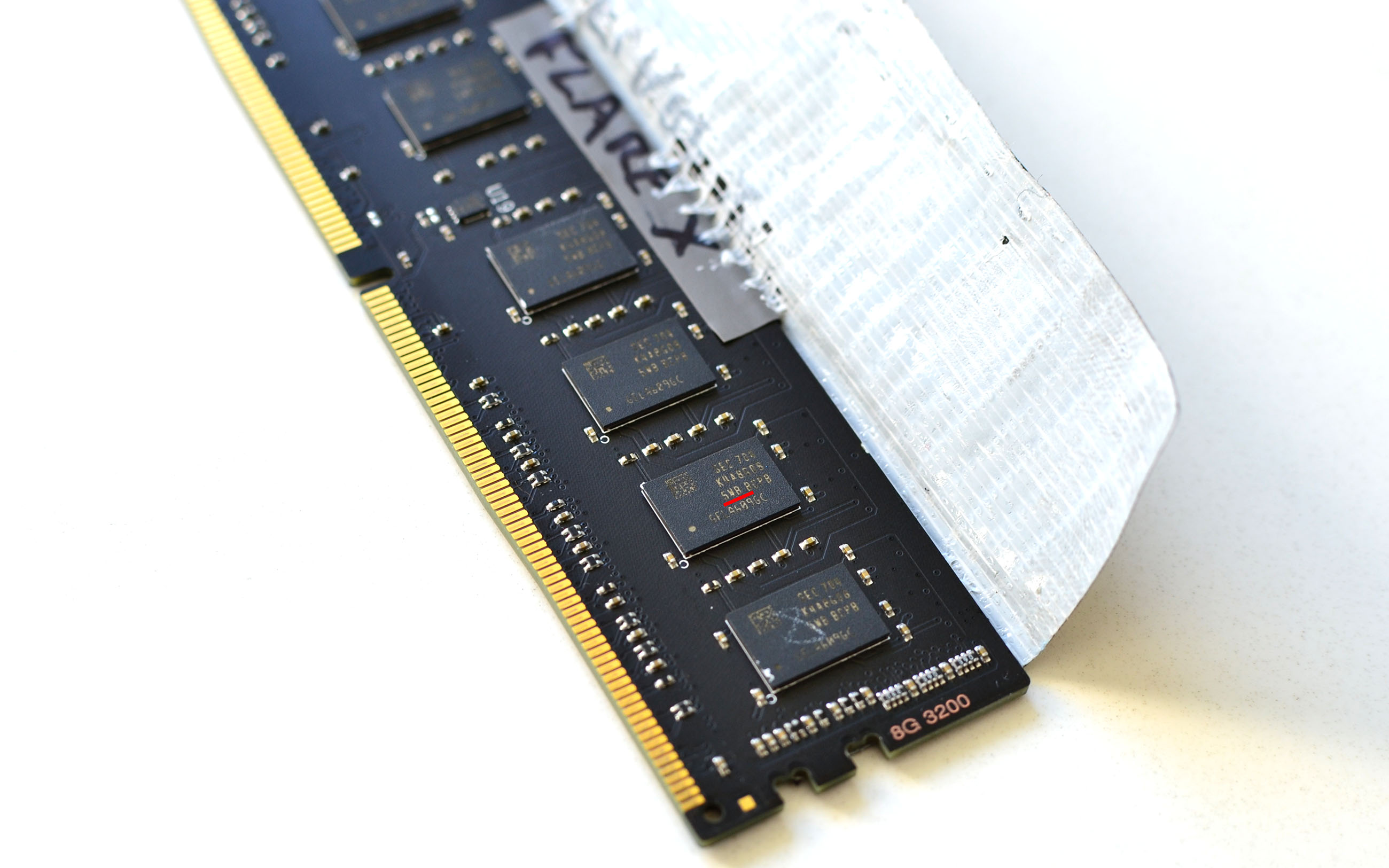

Article continues belowBefore masking off the chips, we take advantage of their exposure to verify that our sticks are endowed with Samsung B-die memory. Without question, they're the best for overclocking.

The type of the IC is indicated on the chip, just above the red line we drew, “5WB”. If these were E-die chips, we'd see 5WE, or 5WD for D-die. Other manufacturers use different identification marks.

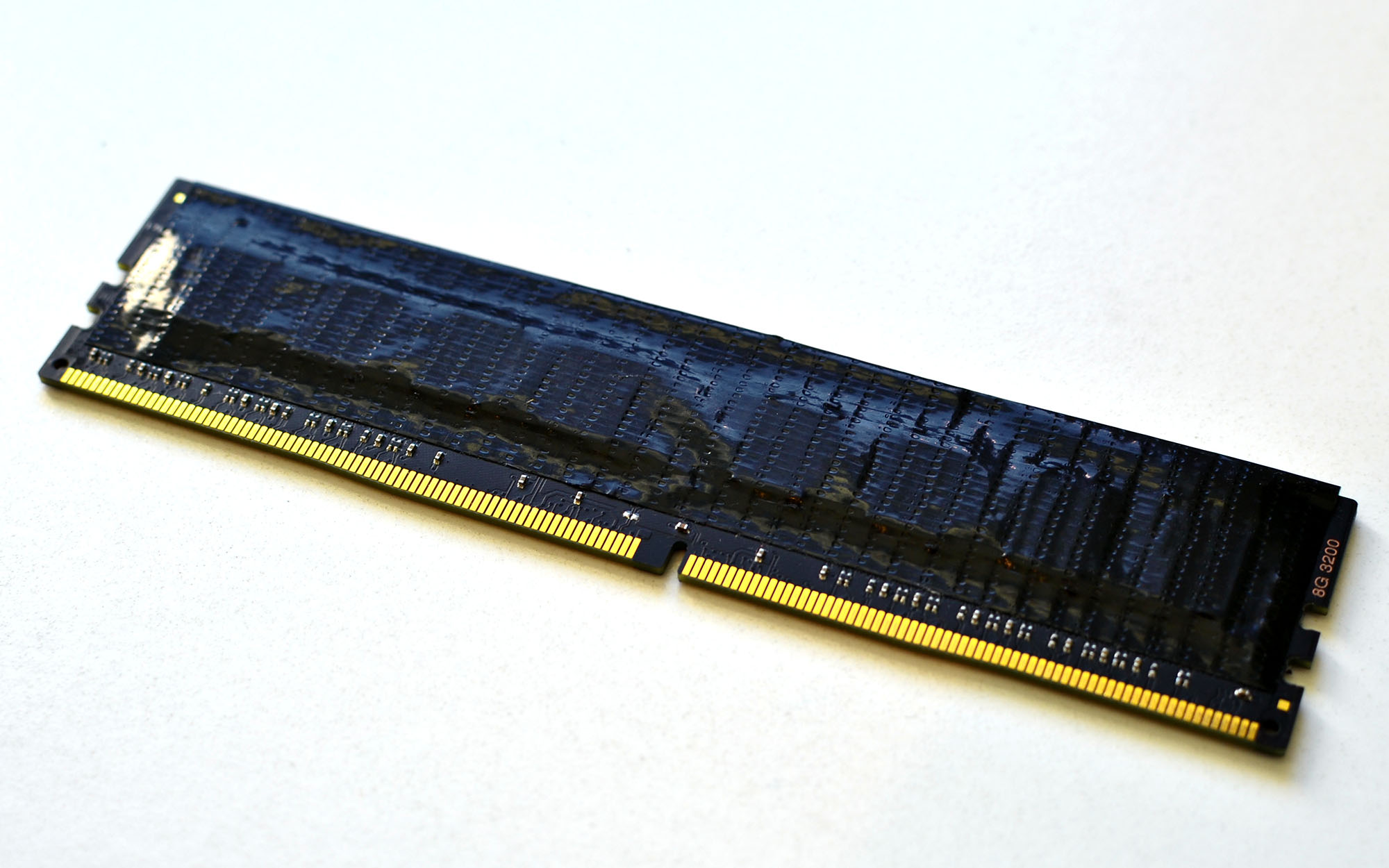

To protect our memory stick, we cover it with adhesive tape. The impermeable nature of this tape should keep condensation from ruining our day. Don't worry, the missing sinks pose no challenge to stability. Even at 1.6V, the chips remain cool.

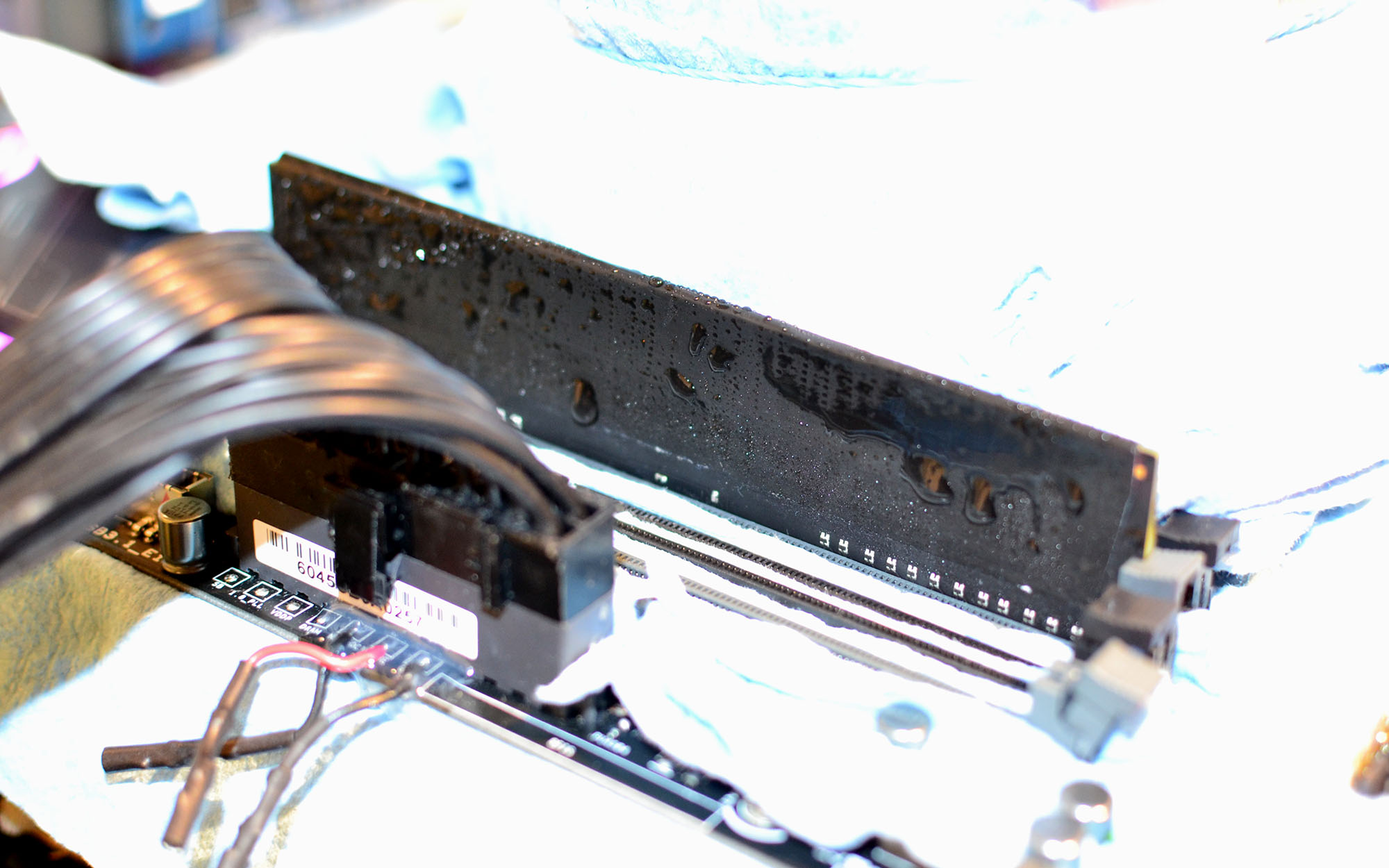

The small pins at the bottom of the module are too close to the slot to be covered. They're buried under layers of absorbent towels though, and therefore less exposed.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Even without the sinks in place to trap condensation, the surface of the RAM doesn't seem to be much less humid. This picture was taken at the end of an overclocking session, and you can clearly see drops of water on the stick's most exposed side. Nevertheless, our efforts pay off: we didn't have any issues with system cut-outs.

It would have been easier to pile paper towels around the RAM to keep water from collecting on the PCB. But then the modules would have cooled down even more through the motherboard. Given that Samsung's B-die memory dislikes freezing temperatures, they could have then failed to function at high frequencies. For better or worse, nothing is ever simple with extreme overclocking.

MORE: Best CPUs

MORE: How To Overclock AMD Ryzen CPUs

MORE: De-Lidding and Overclocking Core i7-7700K

MORE: CPU Overclocking Guide: How (and Why) to Tweak Your Processor

Current page: Preparing The RAM

Prev Page Preparing The Motherboard Next Page 1800X: First Test Of Scaling With LN2-

InvalidError It isn't surprising that the highest-end CPUs have the highest and least troublesome overclocks as that's what chip binning is for - the best dies go to the premium SKUs first, lower tiers get what is left over.Reply -

-Fran- Reply19937674 said:It isn't surprising that the highest-end CPUs have the highest and least troublesome overclocks as that's what chip binning is for - the best dies go to the premium SKUs first, lower tiers get what is left over.

Even more, it's very interesting since it gives some credibility that AMD is not binning due to defects, but electrical properties, hence, making the rumour mill of being able to unlock some 4C and 6C to higher core counts not that far-fetched.

Cheers! -

Wisecracker Très bon!Reply

(hope I used this correctly)

Just wondering ... would it be considered a 'faux pas' (or, an insult to AMD) to release the batch numbers?

-

theyeti87 Reply19937697 said:19937674 said:It isn't surprising that the highest-end CPUs have the highest and least troublesome overclocks as that's what chip binning is for - the best dies go to the premium SKUs first, lower tiers get what is left over.

Even more, it's very interesting since it gives some credibility that AMD is not binning due to defects, but electrical properties, hence, making the rumour mill of being able to unlock some 4C and 6C to higher core counts not that far-fetched.

Cheers!

Wasn't that a similar case with the Phenom X4, X3, and X2's? Or were those 3's and 2's disabled cores due to defect? -

-Fran- Reply19937706 said:19937697 said:19937674 said:It isn't surprising that the highest-end CPUs have the highest and least troublesome overclocks as that's what chip binning is for - the best dies go to the premium SKUs first, lower tiers get what is left over.

Even more, it's very interesting since it gives some credibility that AMD is not binning due to defects, but electrical properties, hence, making the rumour mill of being able to unlock some 4C and 6C to higher core counts not that far-fetched.

Cheers!

Wasn't that a similar case with the Phenom X4, X3, and X2's? Or were those 3's and 2's disabled cores due to defect?

They were a mix of both. If you were lucky (and could track down some of the batches) you were able to unlock the CPU with little worry, but there were defective ones that when unlocked, would not work. I came across both myself.

To be honest, I just catalog it as "interesting", because I will pay the difference to always get the full working version, but I do know there's people out there that like gambling and can track batch numbers :P

Cheers! -

InvalidError Reply

The relatively low defect rate has been a given since launch IMO: half of each CPU core is L2 cache and half of the CCX die area is the L3, so you have a 50% chance that defects within a CCX will land in L3. If the defect rate had been significant, cache defects would have forced AMD to launch models with 8MB of L3 long before the 1400.19937697 said:Even more, it's very interesting since it gives some credibility that AMD is not binning due to defects, but electrical properties -

-Fran- Reply19937880 said:

The relatively low defect rate has been a given since launch IMO: half of each CPU core is L2 cache and half of the CCX die area is the L3, so you have a 50% chance that defects within a CCX will land in L3. If the defect rate had been significant, cache defects would have forced AMD to launch models with 8MB of L3 long before the 1400.19937697 said:Even more, it's very interesting since it gives some credibility that AMD is not binning due to defects, but electrical properties

True. It's just nice to have more non-validated statistical-irrelevant proof! Haha.

Cheers! :P -

Gregory_3 This is all kind of cute, but the real market success will be played out in conventional liquid cooled and air cooled environments. Nobody is going be running high end software with condensation dripping all over.Reply -

InvalidError Reply

There wouldn't be condensation issues if OCers used the nitrogen gas boiling out of the pot to displace air and the moisture it contains around the motherboard to keep it off of it. Instead of circulating the boil-off around the motherboard though, LN2 OCers use fans to suck it away, drawing more moisture-ladden air in the area.19938043 said:Nobody is going be running high end software with condensation dripping all over.

-

gasaraki "It isn't surprising that the highest-end CPUs have the highest and least troublesome overclocks as that's what chip binning is for - the best dies go to the premium SKUs first, lower tiers get what is left over."Reply

While it might not be surprising, it shows the immaturity of the Ryzen processors in that the build quality is not the same between different CPUs or even CCXes and binning is what they do for the lower cored versions. If your build process was mature ALL your chips would come out mostly the same and "awesome" then at that point your forced to just shutdown cores to make the lower cored processors.