RAM Wars: Return of the JEDEC

Enter GDDR2 SDRAM, Continued

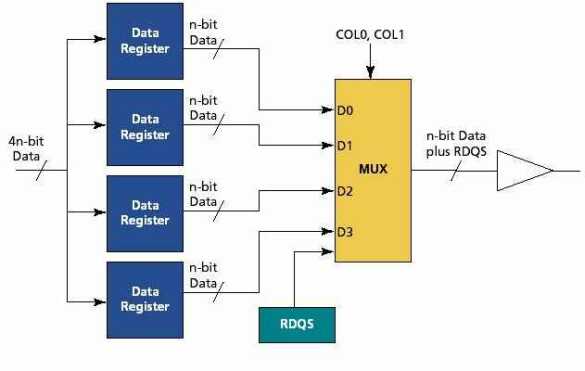

If you have not guessed already, Micron has been very forthcoming about the technical details of its future products, including information about its flavor of GDDR3, and says it will have samples before the first half of 2003 has passed. According to Micron, instead of the 2n-prefetch used with DDR, GDDR3 will offer a 4n-prefetch rate that transfers four data bits every two clock cycles at the I/O pins. A single read or write access for GDDR3 will consist of a single, 4n bit wide data transfer at the internal DRAM core. The 4n-prefetch will thus enable the internal data bus to be four times the width of the external data bus, and will enable the external data transfer rate to be four times the internal column cycle time.

GDDR3, Micron says, will also employ "pseudo open drain logic," which accounts for the I/O interface and simplifies data clocking by having all tri-stated data strobes "float" to a natural Logic, Micron says. The bus is dual-end terminated using the 40Ω controlled impedance driver at the source and the 60Ω on-die termination to VDD at the destination.

Unlike a pure open drain scheme, source termination is achieved on LOW-to-HIGH transitions by using the PMOS device of the push driver. DC power is also minimized since it is only consumed when a logic LOW is driven onto the bus.

GDDR3 also utilizes an external precision resistor (RQ) tied to VSS to calibrate the driver to a known value. Micron says that this eliminates most of the process variation that can be introduced during manufacturing. Initially, the driver functions as a standard push-pull driver with multiple legs to tune the impedance and adjust the on-die termination resistor (RQ) to be six times the desired driver impedance. The PMOS device is first calibrated to the resistor tied to ground. This calibrates one PMOS leg to 240Ω. The pull-up stage for this output buffer consists of six legs, which is the nominal 40Ω equivalent pull-up driver. After the PMOS leg is calibrated to the external resistor, the NMOS leg is calibrated to the PMOS leg in a similar fashion.

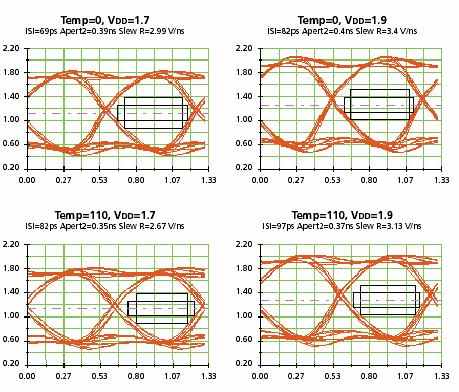

After the process variations have been eliminated, the only other factors that need to be addressed are voltage and temperature variations that occur over time in the system. To address these two issues, the GDDR3 driver provides periodic updates to recalibrate, which minimizes the variation in the pull-up and pull-down drive current due to voltage and temperature. Updates currently take place at a minimum of every 70µs during AUTO REFRESH commands, but this can be adjusted to as small of an interval as needed. The initial calibration takes approximately 350 clock cycles, but the recalibration and updates take less than one clock cycle. The only time the output driver cannot be recalibrated is when there is read data on the bus.

Read Data Eyes (1.5 GHz) of Micron's "pseudo open drain logic" for GDDR3.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: Enter GDDR2 SDRAM, Continued

Prev Page Enter GDDR2 SDRAM Next Page The Return Of The JEDEC