RAM Wars: Return of the JEDEC

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

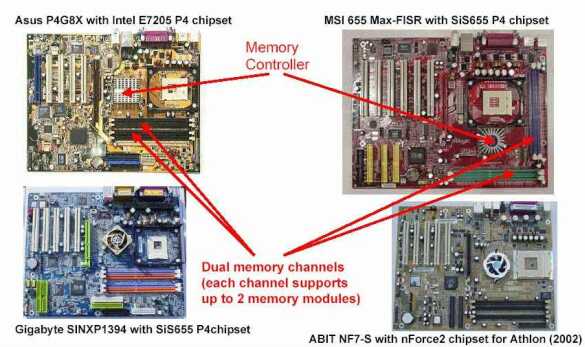

Dueling Channels, Continued

Rambus' 400 MHz RDRAM bus is 800 MHz because a Rambus memory block can send two pieces of information per clock cycle. Like DDR-400, because the Rambus bus width is 16 bit, its data transfer rate is 1.6 GBytes/s.

But with every additional memory interface, there come additional physical constraints involving inductance, or the electro-magnetic behavior of electrical memory. When the processor sends a signal down the pipe and there is a mismatch in signals, for example, then there is a reflection of the signal, and the data signal can be rejected.

The amount of wire in a number of junctions in any given channel wire (such as from the chip's package to the motherboard, up the motherboard into the socket, and then from the socket into the module), represents additional junctions, which introduces the possibility of mismatches. So with additional DIMMs or sockets, which is the case with DDR400, the potential for more reflection is created.

In the very early days of Rambus, there were three sockets, which rendered many motherboards unstable. A '1' that was not there was read, or a '0' that was not there. They solved that by getting rid of one of the sockets and going to two sockets.

So, while dual channel DDR400 appears to be a great thing, only benchmark tests on the motherboards will indicate how stable they will be once they become commercially available.

Motherboards with 800 MHz front-side buses and double channel DDR400 will soon be put to the speed and stability tests (source: Kingston).

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.