RAM Wars: Return of the JEDEC

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Enter DDR

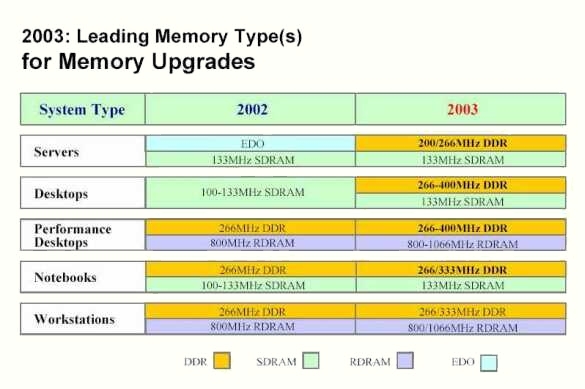

After debuting last year, DDRAM has begun to edge out SDRAM (source: Kingston).

As far as the state of the market goes, SDRAM is quickly being edged out. The transition from SDRAM to DDRAM happened in a major way during the last two quarters of last year, to the extent that DDRAM is reaching maturity and SDRAM is ramping down.

For new PC systems, it is now a question of which speed DDRAM to use: 266 MHz, 333 MHz, or 400 MHz, with the bulk of the market being 266 MHz or 333 MHz.

DDR (double data rate), as its name implies, offers read and write functions that are twice as fast as those of SDRAM, by reading data twice a clock cycle compared to SDRAM's once. With SDRAM, data is read on the rising edge of the clock, while DDRAM reads data on the rising and trailing edge of the clock.

DDRAM, however, has its limitations, according to a patent filed by Micron and obtained by THG. The handicap is related to the burst limitation of DDR. Burst operation comprises retrieving limited data from sequential locations within the memory. During a DDR device clock cycle, two words of data, each of n bits length, are retrieved. Both data signals must be from the same location within the memory as addressed by the logical circuitry before the next location can be approached. This is acceptable for a full-page increment burst starting with an even start word address, because the second data word retrieved is still within the same location in the memory as the first data word. However, a full-page increment burst starting with an odd start word address does not work, because the second data word retrieved will necessarily not lie within the same location as the first data word as addressed by the logical circuitry, violating the limitation of the prefetch nature of DDR devices.

DDRAM also supports ECC (error correction code), which comes in handy for servers. ECC involves transferring extra bits of data. In a 64 bit data bus, for example, there is an extra bit for every 8 bit of data. The 64 bit data bus thus goes from 8-Bytes to 9-Bytes, as there is a bit for every Byte, and becomes 72 bits wide. The extra bits serve to help indicate whether there is an error in the signal transmission, and supplant the missed signal.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.