Intel Core i7 (Nehalem): Architecture By AMD?

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

SSE 4.2 And Power Consumption

With the Nehalem architecture, Intel couldn’t resist adding some new items to the already long list of SSE instructions. Nehalem supports SSE 4.2, which has all the instructions supported by Penryn (SSE4.1) and adds seven more. Most of these new instructions are for manipulating character strings, one purpose of which, Intel says, is to speed up the processing of XML files.

The two other instructions are aimed at specific applications; one is POPCNT, which appeared with Barcelona, and is used to count the number of non-zero bits in a register. According to Intel, this instruction is especially useful in voice recognition and DNA sequencing. The last instruction, CRC32, is used for accelerating the calculation of error detection codes.

Power Consumption Under Control

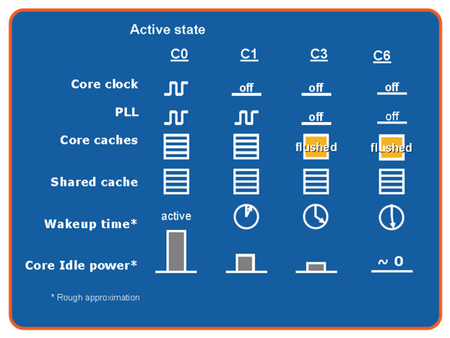

Over and over Intel says that for any potential innovation in one of its new architectures, the engineers weigh performance gains against the impact on power consumption—it’s proof that they’ve learned well from Pentium 4. With the Nehalem architecture, the engineers have gone even farther with techniques for limiting consumption. There’s now a built-in microcontroller—the Power Control Unit—that constantly watches the temperature and power use of the cores and can disable them completely when they’re not being used. Thanks to this technology, the energy consumption of an unused core is next to zero, whereas before Nehalem there were still losses due to leakage currents.

Intel has implemented this in an original way with what it calls a Turbo mode. When the processor is operating below its standard TDP, for example, the Turbo mode increases the frequency of the cores being used, while still keeping within the TDP limit.

Note also that like the Atom processor, Nehalem’s L1 and L2 caches use eight transistors instead of the usual six, which reduces consumption at the cost of a slightly larger die surface.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: SSE 4.2 And Power Consumption

Prev Page SMT Implementation Next Page QuickPath Interconnect-

cl_spdhax1 good write-up, cant wait for the new architecture , plus the "older" chips are going to become cheaper/affordable. big plus.Reply -

neiroatopelcc No explaination as to why you can't use performance modules with higher voltage though.Reply -

neiroatopelcc AuDioFreaK39TomsHardware is just now getting around to posting this?Not to mention it being almost a direct copy/paste from other articles I've seen written about Nehalem architecture.I regard being late as a quality seal really. No point being first, if your info is only as credible as stuff on inquirer. Better be last, but be sure what you write is correct.Reply

-

cangelini AuDioFreaK39TomsHardware is just now getting around to posting this?Not to mention it being almost a direct copy/paste from other articles I've seen written about Nehalem architecture.Reply

Perhaps, if you count being translated from French. -

randomizer Yea, 13 pages is quite alot to translate. You could always use google translation if you want it done fast :kaola:Reply -

Duncan NZ Speaking of french... That link on page 3 goes to a French article that I found fascinating... Would be even better if there was an English version though, cause then I could actually read it. Any chance of that?Reply

Nice article, good depth, well written -

neiroatopelcc randomizerYea, 13 pages is quite alot to translate. You could always use google translation if you want it done fast I don't know french, so no idea if it actually works. But I've tried from english to germany and danish, and viseversa. Also tried from danish to german, and the result is always the same - it's incomplete, and anything that is slighty technical in nature won't be translated properly. In short - want it done right, do it yourself.Reply -

neiroatopelcc I don't think cangelini meant to say, that no other english articles on the subject exist.Reply

You claimed the article on toms was a copy paste from another article. He merely stated that the article here was based on a french version. -

enewmen Good article.Reply

I actually read the whole thing.

I just don't get TLP when RAM is cheap and the Nehalem/Vista can address 128gigs. Anyway, things have changed a lot since running Win NT with 16megs RAM and constant memory swapping. -

cangelini I can't speak for the author, but I imagine neiro's guess is fairly accurate. Written in French, translated to English, and then edited--I'm fairly confident they're different stories ;)Reply