X570 Exposed: Up to Sixteen PCIe 4.0 Lanes, Flexible I/O

This is not the X470 chipset replacement you were looking for--at least according to our conversations with AMD: The X570 is not a replacement for the X470, but instead slots in as a higher tier. That means the firm’s X470 will soldier on as a value-oriented alternative to high-priced X570 models, and we may even see new X470 boards with updated layouts and features targeting people who can’t justify X570 premiums.

But this “model up” philosophy provides a reason for the firm to kill PCIe 4.0 graphics support on future X470 motherboards: Anyone who wants that pathway from the CPU to the GPU will likely be forced to buy an X570 motherboard, unless they use hacked firmware. It’s not in the firm’s interest to produce a separate AGESA for the new X470 motherboards (though we guess that this could change).

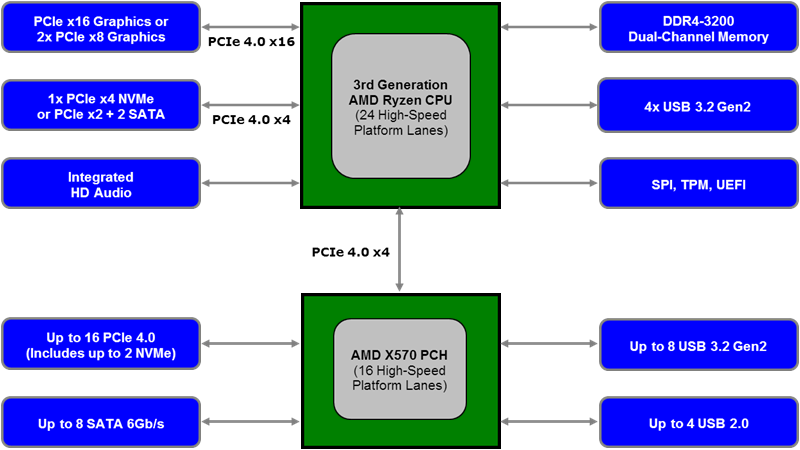

In the meantime, we spent some time over the course of several days to firm up the device connection limits for the X570 PCH, producing a block diagram from real-world application data.

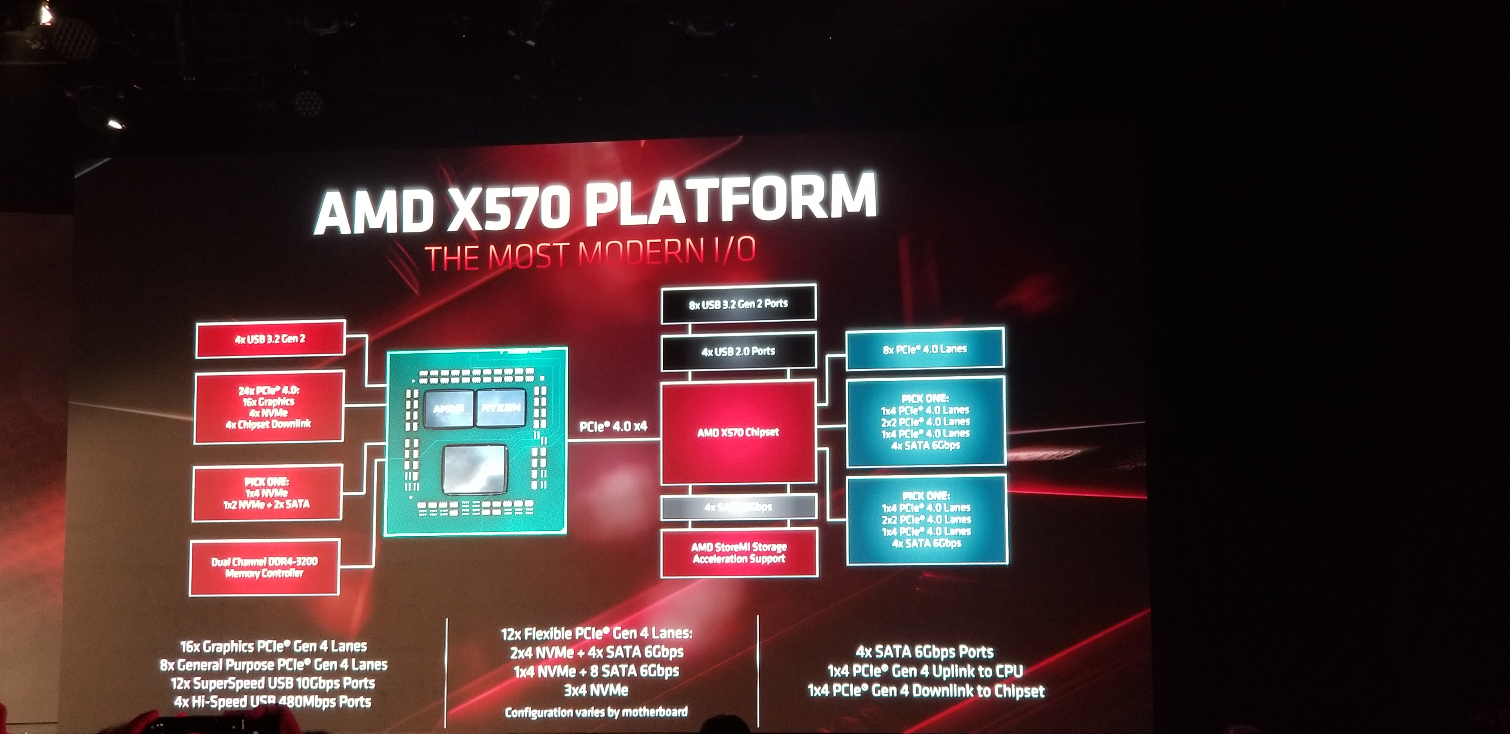

The first thing most in-the-know readers will notice is that the PCH supports eight USB 3.2 Gen2 (10 Gb/s) pathways and eight SATA 6 Gb/s ports rather than four and two quoted for the CPU. That may seem odd since the X570 PCH is nothing more than a 14nm variant of the 12nm I/O die inside the Ryzen 3000-series processors, but it simply appears that the I/O die’s pathways are far more flexible than previously disclosed.

July 2nd Update: Rumors of additional USB 2.0 ports on the PCH turned out to be via conversion (breaking out the USB 2.0 data pins from the USB 3.x interface), as expected. AMD also dismissed rumors of the PCH not supporting full Gen2 transfers as an attempt by motherboard manufacturers to save cost on additional devices such as redrivers.

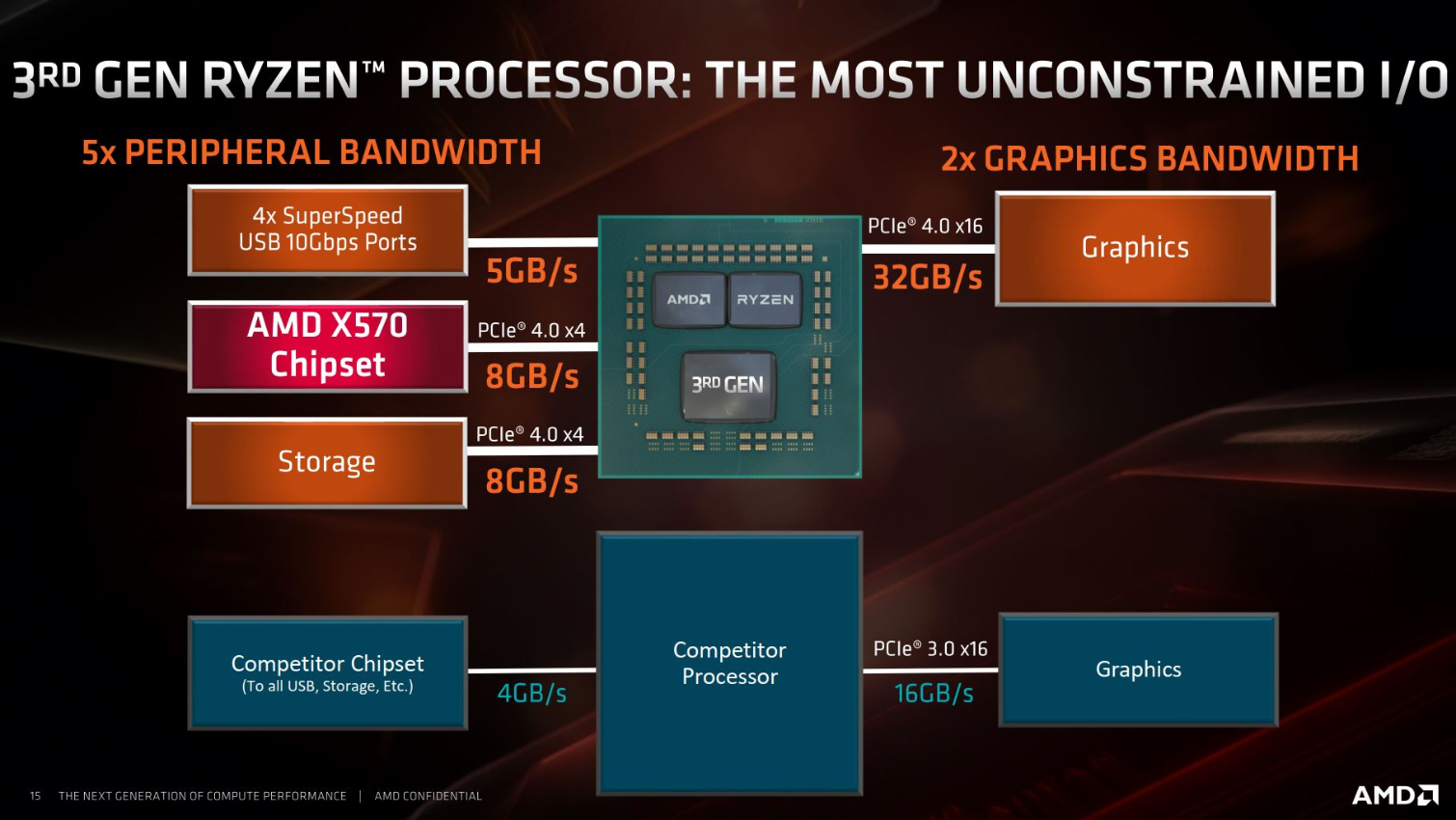

A little creative destruction rids the PCH version of the CPU’s memory controller and any unnecessary appendages, as each of those maximum connections must be selectively reduced by the motherboard manufacturer to fit everything into a combined 16 High-Speed Platform Lanes. That may be just as well since device bandwidth is shared over a single PCIe 4.0 x4 connection to the CPU, though we have to at least give AMD credit for doubling that over its previous PCIe 3.0 version.

We're fairly certain that the second CPU-based NVMe connection shown by AMD at its E3 Press Event should have been a breakout of the first, since motherboard manufacturers have only been able to get one PCIe 4.0 x4 NVMe interface directly from the CPU. A total of 24 CPU lanes that include 16 lanes for graphics, four for storage and four for USB 3.x Gen2 conforms to AMD's statement that "High-Speed Platform Lanes defined as the sum of GPP PCI Express lanes, SATA ports and USB ports from the chipset and processor that can be used concurrently."

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Regarding the PCH, those same motherboard firms are extracting up to eight SATA ports from the PCH in addition to a second and third PCIe 4.0 x4 M.2 slots, with the only resource exclusion being that those board's third expansion card slot is disabled when the third M.2 slot is enabled. These details may explain the absence of the above image in the official slide deck AMD later provided.

We'll inspect final products to be certain about USB 2.0 count, since motherboard manufacturers occasionally double-count USB 2.0 by adding the backwards compatibility of USB 3.0 ports.

Hmm, PCH, HSIO, where have we heard that before?

This article is part of the Tom's Hardware Glossary.

-

mattkiss "The first thing most in-the-know readers will notice is that the PCH supports eight USB 3.2 Gen1 (5Gb/s) pathways rather than four Gen2 (10Gb/s) "Reply

The AMD slide says the chipset USB 3.2 ports are Gen 2. -

mattkiss "A total of 24 CPU lanes that include sixteen lanes for graphics, four for storage, and four for USB 3.x Gen2 "Reply

The last four PCie lanes from the CPU connect to the chipset. They are not used for the USB 3.2 Gen2 ports coming from the CPU. -

Crashman Reply

You should read the full article then ;)mattkiss said:"The first thing most in-the-know readers will notice is that the PCH supports eight USB 3.2 Gen1 (5Gb/s) pathways rather than four Gen2 (10Gb/s) "

The AMD slide says the chipset USB 3.2 ports are Gen 2.

You should read the full article then ;)mattkiss said:"A total of 24 CPU lanes that include sixteen lanes for graphics, four for storage, and four for USB 3.x Gen2 "

The last four PCie lanes from the CPU connect to the chipset. They are not used for the USB 3.2 Gen2 ports coming from the CPU. -

Crashman I'll make it easy for you:Reply

A total of 24 CPU lanes that include sixteen lanes for graphics, four for storage, and four for USB 3.x Gen2 conforms to AMD's statement that "High-Speed Platform Lanes defined as the sum of GPP PCI Express lanes, SATA ports, and USB ports from the chipset and processor that can be used concurrently."

Now you can argue with AMD :D

OH, I just noticed what you did: You appended the reference to AMD. In other words, you're not even bringing an honest debate.

OK, so the PCH has sixteen lanes and none of them are used for the uplink right? But the CPU I/O die has 24 lanes and 4 of them are used for the PCH downlink, right? And they're the same chip, apart from one being manufactured at 14nm and the other and 12nm, right?

Please explain your new math. You see, we want our table to be as accurate as possible, but AMD's table doesn't coincide with its written statement. We got ours verified by a motherboard design team that's actually building product around this chipset, so to this point the only thing we suspect may be inaccurate is the USB 2.0 count. -

epobirs It seems disingenuous to say they've got a USB 3.2 host if they aren't supporting the four lane 20 Gbps mode. This is a point of curiosity for me since having that capability would mean a great deal for expansion storage on the upcoming Sony and Microsoft games consoles. Since those machine will need far fewer PCIe 4 lanes in general, one possibility is a second M.2 slot for added fast storage (though likely packaged in something safer for consumers to handle plugging in) and allowing metadata and smart system management to decide which games won't suffer greatly if consigned to the much slower external storage. A cheap and slow-ish M.2 SSD like the Intel 660p isn't going to lose much from being used externally over USB 3.2 Gen 2 but would still be a great improvement over current console storage. Except for those who feel the need to have absurdly large digital libraries entirely installed.Reply -

Crashman Reply

This is not an AMD issue, it's a USB-IF issue. The group has essentially rendered the number after the decimal point useless, so we'd might as well just call it USB 3.x and then shorten that to USB 3. The part that matters under its current naming scheme is the Gen rating, where Gen1 means 5Gb/s, Gen2 means 10Gb/s, and Gen 2x2 means that two Gen2 ports are bonded to provide up to 20Gb/s over two pathways.epobirs said:It seems disingenuous to say they've got a USB 3.2 host if they aren't supporting the four lane 20 Gbps mode. This is a point of curiosity for me since having that capability would mean a great deal for expansion storage on the upcoming Sony and Microsoft games consoles. Since those machine will need far fewer PCIe 4 lanes in general, one possibility is a second M.2 slot for added fast storage (though likely packaged in something safer for consumers to handle plugging in) and allowing metadata and smart system management to decide which games won't suffer greatly if consigned to the much slower external storage. A cheap and slow-ish M.2 SSD like the Intel 660p isn't going to lose much from being used externally over USB 3.2 Gen 2 but would still be a great improvement over current console storage. Except for those who feel the need to have absurdly large digital libraries entirely installed. -

velocityg4 The write up and block diagrams aren't clear. At least they aren't to me. I'd expect each block to be an exclusive capability. As in, whatever goes on in one block does not affect the others.Reply

One interpretation is that a motherboard could support this setup concurrently.

CPU Connections

1 PCIe 4.0 x16 card

1 NVMe 4.0 x4 SSD

Audio

DDR4 Dual Channel

4 USB 3.2 Gen2

SPI, TPM, UEFI

PCH

PCH Connections

8 SATA III

8 USB 3.2 Gen2

4 USB 2.0

2 NVMe x4 SSD with x8 PCIe 4.0 remaining for lower expansion slots (from 16 PCIe 4.0 in blue box)

Another is a more limited view. Yes there are more options. I'm just taking an example from each blue block.

CPU

24 Lanes total

4 Lanes used by PCH leaving 20 remaining

20 remaining lanes shared by PCIe x16 slot, NVMe, USB 3.2 Gen 2

Audio, SPI, TPM, UEFI have their own connections

PCH

16 total shared lanes

Split up between SATA, USB 3.2 Gen 2, USB 2.0, NVMe and extra PCIe slots. However, the motherboard maker divvies it up or dependent on which features a user makes use of.

I just want to clarify. Which of the blocks is exclusive? If not all of them. Which are dependent upon the configuration of others? -

Crashman Reply

How about we split the difference and ignore the PCH to CPU connnection? Let me explain:velocityg4 said:The write up and block diagrams aren't clear. At least they aren't to me. I'd expect each block to be an exclusive capability. As in, whatever goes on in one block does not affect the others.

One interpretation is that a motherboard could support this setup concurrently.

CPU Connections

1 PCIe 4.0 x16 card

1 NVMe 4.0 x4 SSD

Audio

DDR4 Dual Channel

4 USB 3.2 Gen2

SPI, TPM, UEFI

PCHPCH Connections

8 SATA III

8 USB 3.2 Gen2

4 USB 2.0

2 NVMe x4 SSD with x8 PCIe 4.0 remaining for lower expansion slots (from 16 PCIe 4.0 in blue box)Another is a more limited view. Yes there are more options. I'm just taking an example from each blue block.

CPU

24 Lanes total

4 Lanes used by PCH leaving 20 remaining

20 remaining lanes shared by PCIe x16 slot, NVMe, USB 3.2 Gen 2

Audio, SPI, TPM, UEFI have their own connectionsPCH

16 total shared lanes

Split up between SATA, USB 3.2 Gen 2, USB 2.0, NVMe and extra PCIe slots. However, the motherboard maker divvies it up or dependent on which features a user makes use of.I just want to clarify. Which of the blocks is exclusive? If not all of them. Which are dependent upon the configuration of others?

We're told the CPU has 24 lanes and the PCH 16. But we're also told the PCH connection detracts from the CPU but not the PCH. That's impossible, each side needs four lanes. So we're being told nonsense. And since we already know that the CPU supports an x16 GPU, an x4 NVMe drive, and four USB 3.2 ports simultaneously, the notion of detracting four for the PCH connection makes no sense.

That leaves:

CPU

1 PCIe 4.0 x16 card

1 NVMe 4.0 x4 SSD

4 USB 3.2 Gen2

DDR4 Dual Channel, Audio, SPI, TPM, UEFI, PCH have their own connectionsPCH

16 total shared lanes

Split up between SATA, USB 3.2 Gen 2, USB 2.0, NVMe and extra PCIe slots. However, the motherboard maker divvies it up or dependent on which features a user makes use of. -

velocityg4 ReplyCrashman said:How about we split the difference and ignore the PCH to CPU connnection? Let me explain:

We're told the CPU has 24 lanes and the PCH 16. But we're also told the PCH connection detracts from the CPU but not the PCH. That's impossible, each side needs four lanes. So we're being told nonsense. And since we already know that the PCH supports an x16 GPU, an x4 NVMe drive, and four USB 3.2 ports simultaneously, the notion of detracting four for the PCH connection makes no sense.

That leaves:

CPU

1 PCIe 4.0 x16 card

1 NVMe 4.0 x4 SSD

4 USB 3.2 Gen2

DDR4 Dual Channel, Audio, SPI, TPM, UEFI, PCH have their own connectionsPCH

16 total shared lanes

Split up between SATA, USB 3.2 Gen 2, USB 2.0, NVMe and extra PCIe slots. However, the motherboard maker divvies it up or dependent on which features a user makes use of.

Great, that clears it up. -

Crashman Reply

Great. Please note that I corrected a mistake after reading what I said on your post. It's the CPU that supports the graphics card, an NVMe drive, and four USB 3.x ports simultaneously, because that's carried over from the previous CPU.velocityg4 said:Great, that clears it up.