Benchmark Marathon: 65 CPUs from 100 MHz to 3066 MHz

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Duron 600 To 950: June 2000 To June 2001

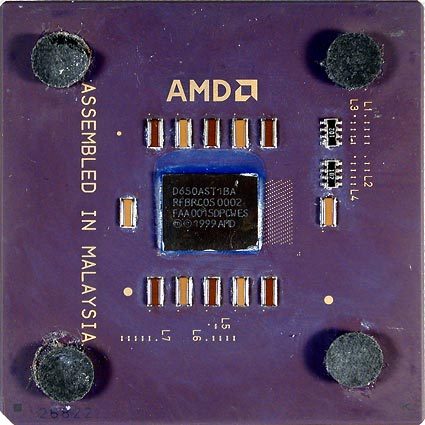

There was a "slimmed down" Athlon for the Socket 462, with a quarter of the L2 cache (64 kB) - also known under its codename of Spitfire. This meant that the L1 cache - at 128 kB - was twice the size of its L2 cache. The transistor count was 25 million and it was manufactured using the 0.18 micron process. The bus speed was 100 MHz from the outset.

It made life difficult for the Intel Celeron 700: AMD Duron 650 with Spitfire core.

Duron 900 To 1300: May 2001 To January 2002

The enhanced version of the long-running Intel Celeron (II) competitor was based on the Morgan core and included new features such as SSE extensions and 3DNow+. The transistor count rose to 25.18 million and fabrication was based on the 0.18 micron process. Bus speed remained at 100 MHz.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: Duron 600 To 950: June 2000 To June 2001

Prev Page Athlon 650 To 1400: June 2000 To June 2001 Next Page Athlon XP 1500+ To 2100+: October 2001 To March 2002