Intel 18A

Latest about Intel 18A

High-ranking TSMC executive faces Taiwan legal investigation over murky return to Intel

By Anton Shilov published

From Intel to TSMC and back?

Intel's pivotal 18A process is making steady progress, but still lags behind

By Anton Shilov published

Expect a slow ramp.

Intel Foundry secures contract to build Microsoft's Maia 2 next-gen AI processor on 18A/18A-P node, claims report

By Anton Shilov published

Microsoft and Intel announced their partnership last year

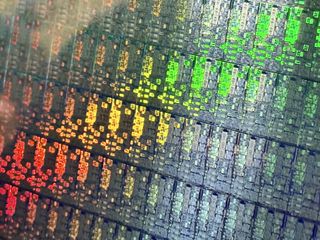

Intel's 18A production starts before TSMC’s competing N2 tech

By Anton Shilov published

Production starts at Fab 52.

Intel takes the wraps off Panther Lake — first 18A client processor brings the best of Lunar Lake and Arrow Lake together in one package

By Jeffrey Kampman published

Panther Lake brings the power efficiency and graphics performance of Lunar Lake and the platform flexibility of Arrow Lake all together on one SoC

Amid Intel's deals, Intel Foundry remains notably absent — 18A and 14A are on the way, but success isn't guaranteed

By Luke James published

Premium It has been a busy few weeks for semiconductors, but among various announcements and rumors, Intel Foundry has remained conspicuously absent.

Intel CFO confirms that 14A will be more expensive to use than 18A

By Anton Shilov last updated

Intel's 14A process, designed for both internal and foundry use, will be significantly more expensive than 18A due to its reliance on ASML's $380 million High-NA EUV tools.

Intel admits its high-end desktop PC chips 'fumbled the football,' disusses 18A yield challenges and performance, Panther Lake ramp

By Anton Shilov published

Intel sees performance of Panther Lake processors as competitive, but it admits lower-than-desired 18A yields and weak offerings on desktop and data center markets.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.