The TFT Connection: Do NVIDIA and ATi Deliver?

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

DVI Jitter Management

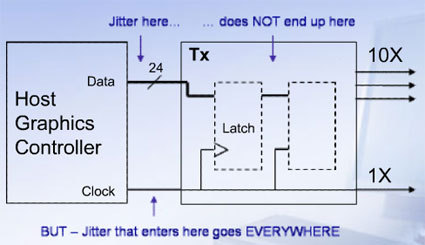

Since DVI transmission is completely digital, that poses the question where signal jitter actually originates. There are two possibilities here. The first would be that it is caused or transmitted by the data itself, i.e. the 24-bit parallel data bits that the graphics chip produces. However, this data is automatically corrected by a latch in the TMDS chip if necessary, ensuring that the graphics data signal is jitter-free. Therefore, the only remaining source is jitter generated by the clock signal.

At first, our data signal is free from any interference. This is ensured by a latch integrated into the TMDS. Therefore, the main problem must stem from the clock signal, which falsifies the data stream via its detour through the 10x multiplication in the PLL.

Since the data is multiplied by a factor of 10 using a PLL, every little flaw has a direct impact. As a result, the data no longer reaches the receiver in its original state.

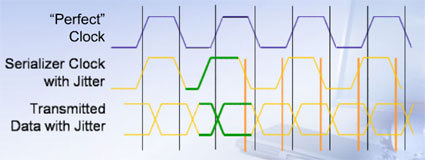

The upper image shows a perfect clock signal, the one below it a signal where the onset of the flank comes too early. Through the PLL, this directly affects the data being transmitted. In short: Every perturbance in the clock signal results in a faulty data transmission.

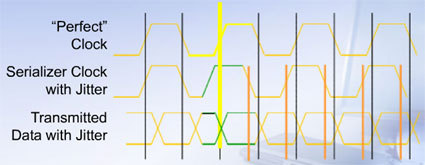

Why is that important to know? When the receiver samples the faulty data stream using a "perfect" clock signal of a hypothetical internal PLL clock, it catches the wrong data (yellow line).

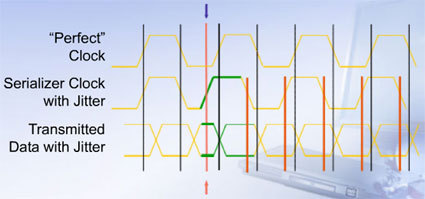

How it really works: If the receiver uses the faulty clock signal of the transmitter it can still read the faulty data stream (red line). This is why the clock signal needs to be transferred via the DVI cable! The receiver needs the same (faulty) clock signal.

The DVI standard includes "jitter management." This describes the transmission of the transmitter's clock signal directly to the receiver. When both components rely on the same faulty clock signal, this allows for an error-free reading out of the faulty data stream. In this manner, DVI compliant devices are capable of operating even with large amounts of "low frequency jitter" present. The error in the clock signal can simply be ignored.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: DVI Jitter Management

Prev Page DVI Compliance Tests, Continued Next Page Causes For Jitter With DVI-

Thanks for this. Saved me lots of trouble with (not) chosing an incompatible DVI cable for my monitor / computer connection.Reply