Manufacturing

Explore Manufacturing

Latest about Manufacturing

ASML's roadmap for chipmaking lithography tools examined — from DUV to Low-NA, High-NA, Hyper-NA, and beyond

By Luke James published

Premium ASML shipped 48 EUV lithography systems and 131 immersion DUV tools in 2025, generating €32.7 billion in total revenue and ending the year with a €38.8 billion order backlog.

Intel details 18A-P process node, touts higher performance, lower power, and much more

By Anton Shilov published

Intel details improvements of 18A-P that include higher performance, lower power, reduced variability, improved yields, and more.

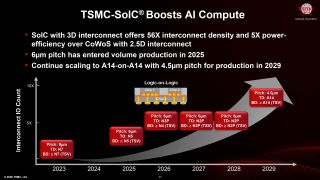

TSMC SoIC 3D stacking roadmap outlines path from 6-micron pitches today to 4.5-micron in 2029

By Anton Shilov published

Premium TSMC adds support for face-to-face stacking, 6.5 µm and 4.5 µm pitches for the next generation of SoIC 3D stacking.

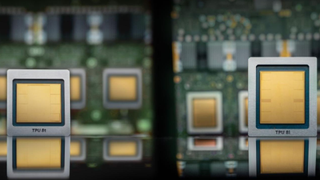

Inside Google's TPU V8 strategy, delivering two chips for two crucial tasks at incredible scale

By Luke James published

Premium Google announced its eighth-gen TPUs at Cloud Next, shipping two distinct chip designs for the first time in the TPU program's decade-long history.

TSMC's details next-gen CoWoS roadmap: over 14-reticle packages and 48x leap in compute power expected by 2029

By Anton Shilov published

Premium TSMC claims that CoWoS innovations will enable 48x more compute and 34x more memory bandwidth for 2029 AI processors.

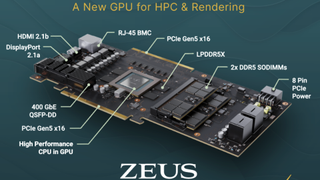

Bolt Graphics tapes out its first Zeus GPU test chip on TSMC 12nm

By Luke James published

Bolt Graphics has announced its completed tape-out of a test chip for its Zeus GPU, marking the startup's first move from FPGA emulation to manufactured silicon.

Elon Musk says TeraFab will use Intel's 14A process technology to make AI chips

By Anton Shilov published

Elon Musk reveals details about TeraFab: Intel provides technology, Tesla builds pilot line, SpaceX constructs high-volume fab.

TSMC unveils process technology roadmap through 2029 — A12, A13, N2U announced, A16 slips to 2027

By Anton Shilov published

TSMC strengthens its bifurcated process technology development approach with A14, A13, and N2U aimed at client applications and A16, A12, and N2X for high-performance data center designs.

Congress moves to strip the DoC of chip-export discretion with the MATCH Act

By Luke James published

Premium A bipartisan group of U.S. lawmakers introduced the Multilateral Alignment of Technology Controls on Hardware Act, or MATCH Act, in early April.

US lawmakers amend new restrictions on Chinese chipmakers — MATCH Act's blanket restrictions removed from select chipmaking tools

By Anton Shilov published

U.S. lawmakers remove countrywide exports ban on cryogenic etching tools from the MATCH Act, yet Chinese companies could barely get them anyway.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.