DDR3-1333 Speed and Latency Shootout

OCZ PC3-10666 Platinum Edition

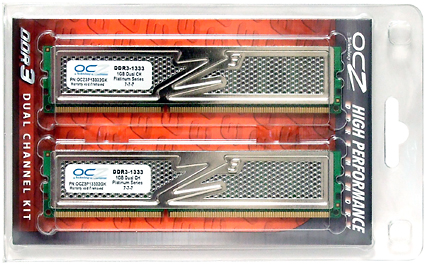

Like Kingston, OCZ wants to appeal to the largest group of DDR3-1333 buyers by offering multiple models. Unlike Kingston, the "lesser" kit supplied by OCZ actually represents the company's midrange parts, with the same CAS 7 timings as its competitor's high-end parts.

That's right, price shoppers will find an even cheaper Gold kit from OCZ, but the firm's midrange Platinum Edition provides timings of 7-7-7-20. These are not just rated timings that require messing with BIOS to achieve, but are also found in the SPD values of this part number OCZ3P13332GK dual-channel 2 x1 GB kit.

But this is where things get a little strange; OCZ's Platinum Series is actually rated to run its full performance values at 1.70 volts, yet its SPD table allows these timings to be set at 1.50 volts. OCZ is one of the companies that historically have provided modules that simply weren't bootable on some systems because its SPD values were too tight to operate at a motherboard's default voltage (1.50 volts for DDR3).

The great news is that our modules were able to operate stably at full-rated timings without manually increasing the voltage from motherboard default 1.50 to OCZ's recommended 1.70 volts. This was true for both our Gigabyte and Asus motherboards.

An SPD value of 761 MHz (DDR3-1522) at 8-8-8-23 timings provides extra room for new overclockers who are not yet familiar with manual changes, while SPD values for 571 MHz and 476 MHz translate downward to DDR3-1066 and DDR3-800 for lower FSB processors.

Current page: OCZ PC3-10666 Platinum Edition

Prev Page Mushkin Enhanced EM3-10666 Next Page OCZ PC3-10666 ReaperX HPC Enhanced BandwidthGet Tom's Hardware's best news and in-depth reviews, straight to your inbox.

-

dv8silencer I have a question: on your page 3 where you discuss the memory myth you do some calculations:Reply

"Because cycle time is the inverse of clock speed (1/2 of DDR data rates), the DDR-333 reference clock cycled every six nanoseconds, DDR2-667 every three nanoseconds and DDR3-1333 every 1.5 nanoseconds. Latency is measured in clock cycles, and two 6ns cycles occur in the same time as four 3ns cycles or eight 1.5ns cycles. If you still have your doubts, do the math!"

Based off of the cycle-based latencies of the DDR-333 (CAS 2), DDR2-667 (CAS 4), and DDR3-1333 (CAS8), and their frequences, you come to the conclusion that each of the memory types will retrieve memory in the same amount of time. The higher CAS's are offset by the frequences of the higher technologies so that even though the DDR2 and DDR3 take more cycles, they also go through more cycles per unit time than DDR. How is it then, that DDR2 and DDR3 technologies are "better" and provide more bandwidth if they provide data in the same amount of time? I do not know much about the technical details of how RAM works, and I have always had this question in mind.

Thanks -

Latency = How fast you can get to the "goodies"Reply

Bandwidth = Rate at which you can get the "goodies" -

So, I have OCZ memory I can run stable atReply

7-7-6-24-2t at 1333Mhz or

9-9-9-24-2t at 1600Mhz

This is FSB at 1600Mhz unlinked. Is there a method to calculate the best setting without running hours of benchmarks? -

Sorry dude but you are underestimating the ReapearX modules,Reply

however hard I want to see what temperatures were other modules at

a voltage of ~ 2.1v, does not mean that the platinum series is not performant but I saw a ReapearX which tended easy to 1.9v(EVP)940Mhz, that means nearly a DDR 1900, which is something, but in chapter of stability/temperature in hours of functioning, ReapearX beats them all. -

All SDRAM (including DDR variants) works more or less the same, they are divided in banks, banks are divided in rows, and rows contain the data (as columns).Reply

First you issue a command to open a row (this is your latency), then in a row you can access any data you want at the rate of 1 datum per cycle with latency depending on pipelining.

So for instance if you want to read 1 datum at address 0 it will take your CAS lat + 1 cycle.

So for instance if you want to read 8 datums at address 0 it will take your CAS lat + 8 cycle.

Since CPUs like to fill their cache lines with the next data that will probably be accessed they always read more than what you wanted anyway, so the extra throughput provided by higher clock speed helps.

But if the CPU stalls waiting for RAM it is the latency that matters.