AMD EPYC Rome Benched: 64 Cores, 128 Threads Boosting to 2.2 GHz (for now)

Several benchmarks of AMD's 64-core, 128-thread EPYC Rome processors have popped up in an online database, indicating that the early chips run at a 1.4 GHz base clock and boost to 2.2 GHz.

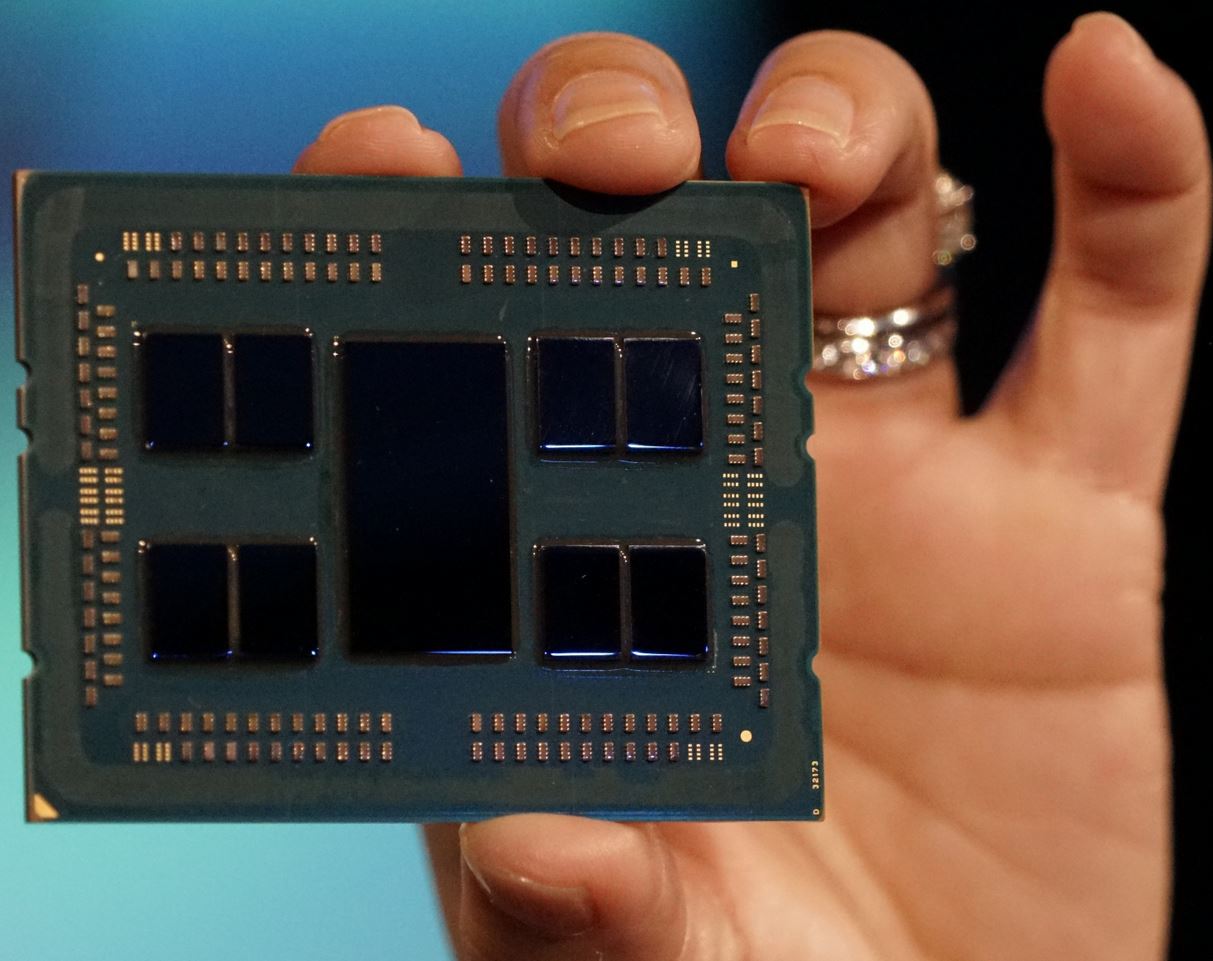

Earlier this year, AMD CEO Lisa Su announced that the 64 core 128 thread EPYC Rome processors would come to market in mid-2019, perhaps setting the stage for a massive upset victory against Intel as AMD marches forward to the 7nm manufacturing process while its competitor remains mired on 14nm.

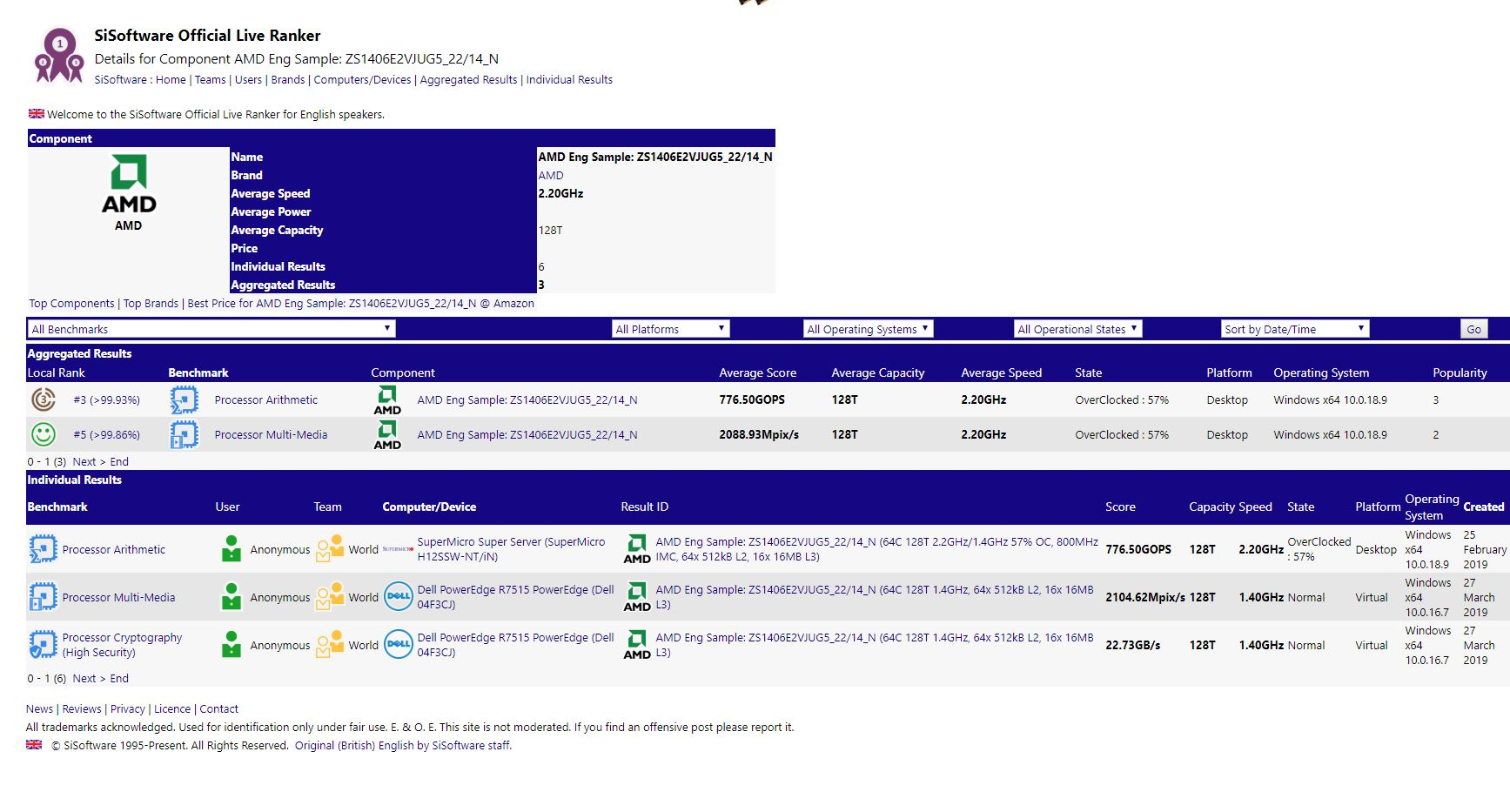

As with any chip in development, early samples are sent to manufacturers for their own interoperability and qualification testing, so we expect some test results to leak out to publicly available testing databases. Several submissions to the SiSoftware Official Live Ranker database have come to light for the EPYC Rome processors over the last few months, most bearing the "Z" descriptor at the beginning of the ZS1406E2VJUG5_22/14_N product identifier. This denotes these are qualification samples, meaning the chip is very close to a final design that will come to market.

The test system is listed as a dual-socket Dell PowerEdge R7515 server. Deconstructing the processors' product name reveals the Rome processor's base clock and boost, core and thread count and that it has 64x512KB of L2 cache and 256MB of L3 cache.

The test result reveals the processor had an average clock speed of 2.2 GHz during the test.

| Row 0 - Cell 0 | Cores/Thread | Base Frequency | Boost Frequency | L3 Cache | TDP |

| AMD ZS1406E2VJUG5_22/14_N (early silicon) | 64 / 128 | 1.4 GHz | 2.2 GHz | 256MB | ? |

| AMD EPYC 7601 | 32 / 64 | 2.2 GHz | 3.2 GHz | 64MB | 180W |

| Intel Xeon Platinum 8180 | 28 / 56 | 2.8 GHz | 3.8 GHz | 38.5MB | 205W |

As a general rule, higher core count chips tend to come with much lower base and boost frequencies, due to the increased thermal generation within the package. For instance, AMD's 32-core 64-thread EPYC 7601 has a 2.2 GHz base and 3.2 GHz boost frequency, which could suggest that either Rome's doubling of cores required yet more adjustments to reduce heat (even with a smaller, more efficient 7nm process), or that this is a model with a lower TDP than the flagship parts. AMD hasn't revealed the TDP ranges for its EPYC Rome processors, but the previous-gen models span from 120W to 180W.

AMD uses TSMC's N7 7nm process for the chips, which promises to consume half the energy of its previous-gen chips for any given operation. However, aside from improvements to energy consumption, AMD hasn't given further details about the performance of the new node.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Intel's 14nm process has been refined over the course of several years, so its 28-core 56-thread Xeon Platinum 8180 clocks in at a 2.8 GHz base and a 3.8 GHz boost.

Rome comes wielding the Zen 2 microarchitecture, which AMD says will provide up to two times the compute power per node, improved execution pipeline and double the number of cores. AMD has also doubled floating point performance with the Zen 2 microarchitecture. These gains in performance, particularly to the processors' IPC (instructions per clock), could offset lower frequencies for the higher core-count parts.

For example, Su has demoed a single 64-core EPYC Rome processor beating two of Intel's fastest data center processors. The single EPYC processor beat the two 28-core Intel Xeon 8180 processors in the scientific NAMD workload, with the Epyc processor winning by about 19 percent.

Earlier this year at the Supercomputing conference, the High Performance Computing Center accidentally released details of its new Hawk supercomputer, revealing that the Rome processors for that system will run at 2.35 GHz, which is largely thought to be a listing of the base frequencies for the processor. That information indicates that AMD may have Rome models with a higher TDP Rome that will therefore unleash more performance.

AMD continues to hold the finer details of its Rome processors close to the chest, but we expect more information to surface while we're at the Computex tech conference in Taipei, Taiwan this May.

EDIT 3/29/2019 2:00 pt: Corrected boost clock speed to 2.2 GHz.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.