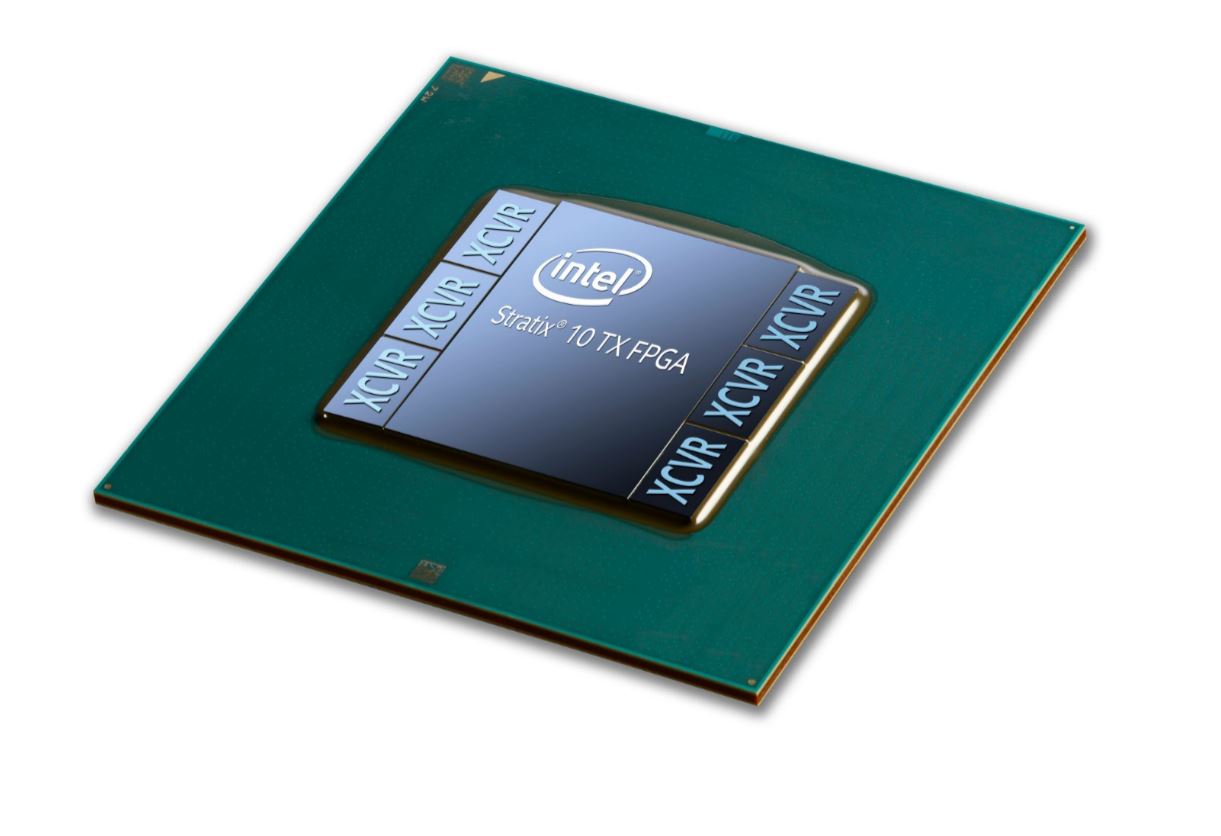

Intel Ships Stratix 10 TX FPGAs With 58G Transceivers

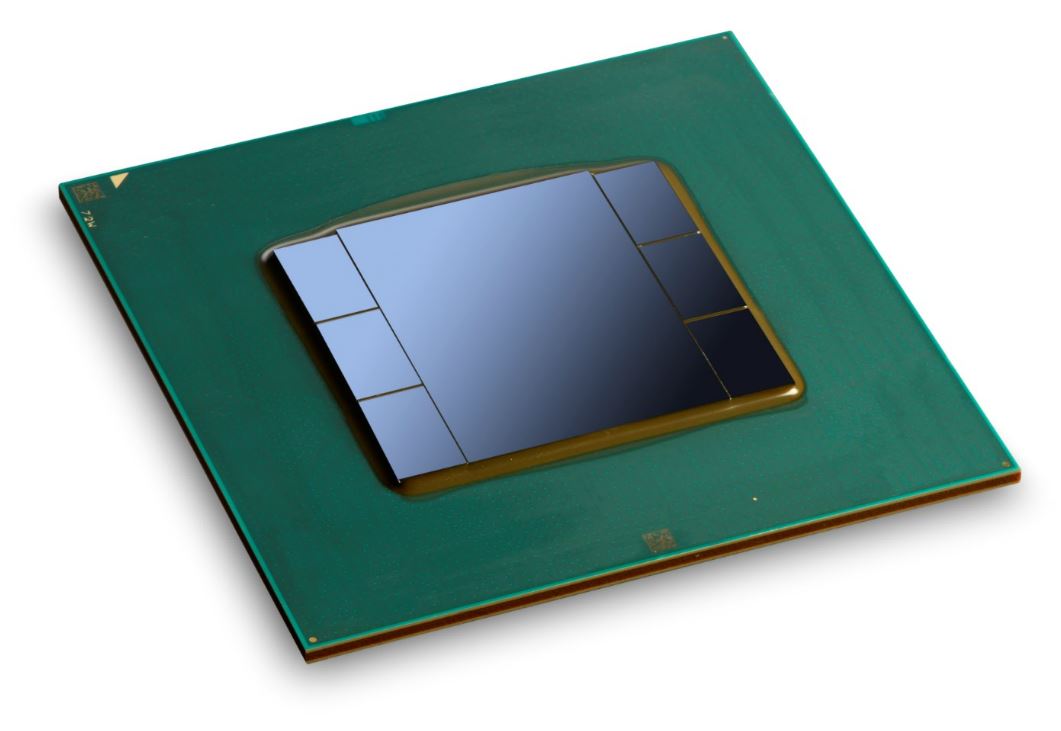

Intel announced its 14nm Stratix 10 FPGA is coming to market with 58G transceivers fabbed on TSMC's 16FF process. Intel's original Stratix 10 announcement brought us the first glimpse of the company's new EMIB technology that allows it to tie larger processors to "chiplets," which are small re-usable building blocks that can be processors, transceivers, memory, or other types of components. That approach allows Intel to mix-and-match features using a Lego-like building process. For instance, Intel uses transceivers fabbed on TSMC's process, and HBM memories from SH Hynix and Samsung, in tandem with its Stratix 10 FPGAs.

Intel's PSG (Programmable Solutions Group) uses the groundbreaking EMIB interconnect technology to create different classes of products in the Stratix 10 FPGA family with varying chiplet options. The GX models serve the general purpose market, SX models come with an integrated quad-core ARM processor, and the MX models come with options for integrated HBM.

Now Intel has added the Stratix 10 TX model for networking, network function virtualization (NFV), and 5G networks, among other uses. The TX FPGA employs up to six 58G transceivers chiplets per FPGA, which can also operate in 28G mode, in various configurations. The TX offers up to 144 transceiver lanes (24 lanes per transceiver). That enables 100G, 200G, and 400G delivery speeds. The Stratix 10 TX offers up to 2.7 million logic elements.

Article continues belowThe transceivers also support dual-mode modulation (PAM4 and 30G NRZ). With PAM4 modulation, the 58GbE transceiver doubles the number of bits in a transmission by sending two bits per clock edge, whereas 28GbE only sent one bit. That enables increased data transmission rates without increasing the frequency, thus assuring compatibility with existing 28G networking equipment (such as backplanes and switches). PAM4 does bring higher error rates, but FEC (Forward Error Correction) reduces the bit error rate to tenable levels. The transceivers also work in NRZ mode to operate at 28G and below, which is a unique feature for an FPGA. We aren't aware of a competing Xilinx product with a similar dual-modulation scheme. Intel also blended the same transceivers into an MX model that sports up to four transceiver tiles and two HBM chiplets.

Intel folded its Altera acquisition into its Programmable Solution Group, so many of the Stratix 10 design decisions, such as using ARM cores for the SX models, were made before Intel purchased the company. The FPGA uses Intel's 14nm FinFET process, but the Intel-designed 58G transceiver tiles use TSMC's 16FF process, which is an improvement from the 28nm TSMC process Altera used with the older 28G transceivers.

Intel will use its own 10nm process for the next-generation Falcon Mesa FPGAs, but it hasn't disclosed if it will use its own process node for the transceivers.

While it may seem counter-intuitive, Intel designed its EMIB (Embedded Multi-Die Bridge) technology specifically to enable it to use chiplets from other vendors. Intel has said that no single company has a monopoly on innovation, and some companies can create certain customized solutions that are better than their competitors. Building a single monolithic die requires a company to be the best at everything, whereas picking and choosing between chiplets from other vendors allows companies to focus on their core competencies. It also allows Intel to use components that don't scale well to smaller nodes, such as analog devices, in tandem with leading-edge processes. Using multiple chips from multiple vendors with different process nodes ultimately reduces cost and can lead to improved performance in some scenarios. Head to our EMIB deep dive for more detail.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Intel is now shipping the Stratix 10 TX FPGAs in volume.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.