Tom's Hardware's 2007 CPU Charts

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

AMD: Waiting For The Phenom

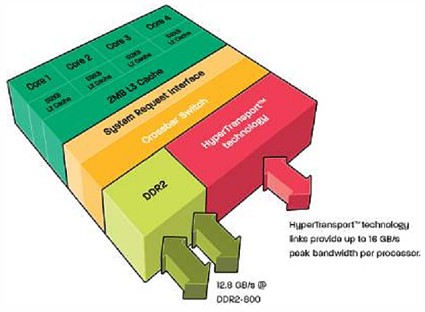

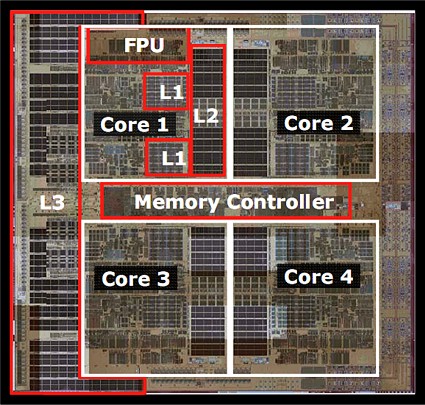

It has been an awfully long wait, because AMD is not ready with its Phenom processors, although it desperately needs them to compete with the Core 2. Several key details on the architecture beneath Phenom have been made public: it will be a native quad core on a die, as opposed to Intel's current approach of placing two dual core dies into one physical processor package. Native quad cores can exchange data and communicate internally, while composed quad cores have to use the system interface, which in case of the Intel Core 2 Quad is the Front Side Bus. Phenom X4 will have a three-stage cache design, consisting of a 64 kB L1 cache (32 kB instruction, 32 kB data) and 512 kB L2 cache per core, plus 2 MB shared L3 cache.

While Intel will rely on its Front Side Bus for another year, AMD can deploy its Phenom X4 processor either to existing Socket AM2 motherboards that comply to the power requirements, or to the accelerated Socket AM2+, which will feature HyperTransport 3.0 running at double the bandwidth. Despite being ready for 125 W AMD processors, not all existing motherboards will be capable of supporting the Phenom X4: with four cores clocking up and down, the voltage levels will fluctuate quite a bit, which I can imagine might be a source of problems. However, AMD points out that the quad core processors do fit into existing designs.

Phenom will also still use the integrated dual channel DDR2 memory controller. Compared to Intel platforms, where the memory controller still is part of the chipset core logic, an integrated unit is clearly more energy efficient and shows less latency. AMD will manufacture Phenom using its 65 nm DSL SOI process (dual stress layer, silicon on insulator), which is also being used for current 65 nm Athlon 64 X2 processors. Compared to Intel's strained silicon approach, SOI manufacturing is clearly more elaborate, while yielding less leakage and thus better energy efficiency.

AMD says it has also improved its branch prediction and out-of-order load execution algorithms, and upgraded the cores to support 128 bit SSE (which Core 2 does as well) and four dual precision floating point operations per cycle (which Core 2 does not). Several extensions and SSE additions complement the architectural updates. Let's hope that AMD can hold to its roadmap and ship the processors before Intel gets to speed up its 45 nm chips.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: AMD: Waiting For The Phenom

Prev Page Status Quo, Continued Next Page Intel: Core 2 Rules The Processor Arena

Patrick Schmid was the editor-in-chief for Tom's Hardware from 2005 to 2006. He wrote numerous articles on a wide range of hardware topics, including storage, CPUs, and system builds.