Intel Atom CPU Review

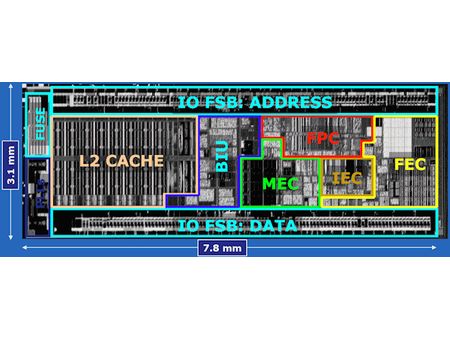

Atom: Caches and FSB

Intel has chosen a fairly out-of-the-ordinary organization for the Atom, but without sacrificing performance (which is important with a CPU using an in-order architecture).

24 kB + 32 kB: An Asymmetrical Cache

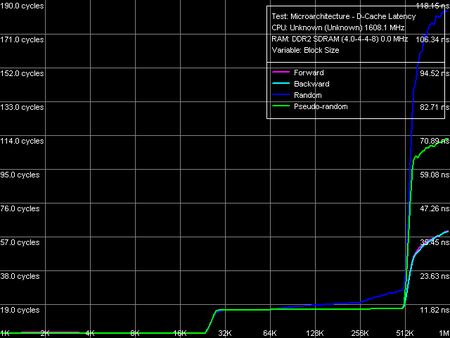

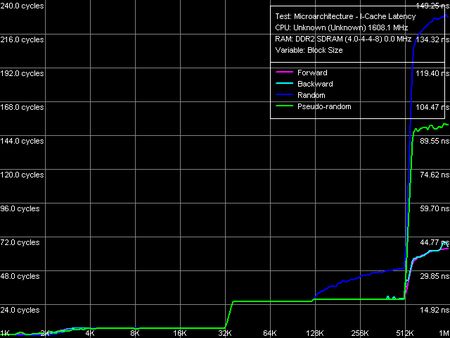

The Atom’s Level-1 cache is 56 kB total: 24 kB for data and 32 kB for instructions. This asymmetry, fairly surprising for Intel, stems from the structure of the cache. Intel uses 8 transistors to store one bit, compared to six transistors in a standard cache. This technique allows the voltage applied to the cache to maintain information to be reduced. It seems that this move to 8-transistor cells was made late in the game, when the design of the processor was fairly advanced, which meant that the size of the cache had to be reduced to fit it in – which explains the 24 kB for the data cache. This unofficial explanation was advanced by AnandTech in their article introducing the Atom in April.

512 kB Level 2, shrinkable

The Level-2 cache has a capacity of 512 kB, and obviously runs at the same frequency as the processor. This 8-way cache is fairly classic and is close in performance to the one used in the Core 2 Duo (its latency is 16 cycles, compared to 14 for the Core 2). One of the new functions can deactivate part of the cache automatically – if a program doesn’t require much cache memory, part of it can be shut down. In practice, the cache goes from 8-way to 2-way (thus from 512 kB to 128 usable kB). This technique is a way of shaving a few precious milliwatts.

The FSB: Two modes of operation

The Atom’s FSB is the same one used by Intel since the Pentium 4. It operates in Quad Pumped (QDR) mode with GTL signaling. An interesting point: The Atom uses another signaling technology – CMOS mode. GTL is effective (the bus can reach 1,600 MHz), but power-intensive, whereas CMOS allows the bus voltage to be reduced. Technically, GTL uses resistors to improve the quality of the signal, but they aren’t really necessary except at higher frequencies. With the Atom and its bus, limited to 533 MHz, it’s possible to change to CMOS mode – the resistors are deactivated and the bus voltage is reduced by half. At the moment, only the SCH chipset is capable of handling the FSB in CMOS mode.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: Atom: Caches and FSB

Prev Page Atom: In-Order and HyperThreading Next Page Power Management: Tests and Theory-

joefriday Celerons have significantly lower frequencies than Atom? umm...no. Only the ULV celeron M has a lower freqency. Modern notebooks start with Celerons at least 1.6GHz, more likely 1.86GHz, and are built on the much more modern Merom architecture, which have at least a 10% IPC advantage over the old Dothan architecture. No, atom is nowhere NEAR a modern Celeron in performance. Nice try though.Reply -

joefriday Also, Why not have a Celeron 420 by now? Are you telling me that THG, with all its money, can't budget in a $30 CPU for comparative testing?Reply -

joefriday After reviewing the article, I can say I'm thoroughly unimpressed with the Atom platform (at least the current desktop derivative). If anyone can remember, THG did a $300 PC build using now ancient Celeron Ds and AMD Semprons. One thing that I find amazing, is that those old rigs both use LESS power than this Atom desktop rig.Reply

http://www.tomshardware.com/reviews/the-300-pc,1546-10.html

-

randomizer Don't you people understand that Atom is not a desktop processor? You can't compare its performance to a desktop processor fairly because that's not what it is designed for.Reply -

joefriday This Atom CPU is on a desktop board. That means it's fair game, especially when the processors being compared are also comparable in price.Reply -

randomizer It's on a desktop board, woopdedoo. If you could get your mobile phone processor to run on a desktop board would you compare it to an E2160?Reply -

joefriday Who cares what the Atom CPU is SUPPOSED to be. It is right now, in this review, on a desktop-oriented package, built to compete with low power consumption desktop computers. It fails miserably in that regard, as it is neither low power consumption, nor competitive. In your ridiculous example, if I had a mobile phone processor on a desktop board, and it ended up consuming more power than an E2160/motherboard combo that costs the same amount of money, all the while performing much worse than the e2160, I would call the mobile phone cpu on a desktop motherboard either A FAILURE or AMD. Take your pick.Reply -

apaige So, for the Intel Atom, you do use an updated version of Sandra, but not for the Phenom. You compare it to the VIA C7, a 3 year-old CPU, but not the VIA Nano, which will be available in the same timeframe as the Atom. You don't provide graphics for power consumption, despite the Atom being designed for low power consumption; surprise, the old C7-M system draws less power.Reply

Biased much? -

Not sure that Nano's are really available yet, still a newer mini-itx based C7 (say EPIA-M700) would have been better, since you would be looking at even less power than the one used and the VX800 will end up used with the Nano. The D201DLY would have been good to compare to, would also give some idea how the Atom would go paired with SiS chipsets.Reply