PCIe 6.0 Spec Release Date on Track, Version 0.5 Announced

The final PCIe 6.0 spec's release date is reportedly on schedule for 2021.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Although AMD has already implemented PCIe 4.0 across a range of mainstream products with its Ryzen 3000-series processors and latest graphics cards, Intel is still stuck on PCIe 3.0, having canceled its plans for PCIe 4.0 on Comet Lake. Meanwhile, PCI-SIG, which makes the PCIe specifications, announced version 0.5 of the upcoming PCIe 6.0 spec today, which features eight times the bandwidth of PCIe 3.0.

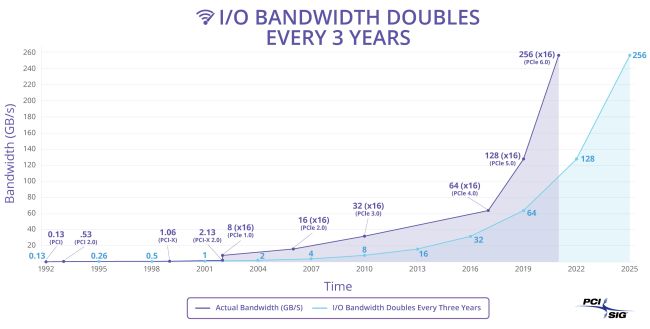

Even though we've yet to see products supporting PCIe 5.0, PCI-SIG first announced it'd be introducing a PCIe 6.0 spec in October. The spec's jump in bandwidth is no surprise, as each new generation of PCIe doubles the bandwidth of the previous. Where PCIe 3.0 has a bandwidth of 8 GTps per lane, PCIe 4.0 doubles that figure to 16 GTps, and PCIe 5.0 jumps to 32 GTps. Logically, PCIe 6.0 makes the jump to an impressive 64 GTps per lane.

- What Is PCIe? Here's a basic definition.

- Best graphics cards for gaming in 2020

Those figures translate to about 8 GBps per lane of PCIe 6.0, which for a 16-lane slot would equate to nearly 128 GBps per slot. Consequently, it wouldn't come as a surprise if the eventual arrival of PCIe 6.0 devices meant the days of full-length PCIe slots were numbered. The first sign of this was AMD's Radeon RX 5500 XT graphics card, which only needs 8 lanes thanks to PCIe 4.0 support.

Article continues belowThese figures are achieved by encoding with Pulse Amplitude Modulation with 4 levels (PAM-4). The specification also features low-latency Forward Error Correction (FEC) and will be compatible with all previous versions of PCIe.

According to PCI-SIG. the PCIe 6.0 spec is on track for delivery in 2021. That doesn't mean we'll be seeing products with it in 2021 though; it only means that hardware vendors will start developing supporting products.

The biggest areas that will benefit from faster PCIe, at least initially, are high-computing platforms, such as artificial intelligence and machine learning. It will likely take significantly longer before individual consumers start leveraging the increase in bandwidth.

PCI-SIG will share more details at its upcoming Developers Conference on June 3 and 4.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Niels Broekhuijsen is a Contributing Writer for Tom's Hardware US. He reviews cases, water cooling and pc builds.

-

TechLurker Given that AMD and Intel both mentioned plans to jump to PCIe 5.0 in 2021 onwards, I wonder if they will stay with PCIe 5.0 or jump to 6.0 another year or two later.Reply

While it makes sense to futureproof hardware, I wonder if it's more convenient to just have their CPUs "PCIe 6.0 ready" but on motherboards, split the bandwidth across more PCIe 5.0 or even PCIe 4.0 lanes. Bringing back the age of having up to 7 x16-sized slots on XL-ATX motherboards or more staggered 4 x16-sized slot motherboards (like the TRX40 Aorus Extreme; requiring 8-9 slots) and NVMe drives between the slots.

For one, I recall that PCIe 4.0 is already expensive due to needing to add whatever signal repeater chips are necessary to get full slot coverage, which was something that limited full PCIe 4.0 to X570 and TRX40 motherboards while B550A and B550s will supposedly only have the first M.2 and PCIe x16 slot at 4.0.

For another, while AMD has ignited a fire under makers of PCIe-based add-on cards to innovate for PCIe 4.0, it's still going to be a long time before any can really make full use of that bandwidth, so downgrading CPU-based PCIe 5.0 or 6.0 to 4.0 but adding more slots seems like a reasonable middle ground. -

bit_user Reply

If they continue having a separate I/O die, then desktop CPUs won't just inherit PCIe 5.0+ "for free".TechLurker said:I wonder if it's more convenient to just have their CPUs "PCIe 6.0 ready" but on motherboards, split the bandwidth across more PCIe 5.0 or even PCIe 4.0 lanes.

As you rightly point out, faster interconnect speeds is a costly proposition. I don't see it coming to desktops, though it'd be interesting if they upgraded the CPU <-> chipset with a PCIe 5.0 or PCIe 6.0 link. As you point out, that could enable more/wider/faster chipset-connected slots. -

srimasis So is it possible to have proper SLI or Crossfire with pcie 6.0 without any bridge since GDDR6 bandwidth is 72 GBps and pcie 6.0 bandwidth is 128 GBps. I hope to see proper dual gpu compatibility like having two 8gb GPUs combination would act as one 16gb GPU.Reply -

InvalidError Reply

72GB/s for GDDR6? For a RX5700XT that's 16GT/s x 256bits = 512GB/s.srimasis said:So is it possible to have proper SLI or Crossfire with pcie 6.0 without any bridge since GDDR6 bandwidth is 72 GBps and pcie 6.0 bandwidth is 128 GBps.

Even if mainstream CPUs got PCIe6, it would still be split x8x8 so you lose half the bandwidth there. Then you also lose performance to the GPU-bus-host-bus-GPU-bus-host-GPU roundtrip and other overheads inherent to accessing remote memory pools.

If you want to make multiple GPUs behave like a single larger one, you'll need even more bandwidth and lower latency than that to account for all of the other internal processes that require bandwidth too but never have to leave the die in single-GPU setups. -

bit_user Reply

FWIW, I guess AMD is using lower-clocked GDDR6 than wherever that 72 GB/s is from, because the rated spec of RX 5700XT is 448 GB/sec. That detail aside, I agree with your basic point, which seems to be that one needs to look at the bandwidth for the whole GPU.InvalidError said:72GB/s for GDDR6? For a RX5700XT that's 16GT/s x 256bits = 512GB/s.

Yeah, I think latency is a killer. That is, if you want to use multiple GPUs to reach really high frame rates.InvalidError said:If you want to make multiple GPUs behave like a single larger one, you'll need even more bandwidth and lower latency than that to account for all of the other internal processes that require bandwidth too but never have to leave the die in single-GPU setups.

However, if you're trying to use multiple older or lower-end GPUs to make a game barely playable, then I think multi-GPU setups are potentially a lot more interesting. -

TechLurker Replybit_user said:If they continue having a separate I/O die, then desktop CPUs won't just inherit PCIe 5.0+ "for free".

As you rightly point out, faster interconnect speeds is a costly proposition. I don't see it coming to desktops, though it'd be interesting if they upgraded the CPU <-> chipset with a PCIe 5.0 or PCIe 6.0 link. As you point out, that could enable more/wider/faster chipset-connected slots.

Using AMD as an example; I meant something like a theoretical "6000" or "7000" series Ryzen/TR CPU having PCIe 6.0 on-die, but motherboards outside of specialized Enterprise/Commercial downgrading that to PCIe 5.0 or even 4.0 bandwidth to allow for more slots while still providing some future-proofing via future motherboards (easier on AMD with socket sharing over 3-4 chipset generations, questionable on Intel).

Especially since by the time PCIe 6.0 becomes an actual adopted thing, 4.0 and 5.0 signal repeaters will likely have come down in costs some due to aggressive adoption by AMD and Intel down to the consumer level, or advances in material design would be advanced enough allowing for boards not needing as many (or not needing any) repeaters for 4.0 or 5.0 traces, making them cheaper than what's needed for 6.0. And further, no company yet has any consumer-level way of actually saturating PCIe 4.0, much less 5.0, and unlikely will for at least another 5-10 years.

On the middle/mainstream end of motherboards (B-series on AMD), we could maybe even see an on-die PCIe 6.0 downgraded further to mostly PCIe 3.0, for all slots except the 1st M.2 and GPU slot. So maybe PCIe 4.0 M.2 and x16 slot, and the remainder x16 or x8 full-length PCIe 3.0 slots. Low end motherboards (AMD A-series mobos) may see the 6.0 downgraded to all 3.0 but sufficiently useful for those "porting over" older systems that still rely on older PCIe 2.0 and 3.0 cards (specialized audio and video cards, old networking cards, etc) and providing full x16 across several slots. -

bit_user Reply

5.0 needs retimers. As I'm not an electronics engineer, I can't comment on the potential for cost reductions, but they'll never cost as little as not having any.TechLurker said:Especially since by the time PCIe 6.0 becomes an actual adopted thing, 4.0 and 5.0 signal repeaters will likely have come down in costs some due to aggressive adoption by AMD and Intel down to the consumer level

One of the articles below puts the cost of PCIe 4.0 x16 retimers at $15 to $25 (parts cost - not final selling price). Presumably, PCIe 5.0 retimers would cost even more, given the need to run at double the frequency. Of course, adding any components has its own costs in terms of assembly and possibly board layer count.

You mean like room temperature superconductors? That would indeed be a game changer.TechLurker said:or advances in material design would be advanced enough allowing for boards not needing as many (or not needing any) repeaters for 4.0 or 5.0 traces

Short of that, I don't really see how material design can have an impact. With so many decades of R&D having already gone into PCB technology & design techniques, I find it hard to believe there are still potential refinements big enough to avoid the need for retimers, or even reducing board costs & complexity to the level we currently have with PCIe 4.0 boards.

For more on the added costs & technical challenges posed by PCIe 5.0, it's best to have a look at the electronic design trade publications. These articles are aimed at the design engineers tasked with using these technologies in real products.

https://www.planetanalog.com/signal-integrity-challenges-set-to-explode-in-servers-with-pcie-5-0/https://www.eetasia.com/news/article/18061502-pcie-45-higher-bandwidth-but-at-what-cost

I will say the discussion of cables is interesting. If there would be a sufficient need for the bandwidth, that could be the way the industry goes.

The only possibility I'm seriously entertaining is PCIe 5.0 between the CPU and chipset, and only because the chipset is soldered and can be located near the CPU. Perhaps 6.0 could eventually follow, if there's a sufficient need to justify the additional complexity and power consumption.TechLurker said:On the middle/mainstream end of motherboards (B-series on AMD), we could maybe even see an on-die PCIe 6.0 downgraded further to mostly PCIe 3.0, for all slots except the 1st M.2 and GPU slot. So maybe PCIe 4.0 M.2 and x16 slot, and the remainder x16 or x8 full-length PCIe 3.0 slots.

It's hard to see a use case, though. NVMe SSDs already have faster sequential speeds than desktop users actually need. So, we'd have to see a stronger market demand for multi-GPU setups than I think we've seen, lately. -

mdd1963 Replyadmin said:The PCIe 6.0 spec doubles the data rate of the last generation.

PCIe 6.0 Spec Release Date on Track, Version 0.5 Announced : Read more

This should come in very handy... in about 2028.... -

USAFRet Just as a 386DX was "for server rooms only"...this too shall eventually trickle down to the consumer space.Reply

Eventually. -

bit_user Reply

IMO, perhaps more like 2038.mdd1963 said:This should come in very handy... in about 2028....