Computex: Nvidia declares war on Intel

Features

By

Omid Rahmat

published

Add us as a preferred source on Google

Get the Tom's Hardware Newsletter

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

By submitting your information you agree to the Terms & Conditions and Privacy Policy and are aged 16 or over.

You are now subscribed

Your newsletter sign-up was successful

An account already exists for this email address, please log in.

Subscribe to our newsletter

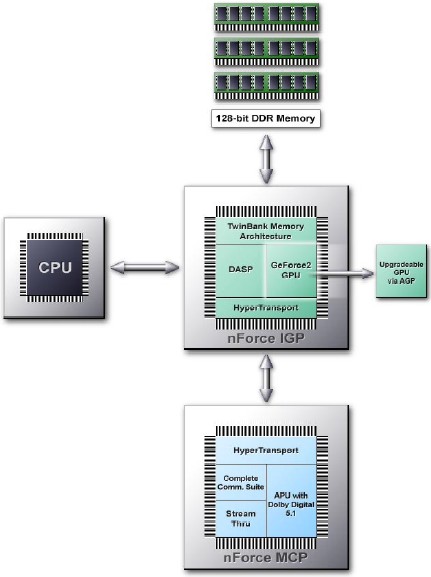

nForce Architecture

The nForce platform consists of three parts:

- A memory controller that can accesses to two banks of SDR or DDR SDRAM, thus sporting a 128-bit bit wide memory interface with a cross-bar configuration, which doubles the memory bandwidth as halves the memory latency of common SDR/DDR SDRAM solutions. The interface to the CPU also includes Nvidia's dynamic adaptive speculative pre-processor (DASP), which predicts, and pre-fetches data to improve the performance of CPU requests for data from memory. NVIDIA claims that nForce increases Athlon performance by up to 20%.

- The memory controller and DASP are housed inside the Integrated Graphics Processor (IGP) that also includes a GeForce2MX-style GPU, offering an integrated 3D-solution that is worlds apart from currently known chipsets with integrated 3D-graphics decelerators, such as Intel's i810, i815 or VIA's KM133.

- The Multimedia Communications Processor (MCP) is the connected to the IGP using a HyperTransport interface (8-bit wide, 400 MHz, differential), and houses the impressively featured Audio Processing Unit (APU - the audio from the Xbox including Dolby Digital 5.1 encoding), which comprises a sound unit several times as powerful as a Creative Live card. It also comes with a complete suite of networking and communications interfaces, including 10/100Base-T Ethernet and home phone-line networking (HomePNA 2.0).

The nForce architecture or, as Nvidia likes to call it, a distributed platform architecture. Tom's got plenty to say about it in his in-depth analysis coming soon.

Stay On the Cutting Edge: Get the Tom's Hardware Newsletter

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

No comments yet

Comment from the forums