Modular AMD Chips to Embrace Custom 3rd Party Chiplets

Supercharging learnings - and earnings - from the console space.

AMD is extending its custom chip design services even as it aims to offer a portfolio that's close and personal to its client's requirements. During its latest analyst day meeting, AMD Chief Technical Officer (CTO) Mark Papermaster spoke of recent advancements in semiconductor fabrication and chip interconnect technologies that would enable a modular future for the company's chip design. It seems that AMD might be looking at carving another strategy for the decades to come: something like "The Future is Custom."

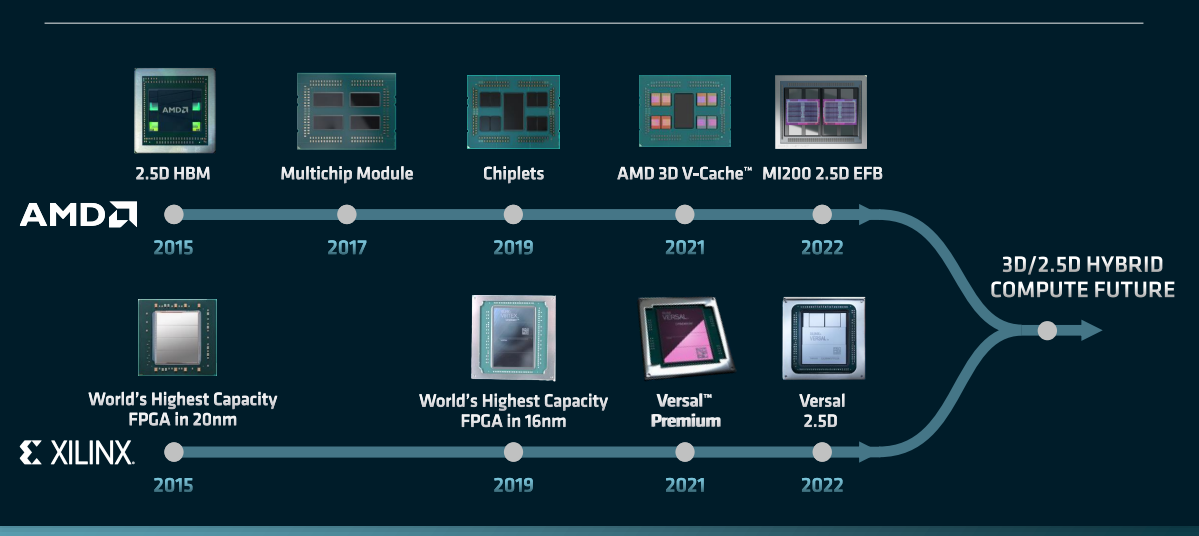

Building upon work that started with custom silicon designs for the Xbox 360 and PlayStation 4, AMD's Semi-Custom Solutions Division has quickly become one of the company's main strengths. AMD adapted its mainstream architectures according to Microsoft and Sony's power, performance, and cost requirements. Even Steam's runaway success, the handheld Steam Deck, has embraced AMD chip designs. But the company wants to take it further.

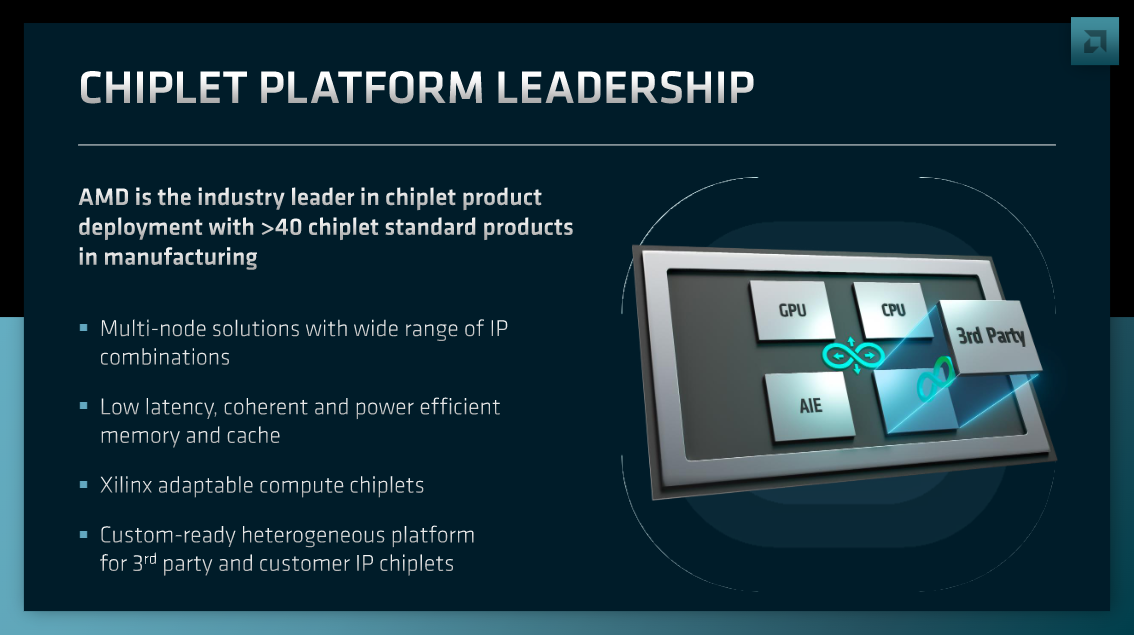

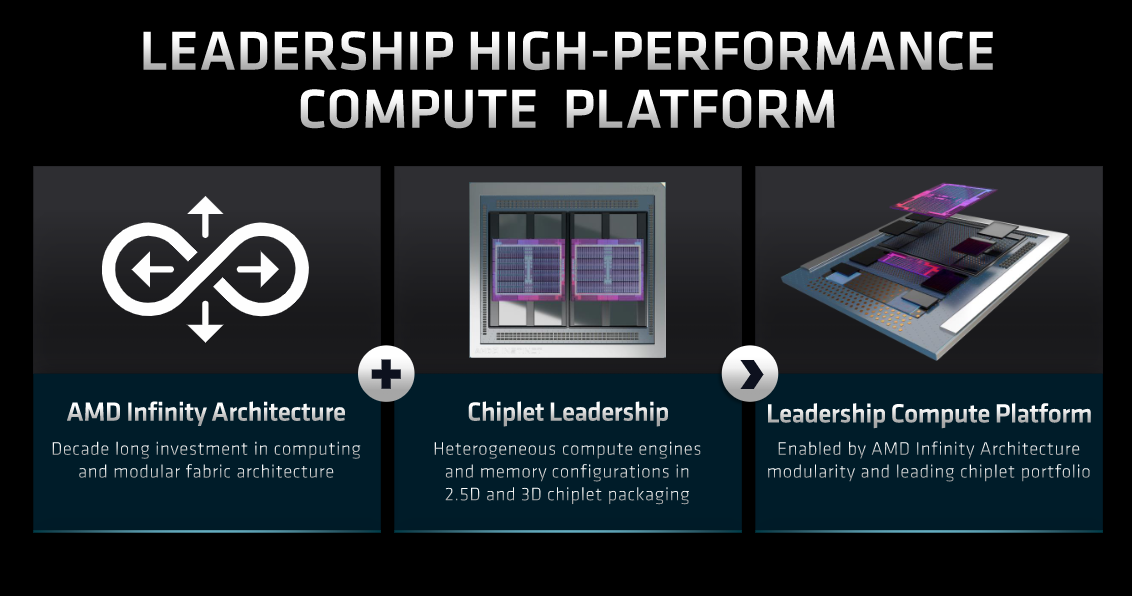

AMD's chiplet platform leadership

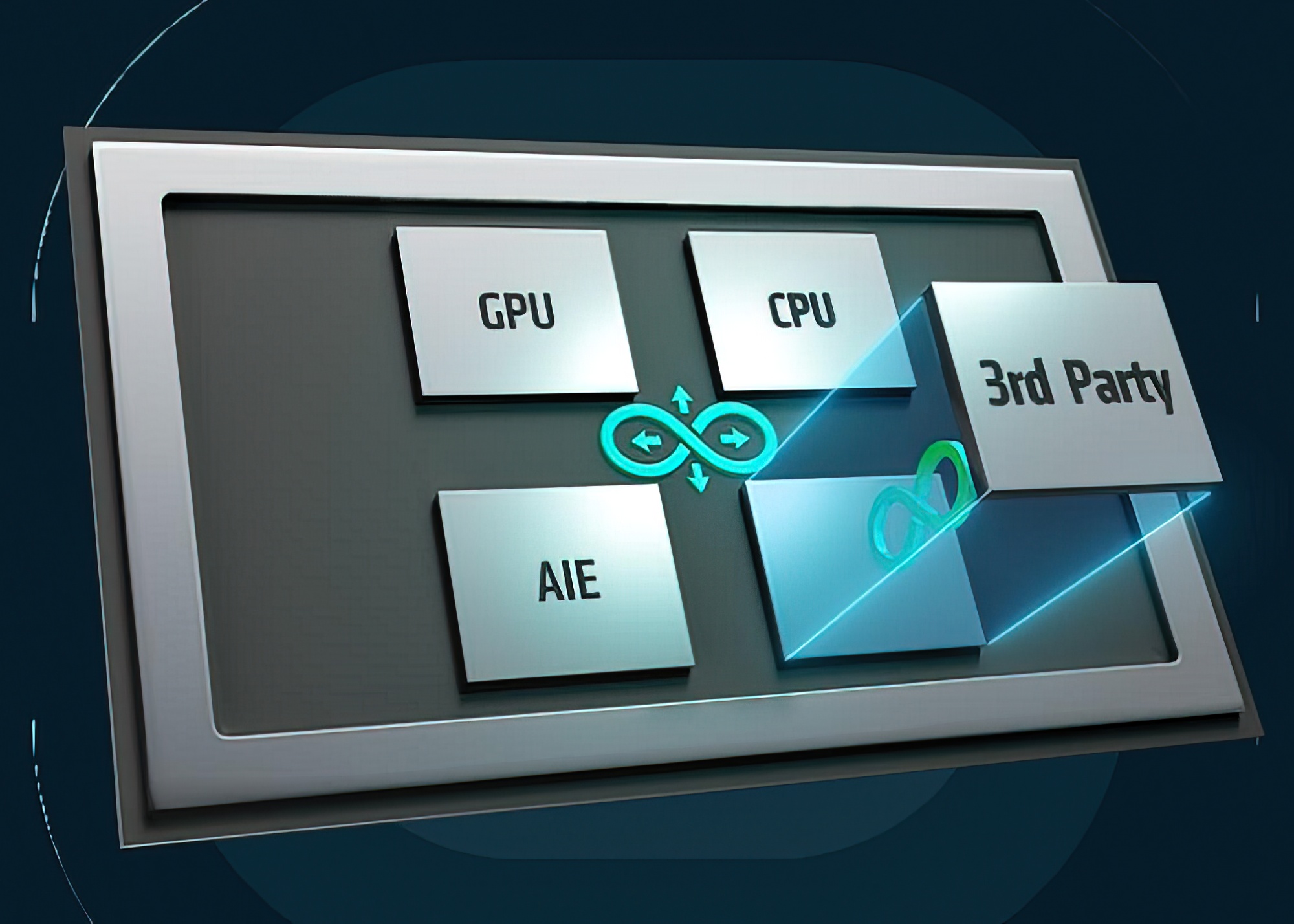

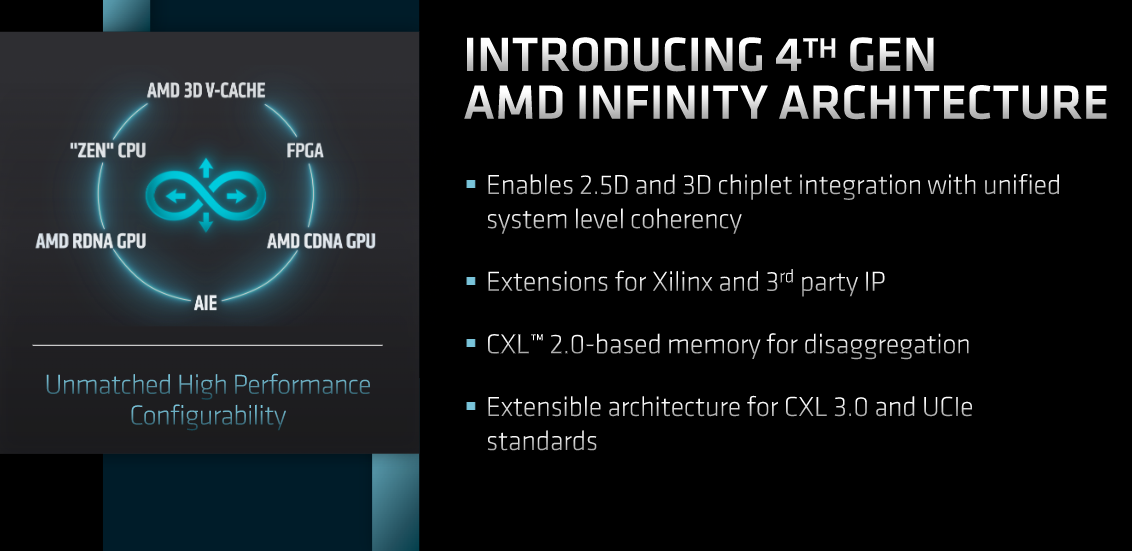

"We are focused on making it easier to implement chips with more flexibility," said Papermaster, who then expanded on the new philosophy by adding that customers would be invited to bring their own choice of chips towards a tile-like, manufacturable chip structure that can incorporate multiple chiplets wrapped up in a custom chip package. This means AMD customers would be able to pick and choose amongst the company's impressive IP portfolio - ranging from x86 CPUs, GPUs, Arm-based FPGAs through its merge with Xilinx, and even Arm-based networking chips from its Pensando acquisition - while also being able to deploy their own intellectual property.

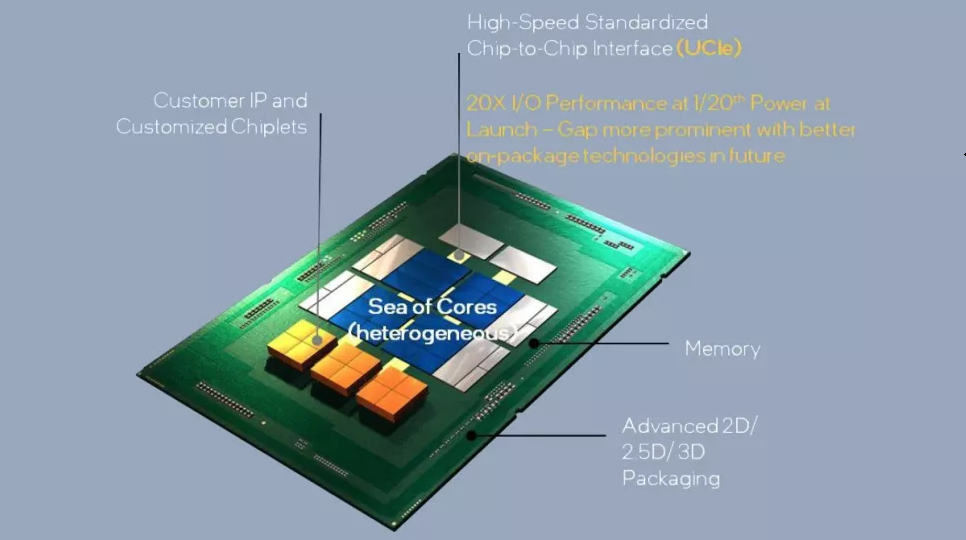

Article continues belowThe new strategy builds upon the recently-introduced Universal Chiplet Interconnect Express (UCIe) standard, which has garnered support from AMD, Intel, Arm, Google, Meta, and others. These companies see the future as an amalgamation of disparate, complementary IPs rather than what each player can singularly offer in-house. UCIe enables a standardized connection between chiplets, like cores, memory, and I/O, in both an in-die and off-die manner that enables performance and latency specifications that are high enough for HPC scaling while relying on well-known protocols like PCIe and CXL.

This makes sense considering the increasing prevalence of custom chip design - bolstered by royalty-free architectures such as RISC-V. Interestingly, RISC-V still hasn't integrated the UCIe standard. Nvidia hasn't either, but the company likely wants to push its proprietary NVLink interconnect as much as possible.

"We're going to make it much easier to add third-party IP as well as customer IP to that chiplet platform," said AMD CEO Lisa Su during the conference. "We've gotten a lot of positive customer engagement so far when you think about hyperscalers, when you think about 5G in automotive," she added. "These are big opportunities where people want to customize and we want to be their partner of choice."

AMD's chiplet-based approach to custom manufacturing is based on its strong relationship with TSMC and leverages the Taiwanese foundries' CoWoS (Chip-on-Wafer-on-Substrate) technology. The same is true for Apple's CoWoS-derivative UltraFusion interconnect. Nvidia's own Hopper GPU is also rumored to be based around that particular bit of TSMC's tech. AMD, naturally, will also be looking to leverage its Infinity Fabric 4.0 architecture, which has been developed for on-die connectivity and hyperscaling in HPC environments.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

AMD aims to lead in heterogeneous chip design

In what might be one of the most interesting tidbits regarding the future of computing, saying that the company is happy to be ISA (Instruction-Set Architecture) agnostic. Of course, it's easier to be agnostic when a company has the resources, licenses and engineering capabilities to have its feet firmly planted in both dominating and emerging architectures all at once. AMD is capable of this feat thanks to its nearly immaculate execution since Su became CEO.

It does mark a difference in stance compared to the walled garden approach historically preferred by chipmakers. To be fair, there's still a wall - there's a reason only AMD and Intel manufacture high-performance X86-x64 chips. But the gates are now ever so slightly ajar. In the meantime, we await the arrival of AMD's Ryzen 7000 processors and other new products on its consumer CPU roadmaps.

Francisco Pires is a freelance news writer for Tom's Hardware with a soft side for quantum computing.

-

dehjomz So this is similar in concept to intel foundry services that will allow developers to mix and match various ip on the same chip. So AMD chiplet services… and rather than having to manufacture the chip itself, on a node that may or may not be delayed or constrained in some other form, AMD can farm production out to TSMC.Reply

Seems like a very smart strategy. I wonder what types of IP blocks we’ll start to see on these custom chips? What would be the benefit, if any, of a chip with both arm and x86 cores? Wouldn’t windows and Linux need to be updated to fully account for and optimally utilize various types of cores spanning different ISAs on the same package? -

hotaru.hino Reply

I would argue operating systems are aware of this in a sense. For instance, the commands that games send to video cards to render something are actually microprograms called shaders. They get compiled by the drivers before being sent to the card to run.dehjomz said:Seems like a very smart strategy. I wonder what types of IP blocks we’ll start to see on these custom chips? What would be the benefit, if any, of a chip with both arm and x86 cores? Wouldn’t windows and Linux need to be updated to fully account for and optimally utilize various types of cores spanning different ISAs on the same package?

The OS wouldn't run on multiple ISAs, it'll just run on one and see the other as some other hardware to send executable data to if need be.