AMD announces 3nm EPYC Turin with 192 cores and 384 threads — 5.4X faster than Intel Xeon in AI work, launches second half of 2024

192 cores, 385 threads, socket compatibility. What's not to like?

AMD's hotly anticipated 5th-Gen EPYC Turin processors will launch in the second half of 2024, Lisa Su announced during her Computex 2024 keynote. The 3nm chips mark the debut of AMD's Zen 5 architecture for data center chips, and AMD claims they are up to 5.4x faster than Intel's competing current-gen Xeon chips in key AI workloads.

Turin comes in two variants: one with up to 128 standard Zen 5 cores and another using density-optimized CPU cores called Zen 5c — that model stretches up to 192 cores. Su also announced that AMD now has 33% of the data-center market.

The new Zen 5c-powered chips will feature up to 192 cores and 384 threads fabbed on the 3nm process node, then paired with a 6nm I/O Die (IOD) crammed into a single socket. The chip is comprised of 17 chiplets. The highest core count models utilize AMD's Zen 5c architecture, which uses density-optimized cores that are conceptually similar to Intel's e-cores. However, AMD pioneered this core type for x86 chips in the data center.

The models with standard full-performance Zen 5 cores come with 12 compute dies with the N4P process node and one central 6nm IOD die, for a total of 13 chiplets.

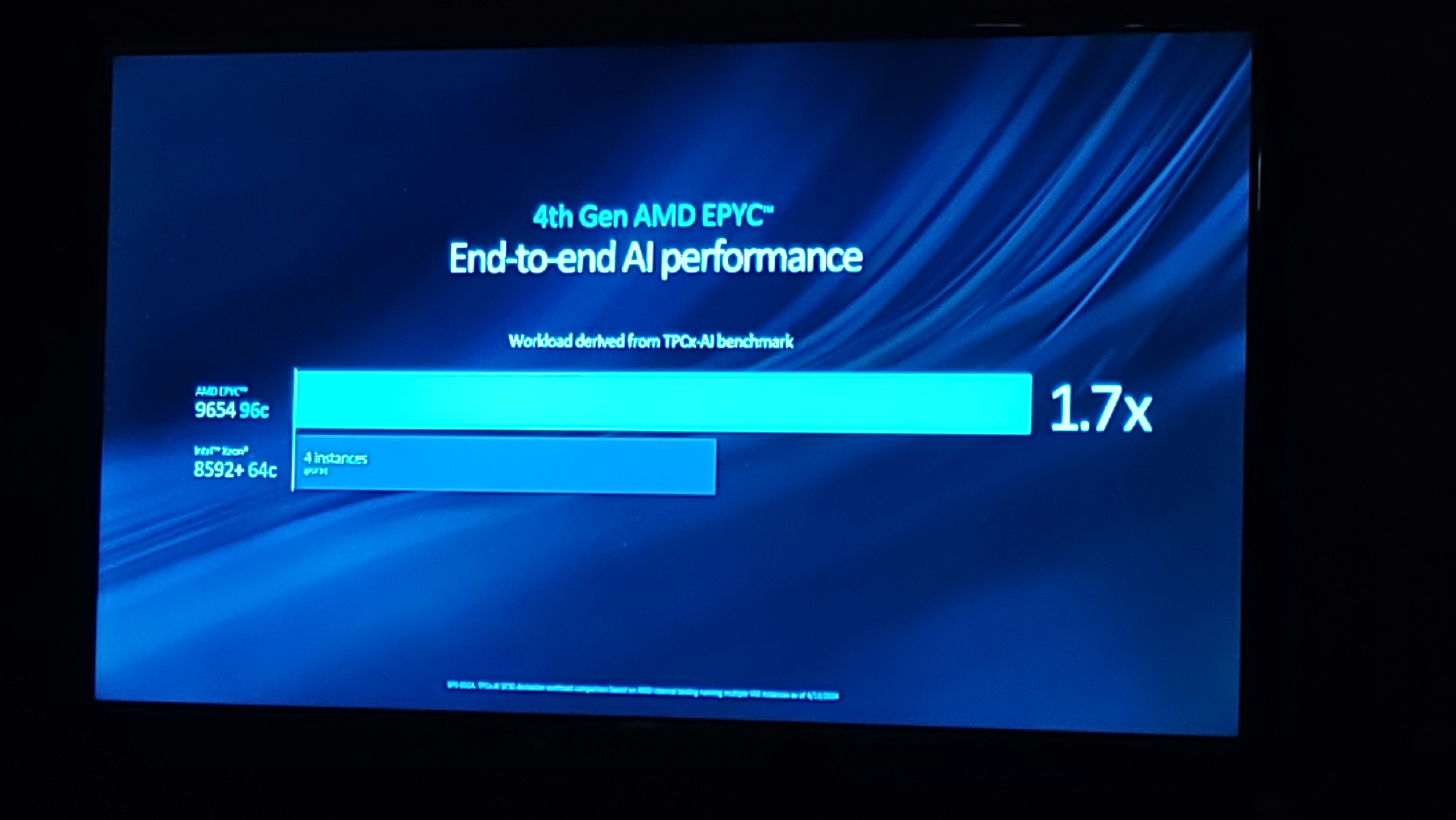

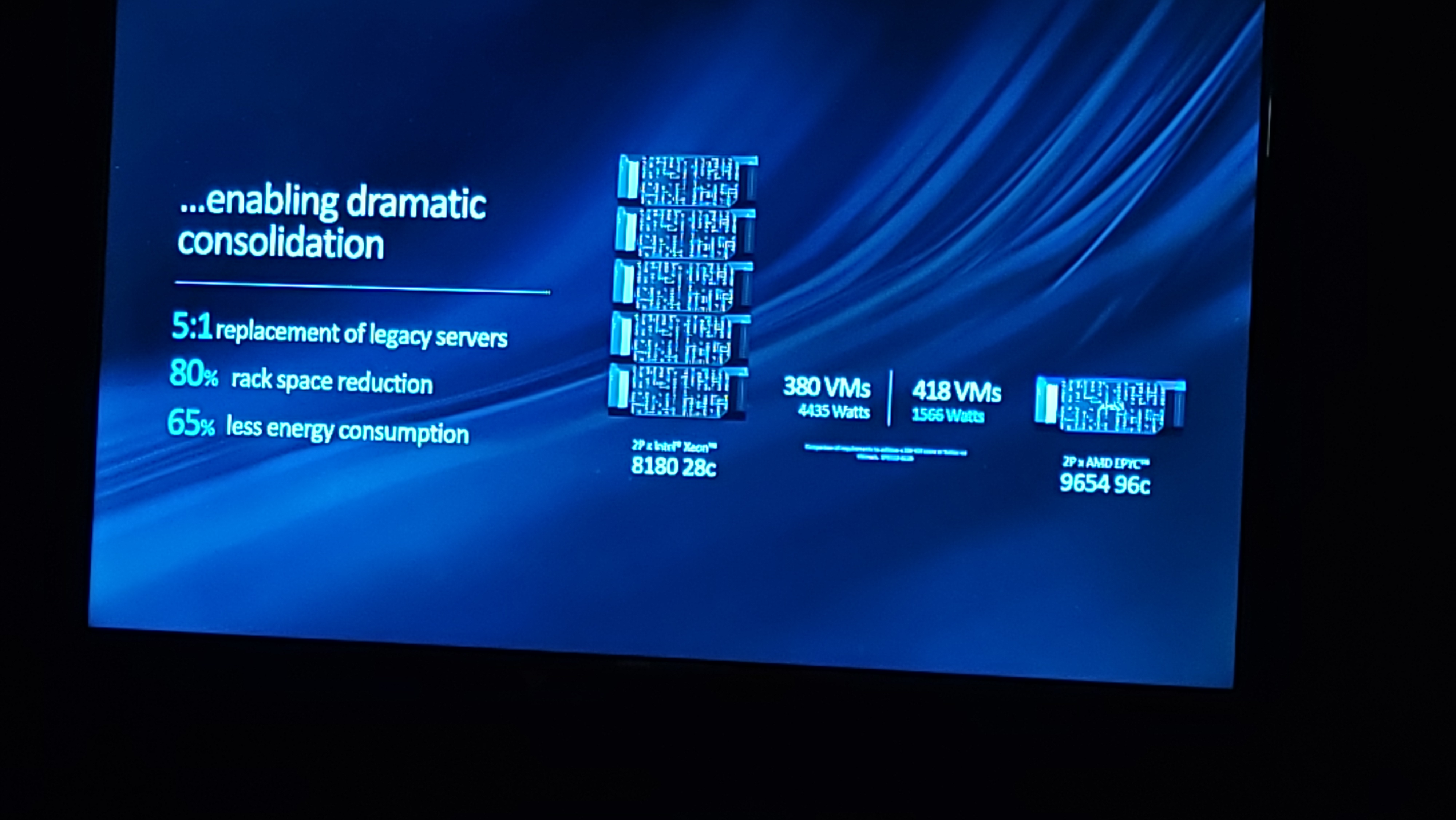

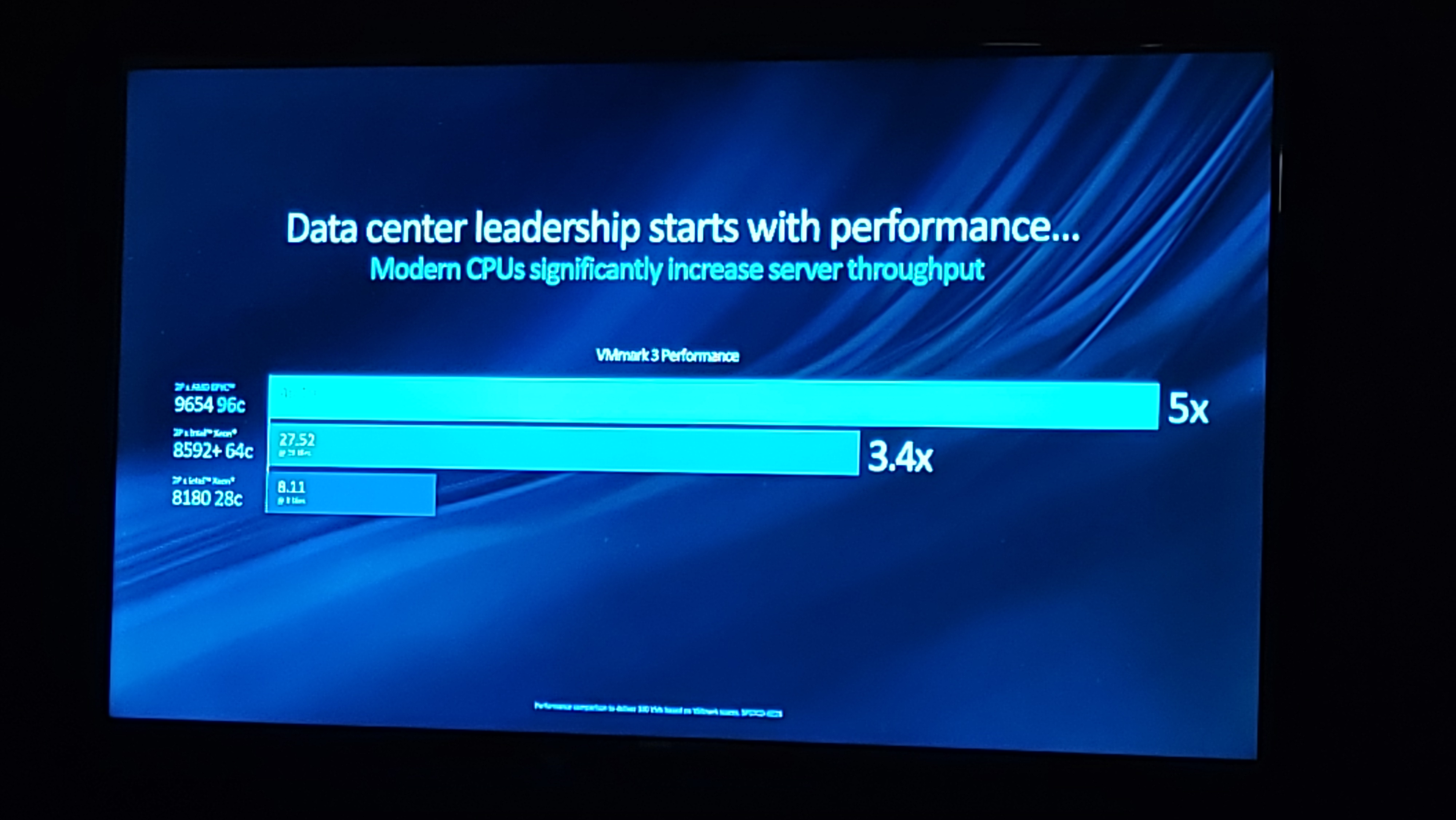

AMD displayed a spate of benchmarks against Intel's competing Xeon chips, but as with all vendor-provided benchmarks, take them with some salt. AMD claims an up to 5.4X advantage in an LLM AI model (chatbots) over Xeon, along with a 2.5X advantage in translation models and a 3.9X advantage in summarization work. AMD also showed a 3.1x advantage in the scientific NAMD workload with its 128-core Turin model and a live demo of Turin delivering 4X more tokens per second than Xeon.

The 192-core Zen 5c chips are the follow-on series to AMD's EPYC Bergamo, the industry's first x86 data center processor with density-optimized cores (Zen 4c). Bergamo tops out at 128 cores.

The 'standard' Turin models with the Zen 5 architecture stretch to 128 cores, marking a strong generational gain over the current-gen EPYC Genoa, which peaks at 96 cores.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

AMD's 192-core EPYC Turin chips are designed for the highest core density. They have an optimized Zen 5c core that halves the area needed for each core yet supports the same features as the full-fat Zen 5 cores, making them exceedingly attractive to hyperscalers (AMD says it owns 50% of this market segment).

The Zen 5c Turin chips will compete with Intel's 144-core Sierra Forest chips, which mark the debut of Intel's Efficiency cores (E-cores) in its Xeon data center lineup, and Ampre's 192-core AmpereOne processors, not to mention the custom silicon being developed or employed by Google and Microsoft.

Meanwhile, the standard Zen 5 EPYC processors will take on Intel's coming Xeon 6 lineup. Turin will drop into motherboards with the same SP5 socket used for 4th-Gen EPYC Genoa and Bergamo, allowing the existing kit to be simply upgraded to a drastically faster chip. This tactic also speeds quals on newer motherboards and servers, thus enabling a quicker time to market.

AMD also shared some benchmarks highlighting its claimed advantages in AI workloads with its existing 4th-Gen EPYC chips over competing Intel models. We expect more details to emerge as the Turin chips move closer to the market.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

hotaru251 AMD will never let Intel back in server performance at this rate.Reply

amd already onto next race while intel just crosses the finish line of last one. -

Here are some 20 Turin SKUs based on the Zen 5 & Zen 5C core architecture, branded under the EPYC 9005 family.Reply

The 192 core flagship part is missing here though, and since there's no mention of which of these SKUs are based on the Zen 5 or Zen 5c architecture, we can make some educated guess, also based on the L3 cache.

IMO, seems unlikely that there will be Zen 5c offerings above 128 cores, so 144-core and 160-core variants should stick with the Zen 5C architecture.

EPYC Zen 5C: Up To 192 Cores.

EPYC Zen 5: Up To 128 Cores.

EDIT:

The EPYC 9005 series branding was actually confirmed in a latest submission by AMD at SATA-IO.

https://sata-io.org/product/9044 -

bit_user Reply

Intel will allegedly counter with 128-core Granite Rapids and answer the 192-core/384-thread Zen 5c version with 288-core/288-thread Sierra Forest:hotaru251 said:AMD will never let Intel back in server performance at this rate.

amd already onto next race while intel just crosses the finish line of last one.

https://www.tomshardware.com/pc-components/cpus/leak-reveals-500w-fire-breathing-128-core-granite-rapids-xeon-6-cpu

I'm not saying Intel will match AMD in perf/W, this generation, although it's going to be Intel 3 vs. TSMC N4 N3B (?). So, even if they don't completely catch up, they should at least have narrowed the gap quite considerably. -

thestryker This ought to be the most interesting enterprise level has been since Zen 2 based Epyc launched. Interesting to see how well AMD has optimized Zen 5 that they didn't need to jump to N3 for the standard CCDs which undoubtedly helps the financial side of things.Reply -

dalek1234 "AMD's Zen 5c architecture...density-optimized cores that are conceptually similar to Intel's e-cores"Reply

No, they are not. Intel castrated their cores to make them smaller. AMD packed the transistors closer together and reduced cache size. From instruction stand point, Zen 5 and Zen 5c are identical, which is not the case with Intel's e-cores (Also refereed to as Garbage Cores) -

abufrejoval Reply

Castration takes something away that was originally there. Not the case with e-cores, they are a distinct design for the same ISA, sometimes with a subset (still no castration).dalek1234 said:"AMD's Zen 5c architecture...density-optimized cores that are conceptually similar to Intel's e-cores"

No, they are not. Intel castrated their cores to make them smaller. AMD packed the transistors closer together and reduced cache size. From instruction stand point, Zen 5 and Zen 5c are identical, which is not the case with Intel's e-cores (Also refereed to as Garbage Cores)

Yes, turning off the AVX512 IP blocks on Alder Lake P-cores probably qualifies as castration.

And for the AMD compact core approach, a half sized cache might actually fit your use of "castration" and result in significant penalties for cache sensitve workloads. That's why hyperscalers will carefully test and tune.

But the genius is that a lot of the silicon surface area which has to be left dark for cooling on top-clock desgns, can instead be filled with logic on a design with lower max-clocks, resulting in less area waste.

Or well, it would be genius, if it wasn't quite simply what Ampere and similar hyperscaler specific designs had already been doing first.

If now they could only make chips switch between those two personalities on the fly!

And I guess dynamically disabling/not using hyperhreading to gain some clocks would get you half way there? -

bit_user Reply

FWIW, I'd characterize it as a different solution to the same problem of trying to increase compute density and efficiency.dalek1234 said:"AMD's Zen 5c architecture...density-optimized cores that are conceptually similar to Intel's e-cores"

No, they are not.

If we're nit-picking, I wouldn't even say that. What they did was to use a fundamentally different core design, from a completely different lineage.dalek1234 said:Intel castrated their cores to make them smaller.

https://en.wikipedia.org/wiki/Intel_Atom

AMD actually had their own lineage of E-cores, but that ended with the advent of Zen.

https://en.wikipedia.org/wiki/Puma_(microarchitecture)

At the expense of clockspeed, which explains why they weren't so densely-packed in the non-C version. That's a big reason why the C-cores are smaller - possibly even bigger than the cache reduction.dalek1234 said:AMD packed the transistors closer together and reduced cache size.

They're not garbage. They offer good compute density, which is what they were designed to do. You might disagree with how they were used in a particular product line, but that doesn't make them outright garbage.dalek1234 said:From instruction stand point, Zen 5 and Zen 5c are identical, which is not the case with Intel's e-cores (Also refereed to as Garbage Cores) -

frogr Reply

Actually it is granite rapids on intel 3 with E cores vs AMD on TMSC 3nm with 5c coresbit_user said:Intel will allegedly counter with 128-core Granite Rapids and answer the 192-core/384-thread Zen 5c version with 288-core/288-thread Sierra Forest:

https://www.tomshardware.com/pc-components/cpus/leak-reveals-500w-fire-breathing-128-core-granite-rapids-xeon-6-cpu

I'm not saying Intel will match AMD in perf/W, this generation, although it's going to be Intel 3 vs. TSMC N4. So, even if they don't completely catch up, they should at least have narrowed the gap quite considerably.