China-based firm delivers its first chipmaking tool that stamps nanoscale processor designs onto wafers — Prinano's nanoimprint lithography tool uses quartz molds engraved with circuits

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Prinano Technology, a China-based developer of nanoimprint tools, has delivered its first semiconductor-grade step-and-repeat nanoimprint lithography system to a Chinese customer that is focused on specialty process technologies. Instead of using traditional light-based lithography techniques, this type of chipmaking tool 'stamps' a chip design onto the wafer with a quartz mold that's imprinted with the circuit design.

Prinano's PL-SR-series machine is the first nanoimprint lithography tool (NIL) developed in China and set to be used for actual chip production once it passes all necessary tests at Prinano's client. Prinano is the second company in the world to deliver an actual nanoimprint lithography tool to a customer after Canon.

China's NIL tool seems to work

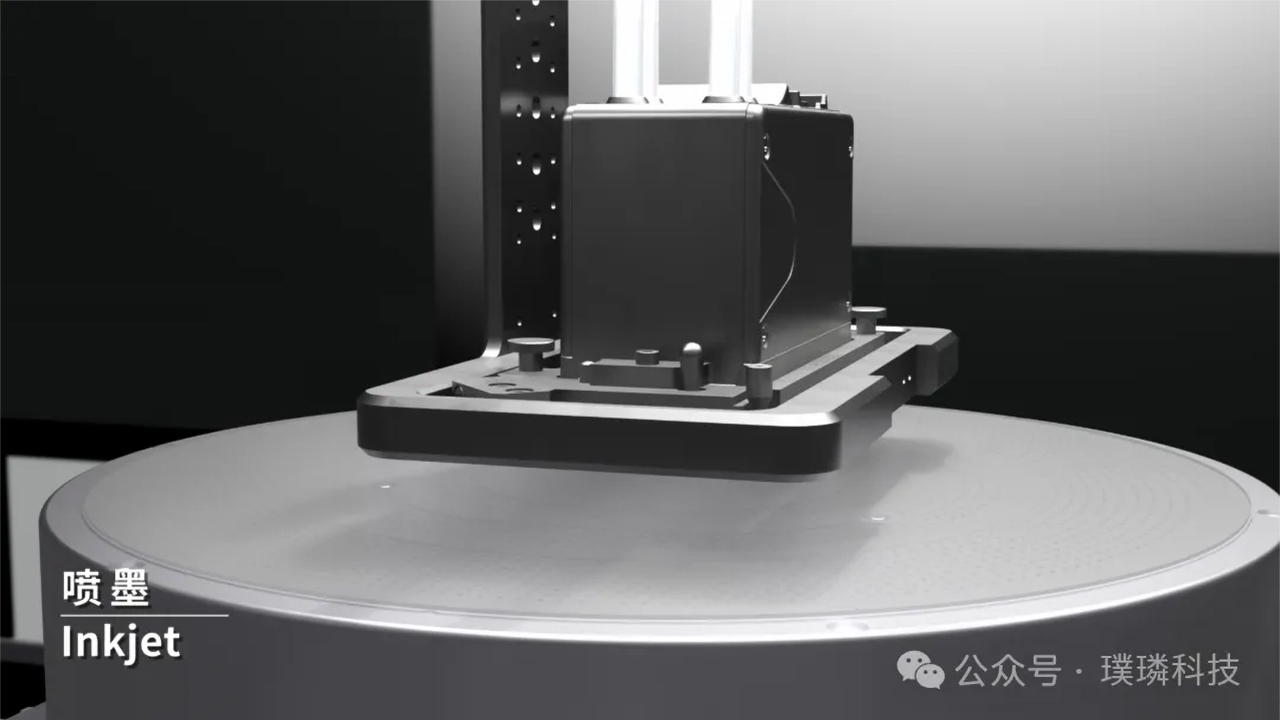

Prinano's PL-SR step-and-repeat nanoimprint lithography tool patterns wafers by physically pressing a rigid quartz mold engraved with nanoscale circuit designs into a thin layer of liquid resist deposited on the wafer surface. Instead of using light and projection optics like photolithography, the PL-SR directly replicates the mold's features at full scale. It applies the resist using a high-precision inkjet system that dynamically adjusts droplet volume for different pattern densities to ensure a thin, uniform residual layer (under 10nm, with less than 2nm variation).

Article continues belowPrinano's PL-SR system processes 300mm wafers and achieves less than 10nm linewidth capability. During operation, the system aligns the mold and wafer to presumably sub-10nm precision, makes full contact without a vacuum, and imprints each field sequentially (which is why it is called a 'step-and-repeat' system), stitching them together to cover the full 300mm wafer.

The machine features a proprietary template profile control mechanism — an important innovation for NIL — that promises to compensate for curvature mismatches between the rigid quartz mold and silicon wafer to enable transfer of features with aspect ratios over 7:1 without any distortions to maximize yields and reduce performance variations. After imprinting, the resist pattern is cured and later etched to form the final circuit structures.

With good results

While we cannot directly compare the NIL lithography machine with EUV tools, its linewidth capability can be compared to the resolution enabled by EUV scanners. Modern EUV systems with 0.33 NA optics operate at a 13.5nm wavelength and typically achieve 13nm minimum half-pitch in a single exposure, which is good enough to print a 26nm minimum metal pitch with a single exposure patterning.

To achieve resolutions below 10nm (e.g., printing 3nm-class process technology features at 21nm – 24nm), EUV tools necessitate multiple patterning steps, thereby adding cost and complexity. NIL's single-step reproduction of sub-10 nm lines is potentially simpler than EUV’s multipatterning for the same size, but only if the quartz mold can be manufactured with matching accuracy and defects can be kept low.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

As for <10nm residual layer thickness with less than a 2nm variation, EUV lithography (EUVL) scanners do not create a 'residual layer' in the same sense as nanoimprint lithography systems, but it makes sense to compare these dimensions to EUV's critical dimensions uniformity (CDU). Modern EUVL tools achieve CDUs within 1nm – 2nm across the wafer, so in this sense, NIL and EUVL systems are similar.

Prinano does not disclose overlay performance of its NIL tools, but its whitepaper about the tool says that the 'industry requires' overlay accuracy 'below 10 nm, and even approach the 1nm level' in the future. The latest ASML Twinscan NXE:3800E can achieve overlay performance in the range of 1.5nm – 2.0nm for high-volume manufacturing, depending on process conditions. Considering that Prinano does not directly disclose its overlay accuracy, we can only speculate that its target for now is between 1nm and 10nm.

But not for high-volume output

But competitive resolution is only one part of the equation. One thing to keep in mind is that NIL step-and-repeat imprinting is inherently slower than EUV or DUV projection lithography because each wafer field must be physically contacted, imprinted, cured, and separated before moving to the next. This mechanical cycle limits wafer-per-hour rates to the tens for fine features, whereas modern EUV tools can process around 200 wafers per hour. The slower pace makes NIL less suited for high-volume, leading-edge logic or memory production, even if its resolution is competitive.

And not for logic (at least for now)

Prinano says that initial validation of PL-SR has been completed for applications in memory chips, silicon-based microdisplays, silicon photonics, and advanced packaging. That said, it does not look like PL-SR will be used for logic manufacturing for the time being. The company does not disclose reasons for this, but given that it mentions applications that use mostly regular structures and no intricate circuits common for CPUs or GPUs, it looks like there are technical limitations for this.

NIL relies on printing IC features by physically touching a resist-coated wafer using a mold. This means that any particle or surface contamination can damage the mold and cause yield loss. With chips featuring loads of regular structures it is possible to implement redundancy without substantial increase of costs, but this is much harder to do with intricate logic, so any imperfection can be a yield killer. In fact, NIL's contact nature makes ultra-low defect rates harder to achieve consistently.

Follow Tom's Hardware on Google News to get our up-to-date news, analysis, and reviews in your feeds. Make sure to click the Follow button.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

IBM296 Ehh not bad. But until this system can be used for CPU and GPU manufacturing, it doesn't do much to help China's chip companies.Reply -

bit_user Reply

This is a key point, isn't it?The article said:only if the quartz mold can be manufactured with matching accuracy and defects can be kept low.

Also, talking about line widths, I think I read that Intel's old Fin FET node (maybe even 22 nm?) had just an 8 nm fin pitch. The way they accomplished this was by a chemical process to erode that fin layer. So, I get kind of lost when different pitches and feature sizes are being compared, TBH. -

stoatwblr If the machines are cheap enough then using multiples will make up the throughput difference. EUV machines are hideously expensiveReply

Remember, it doesn't have to be perfect. "good enough" is sufficient if it's cheaper and/or faster and/or has lower running costs (which is a significant factor on EUV systems)

Time will tell if this is a viable method at scale but remember that 10nm is more than sufficient for a lot of electronics and too small for reliable ram or nand -

cerruti1881 Reply

But it helps the prototype, pre-massive production verification, and even small scale military use where chip yield and cost aren't that sensitive.IBM296 said:Ehh not bad. But until this system can be used for CPU and GPU manufacturing, it doesn't do much to help China's chip companies.