Qubits and The Number 42: 12th Annual Hot Chips Conference in Palo Alto

Powerful

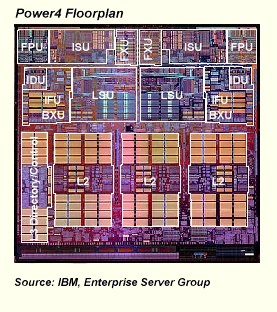

Back in the real world IBM has been working on the chip integration of their Power4 design. It is the first IBM chip that includes two processors and an L2 cache on the same die. Intended for the AS400 and RS/6000 server families, the Power4 can be used to create 32-way systems. Similar to its' predecessor, the Power3, the processor has two floating-point units per core.

IBM's Power4 chip has two processor cores and four floating-point units on the same die.

The Power4 is expected to run at a frequency of more than 1 GHz, and the die contains 174 million transistors. It is manufactured with 0.18 micron technology, features all-copper interconnects through seven layers of metal, and it is built using silicon-on-insulator (SOI) wafers.

According to a second paper presented at the conference, the Power4 will be able to communicate with other chips via a 500 MHz bus. The bus speeds of current designs are mostly at 100 MHz, slowly migrating to 133 MHz. IBM uses a technology called synchronous wave-pipelined interface to control and minimize the latency during the data transfer. Power4 is not in production yet, but it should be ready in 2001. Currently IBM has a test chip running in the lab.

Low Power

Transmeta, who just landed a deal with Sony, was also at the conference to announce their next-generation notebook PC microprocessor. CEO Dave Ditzel introduced the 700 MHz Crusoe TM5600, which offers twice the L2 cache than the previous TM5400 design. The package has the same pinout as the TM5400, however. The performance increases about 20 percent at the same frequency while at the same time consuming about 10 percent less power. Sony will use the Transmeta chip in selected models of its' popular Vaio notebook product line. Even though Sony has invested in Transmeta Corporation, and thus has a vested interest in its' success, the company says that the main incentive for using the Crusoe chip is its' low power consumption.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.