Silicon Motion SM2263XT HMB SSD Preview

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

Market Position & Specifications

The Silicon Motion, Inc. (SMI) SM2263 controller had a big presence at the 2018 CES trade show. Retail products should follow soon after the show, but you don't have to wait to see how the new controller performs. Today we look at the SM2263XT, the DRAM-less drive that will change the way we look at low-cost SSDs in 2018.

DRAM-less SSDs have a negative connotation, and we're not talking about the first-gen consumer SSDs that came to market in the mid-2000s. Those DRAM-less SSDs were bad enough, but the industry corrected those mistakes in just a few months.

DRAM-less SSDs began their resurgence in 2015. The first products were designed as low-cost alternatives to the HDDs sold in notebooks, but they later bled over to the retail upgrade market. Several companies tried to combat price increases during the NAND shortage with DRAM-less drives, but most shoppers were more inclined to carry over an older SSD to a new build or simply spend more for a higher-quality product.

Article continues belowWith a long history of failures to draw inspiration from, someone, somewhere, refuses to let this category die. Fortunately, the next iteration of DRAM-less design uses a new Host Memory Buffer (HMB) technology that should help DRAM-less SSDs finally succeed. Surprisingly, the magic ingredient used to make DRAM-less SSDs perform more like mainstream models is...DRAM.

Consumer DRAM-less SSD 3.0: Host Memory Buffer

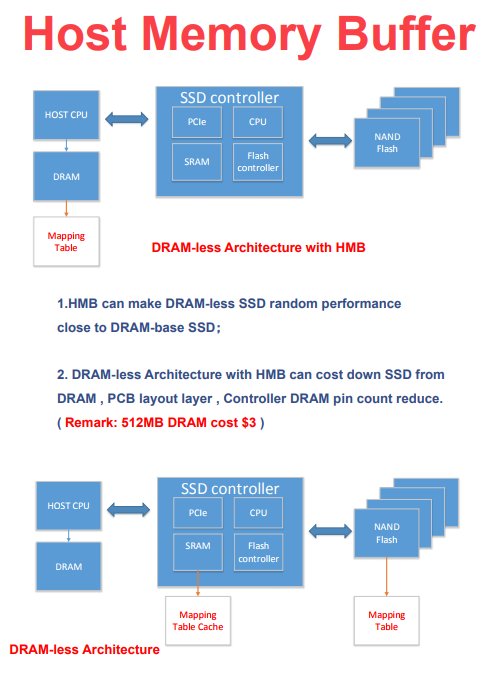

Today we will test the first Host Memory Buffer (HMB) drive to enter our lab. Before we dive into HMB technology, we have to define what cache is and how it pertains to solid-state drives. When most people think of cache, they imagine data passing through a high-speed memory on its way to a slower destination. User data does not actually pass through the DRAM cache in most SSDs, though. The DRAM holds a translation (mapping) table, which is a map of the abstracted addresses of the data stored on the NAND.

SSDs do not store data like hard disk drives, but the operating system expects them to. Flash-based devices do not place the data where the operating system requests because they need to spread wear evenly across the NAND. Essentially, the SSD has two maps of the LBA addresses: the logical map where the host "thinks" it is placing data and the physical map of where the SSD actually places the data. The SSD uses the translation table to find the stored data when the operating system issues read or write requests.

Flash is faster than disks, but both are slower than DRAM. Unfortunately, DRAM loses all its stored data as soon as you remove power. Losing the translation table can be devastating because it tells the SSD where it stored the data, but it's important to store the table in DRAM to speed up access, and thus SSD performance.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Modern SSDs hold a permanent copy of the table on the NAND, but it is often not the most up-to-date record because flash struggles with writing very small bits of data. For each update, the SSD would need to read the data in NAND, make a minor change, and then write an entire page back to the NAND. This process is slow and chews through endurance. Instead, the SSD stores the most up-to-date record of the map data in DRAM, and then periodically updates the copy on the flash.

The translation table is fairly large and grows based on SSD capacity. A 1TB SSD usually has a 1GB DRAM cache. For most consumer workloads, only a small portion of "hot" data changes often. DRAM-less SSDs cache the hot portion of the table inside the controller in a very small SRAM cache, but the SSD has to access the map in the NAND if the addresses aren’t readily available in the SRAM. We found in our testing that the small SRAM cache is not large enough for enthusiast workloads. That often results in slower performance than a hard disk drive.

HMB technology uses system memory (RAM) to cache the translation table. We've heard that one company uses 24MB and another company uses up to 128MB. In the future, we may need to look closer at the allocated space, but that is an area we will examine in individual product reviews. There currently isn't even a tool to see if HMB is enabled. Microsoft enables HMB automatically in the Fall Creator's Update, but it is not available with older versions of Windows.

Windows allocates much more system memory capacity to the translation table than the SSD has in the SRAM buffer, but it isn't as much as a dedicated DRAM module we usually find directly attached to an SSD controller. To compensate, the HMB SSD uses algorithms to detect hot data addresses and stores only the most frequently updated table data in the system memory.

Newer hardware and operating systems allow PCIe devices to flag data headed directly to system memory. Even though the system memory and PCIe bus are on opposite sides of the CPU, the flagged data passes through the processor without adding parasitic load. Even with the longer path, the system memory seems to do a good job of replacing on-device DRAM.

Specifications

| Controller | SM2263 | SM2263XT |

|---|---|---|

| Host Interface | PCIe 3.0 x4 | PCIe 3.0 x4 |

| PCIe Protocol | NVMe 1.3 | NVMe 1.3 |

| Package | 288-Ball TFBGA (12mm x 12mm) | 288-Ball TFBGA (12mm x 12mm) |

| NAND Flash Channels | 4 | 4 |

| CE/Channel | 4 | 4 |

| NAND Support | ONFi 3.0 / 4.0Toggle 2.0 / 3.0NV-DDR3 to 667MT/s | ONFi 3.0 / 4.0Toggle 2.0 / 3.0NV-DDR3 to 667MT/s |

| DRAM Interface | DDR3, DDR3L, LPDDR3, DDR4 | DRAM-less |

| Sequential Read | 2,400 MB/s | 2,400 MB/s |

| Sequential Write | 1,700 MB/s | 1,700 MB/s |

| Random Read | 300,000 IOPS | 280,000 IOPS (HMB)140,000 IOPS (No HMB) |

| Random Write | 250,000 IOPS | 250,000 IOPS |

| Security | Real-Time FDE With AESTCG Opal ProtocolHardware SHA 256 and TRNG | Real-Time FDE With AESTCG Opal ProtocolHardware SHA 256 and TRNG |

Both SM2263 variants sport impressive performance numbers. Our focus today is on the SM2263XT DRAM-less model with HMB, but aside from random read performance, the upper tier model has many of the same specifications. The DRAM-equipped SM2263 pushes up to 300,0000 random read IOPS, but the DRAM-less SM2263XT is only capable of 280,000 IOPS with HMB enabled. Without HMB, random read performance drops to 140,000 IOPS.

The rest of the performance specifications are similar. Sequential read/write performance reaches 2,400/1,700 MB/s for both controllers. Random write performance weighs in at an impressive 250,000 IOPS. We suspect we may find increased random write performance with the SM2263 when it arrives. For now, we only have the SM2263XT.

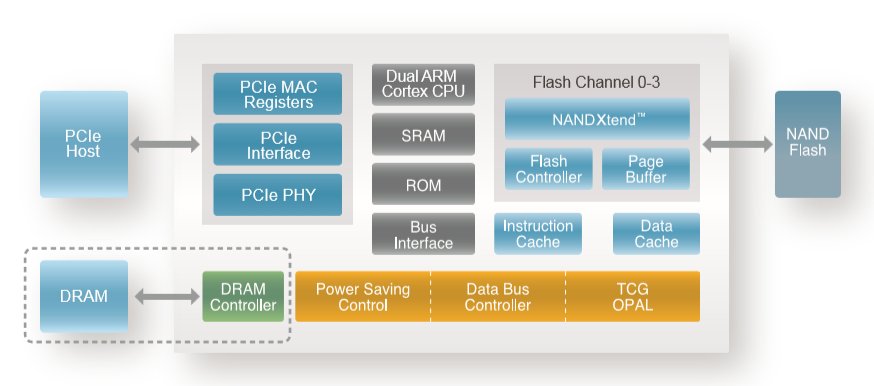

Features

A modular dual-core ARM Cortex processor is at the heart of the two new controllers. The SSD communicates through a PCI Express 3.0 x4 connection. The controllers also have four CE (Chip Enables) on each of the four NAND channels. The internal SRAM buffer features error-correction and the controller features end-to-end data path protection.

The design supports full disk encryption with 256-bit AES using TCG Opal and IEEE-1667 (Microsoft's eDrive). You can enable encryption without seeing a performance reduction. NANDXtend ECC Technology is SMI's proprietary form of low-density parity check code that ensures your data is safe on the flash.

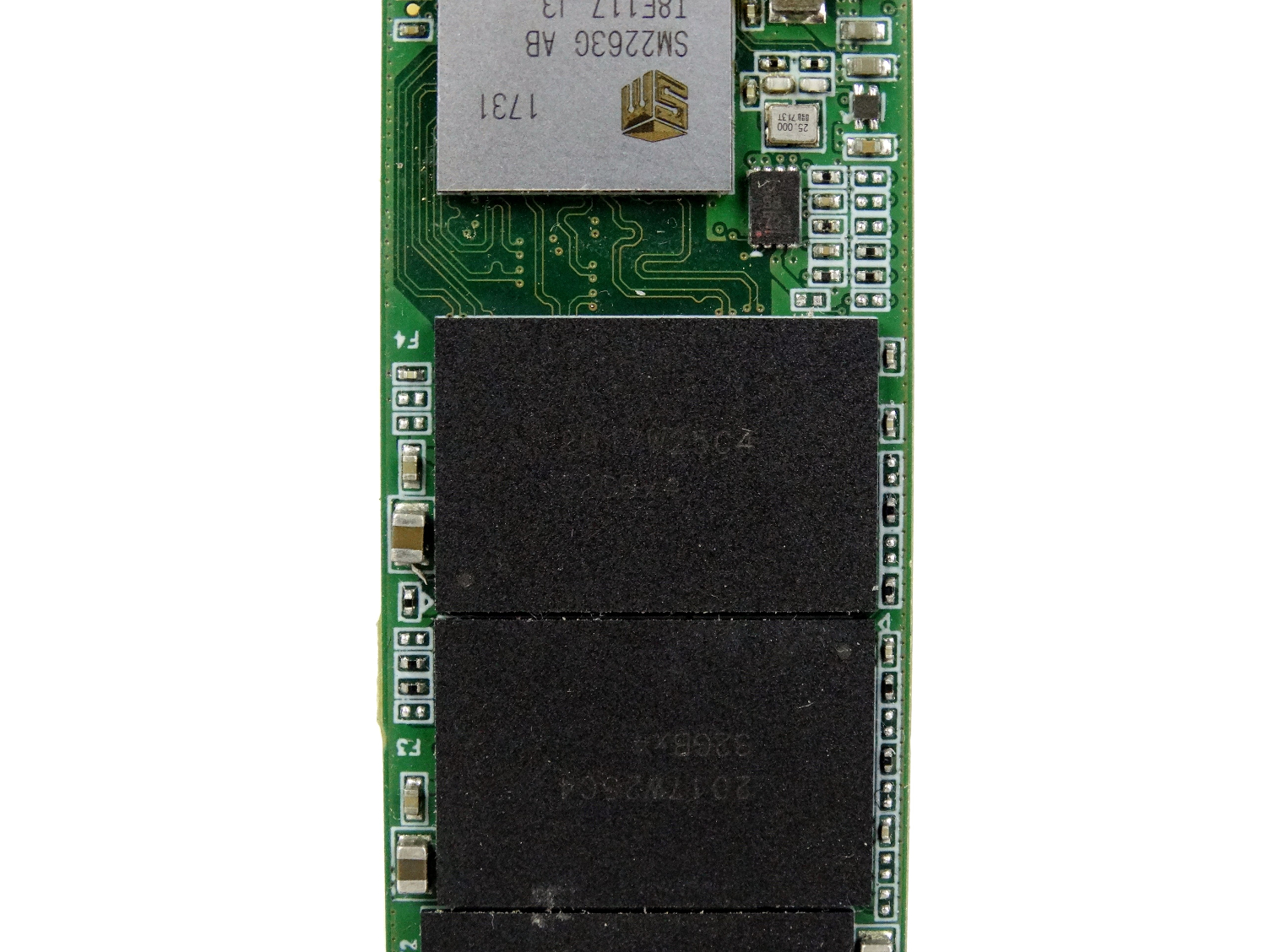

A Closer Look

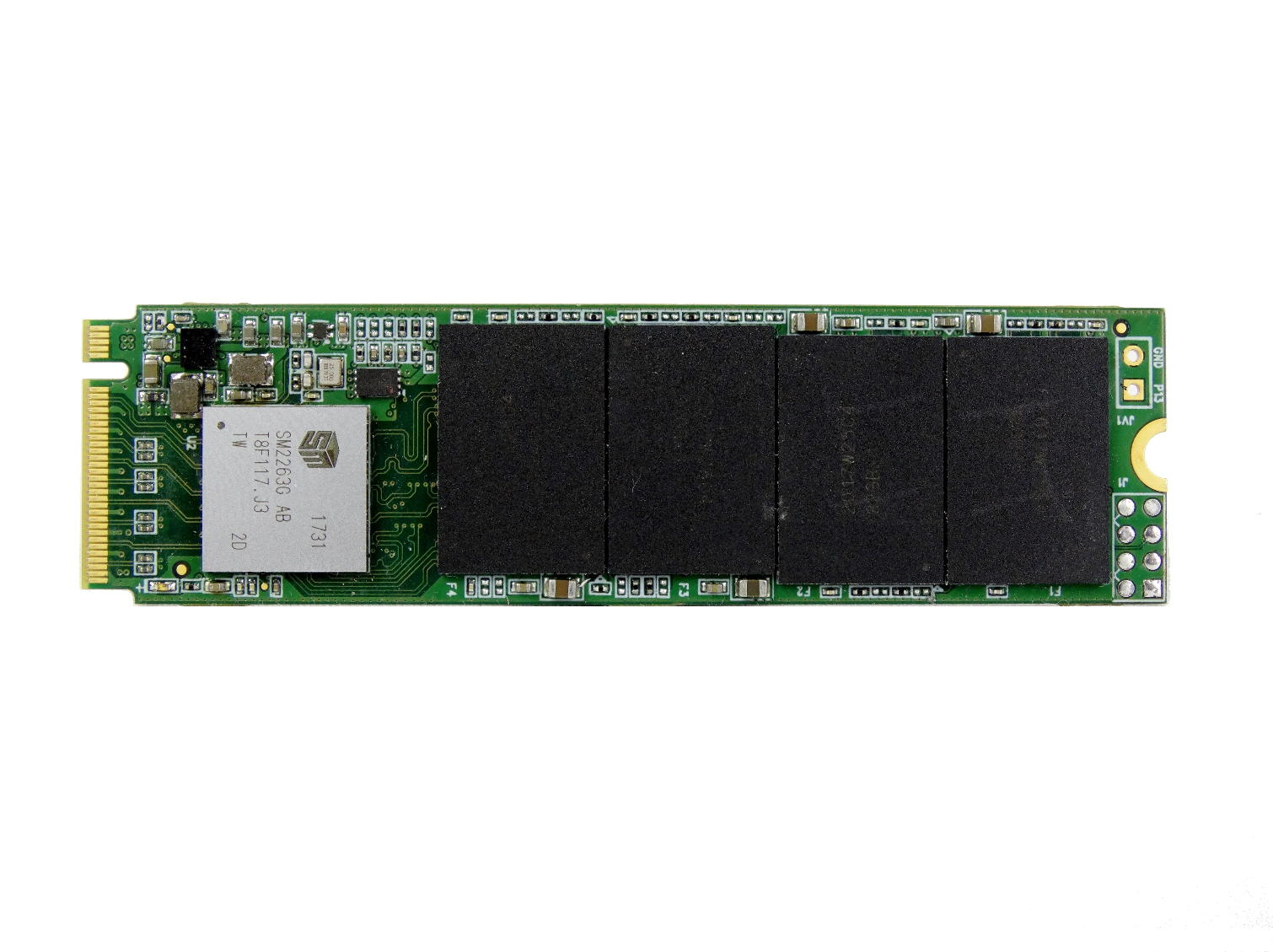

The SM2263 controller is surprisingly small. SMI says this controller will also appear in BGA SSDs at some point. Considering the SMI and Intel relationship, there is a very good chance the unreleased Intel BGA uses the SM2263XT.

MORE: Best SSDs

MORE: How We Test HDDs And SSDs

MORE: All SSD Content

Chris Ramseyer was a senior contributing editor for Tom's Hardware. He tested and reviewed consumer storage.

-

takeshi7 DRAM-less SSDs should have to advertise that in giant letters on their box so that consumers know to avoid them. Those mixed I/O numbers are pathetic.Reply -

WyomingKnott Is it correct that a 1 TB SSD will have 1 GB of DRAM, or is that a typo, or did I read it wrong? Sounds like a pretty big lookup table.Reply -

alextheblue Reply

The new gen HMB-capable DRAMless SSDs (with FCU or later) are good enough for most consumers. Also most PC users buy OEM boxes... I'd much rather see users offered a machine with HMB DRAMless SSDs than HDDs or non-HMB DRAMless SSDs.20609574 said:DRAM-less SSDs should have to advertise that in giant letters on their box so that consumers know to avoid them. Those mixed I/O numbers are pathetic.

Heck, for secondary storage (mechanical drive replacement, media storage) even QLC drives will be OK, so long as they're well-designed.

Newer hardware and operating systems allow PCIe devices to flag data headed directly to system memory. Even though the system memory and PCIe bus are on opposite sides of the CPU, the flagged data passes through the processor without adding parasitic load.

That answers the first question that came to mind. What are the requirements for direct-to-memory flag support? Is it only a question of PCIe version x.xx and OS + SSD support? -

Lutfij Found the time to read through this review. Very well written Chris, keep up the good work!Reply