IBM Patents Graphics Rendering on a Network On Chip

IBM was granted a patent that describes technology that integrates graphics rendering on a network on chip (NOC) device.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

IBM filed the patent in February 2008 and got the confirmation after an unusually short time frame. The NOC claimed by IBM includes integrated processor (IP) blocks, routers, memory communications controllers, and a network interface controller. The IP blocks in the patent feature at least one geometry processor, a plurality of scan converters, and a multiple pixel processors.

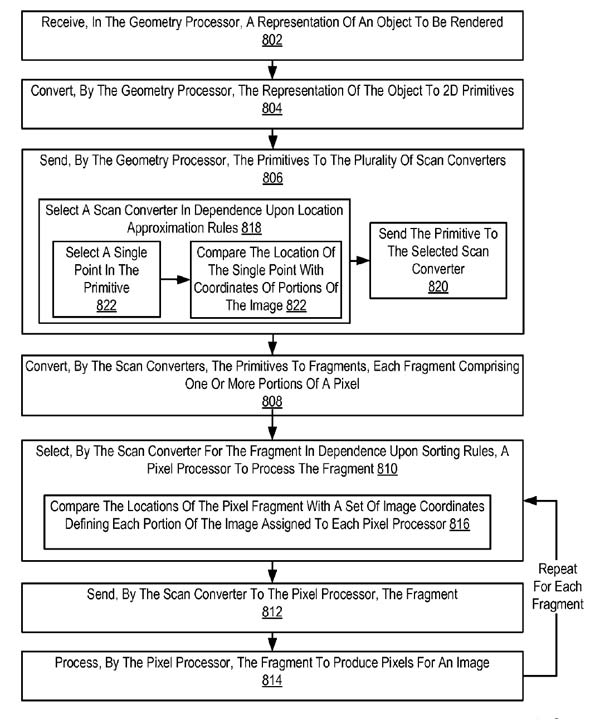

The description of the graphics capability of the NOC is scarce, but IBM is referring to very basic graphics processing capability throughout the document. According to IBM, claims the rights to a: "method comprising: receiving, in the geometry processor, a representation of an object to be rendered; converting, by the geometry processor, the representation of the object to two dimensional primitives; sending, by the geometry processor, the primitives to the plurality of scan converters; converting, by the scan converters, the primitives to fragments, each fragment comprising one or more portions of a pixel; for each fragment: selecting, by the scan converter for the fragment in dependence upon sorting rules, a pixel processor to process the fragment; sending, by the scan converter to the pixel processor, the fragment; and processing, by the pixel processor, the fragment to produce pixels for an image."

Additional claims include software drivers.

Article continues belowGet Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Douglas Perry was a freelance writer for Tom's Hardware covering semiconductors, storage technology, quantum computing, and processor power delivery. He has authored several books and is currently an editor for The Oregonian/OregonLive.

-

amk09 WHAT!!!!! Is this going to do what I think it's going to do? The possibilities are endless!Reply -

killerclick I'd like to patent brain upload - a virtual software brain (kind of like a virtual machine but with virtual neurons) hooked up to a converter that translates human brain activity to the virtual format via nano-electrodes.Reply

Then I'm going to sit and do nothing until someone makes a useful version of my patent and then I'll sue their ass off! Patents rule, yeah! -

Cazalan Wow. AMD/Intel/NVidia and countless other vendors better shut this patent down quick. That loose definition of a NOC pretty much includes every CPU with embedded video.Reply -

mattclary Network rendering is old hat, just because the network has been shrunk does not make it new or innovative. That's the problem with the patent system, idiots grant patents on obvious stuff.Reply -

Lord Captivus you should only be able to patent something ones you have build it, that would be easier and the world would evolve faster...Reply -

upgrade_1977 I'm trying to understand exactly what this would be useful for.. Would these be for cloud computing so that your home pc doesn't have to do any rendering? Would this make cloud computing or even regular internet surfing safer because your home pc has less code to execute?Reply -

Gatorbait Eraser: Patented. Pencil: Patented. You can not patent Eraser + Pencil. That is all this patent is for: Network processor + Graphics core. Parallel graphics on network processors for cloud graphics processing is not patentable. US PTO is a joke... will issue anything. No different than giving a server a IP address and having it do rendering and sending back the results... just making it dedicated... Another US PTO FAIL... but what do you expect, its government!Reply -

amk-aka-Phantom lol wut? another company patenting the concept instead of a product? Just you wait, by 2015 or so all progress will stop because the greedy fools will claw to their copyrights instead of sharing the knowledge and innovating... all for nothing, since you can't take any cash with you into your grave :PReply -

amk-aka-Phantom Reply9311197 said:I'm trying to understand exactly what this would be useful for.. Would these be for cloud computing so that your home pc doesn't have to do any rendering? Would this make cloud computing or even regular internet surfing safer because your home pc has less code to execute?

I'm afraid so.