Rumor: AMD's EPYC Milan-X CPU to Have 3D Die Stacking

We now know a lot more about AMD's forthcoming 3D die stacking technology, thanks to new tweets from reliable hardware leakers ExecutableFix and Patrick Schur. These tweets claim that we can first expect to see this tech at play in the EPYC Milan-X series of data center processors.

Milan-X aka Milan-X(3D). Genesis IO-die with stacked chipletsI love lasagna 😋 https://t.co/O2FrGxyd8PMay 25, 2021

AMD is working on a new CPU (codename Milan-X) that will use stacked dies. 😏May 25, 2021

A year ago, AMD revealed via its Financial Analyst Day 2020 event that the chipmaker was working on a new breed of processors that would utilize its X3D chip packaging technology. AMD's X3D hybrid technology is based on 2.5D packaging and 3D stacking. In layman terms, it allows AMD to stack various dies on top of each other inside the chipmaker's multi-chip modules (MCM). Considering the similarity, X3D is basically AMD's response to Intel's Foveros 3D stacking technology.

The latest rumors claim that Milan-X will be the first wave of chips to feature X3D chip packaging. Given the codename, it's reasonable to assume that Milan-X is comprised of Zen 3 cores, just like the EPYC 7003 (Milan) parts. ExecutableFix claims that Milan-X is based on the Genesis IO-die, alluding to the same I/O die inside Zen 3 EPYC chips.

However, we don't expect AMD to push the core barrier with Milan-X. At its presentation, the company explained that the objective behind X3D was to provide up to 10X higher bandwidth. However, the company never revealed what it planned to stack. ExecutableFix thinks that AMD is stacking chiplets, but core complex dies (CCDs) seem unlikely, given the cooling that they require.

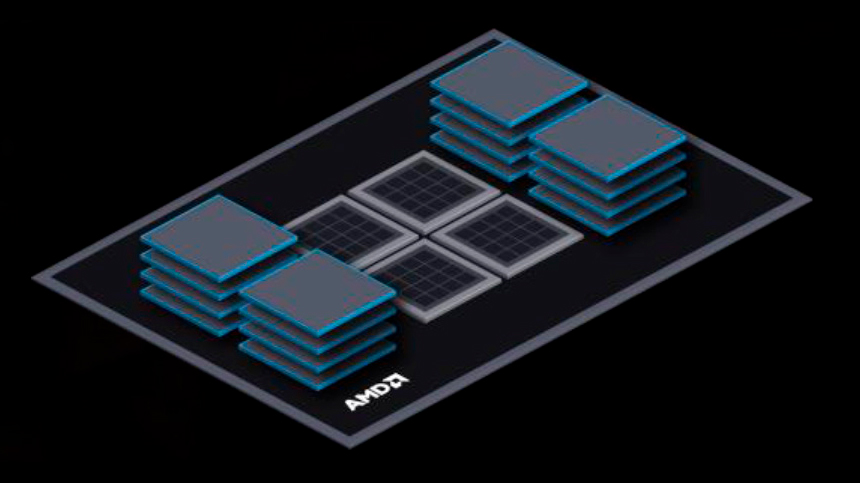

Therefore, AMD is very likely stacking memory on Milan-X as opposed to compute dies. Furthermore, the diagram that was shared at AMD's Financial Analyst Day 2020 exhibited a 2x2 layout with four interconnected chiplets and four stacked dies above a huge interposer. The four chiplets are probably the compute dies, and we suspect that AMD's stacking HBM packages on Milan-X. Apparently, there's one stacked die per each individual chiplet. The presence of HBM memory would do wonders on an EPYC processor, especially in a data center environment that's heavy on workloads that are sensitive to bandwidth.

Even on AMD's roadmap, the X3D processor was marked as "future." We haven't heard anything about Milan-X until today. However, AMD President and CEO Dr. Lisa Su is scheduled to deliver the a keynote at Computex 2021 called "AMD Accelerating – The High Performance Computing Ecosystem" so we may hear some more about Milan-X very soon.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Zhiye Liu is a news editor, memory reviewer, and SSD tester at Tom’s Hardware. Although he loves everything that’s hardware, he has a soft spot for CPUs, GPUs, and RAM.

-

Kamen Rider Blade I wouldn't be surprised if there is a L4 HBM cache at the bottom with L2/L3 Basement Caches in between with the CCD's at the top.Reply -

jimmysmitty ReplyKamen Rider Blade said:I wouldn't be surprised if there is a L4 HBM cache at the bottom with L2/L3 Basement Caches in between with the CCD's at the top.

Doubt the CCDs will be stacked in any way yet. More likely memory and maybe I/O. Intel has been working on 3D stacking for a long time and cooling is a major issue to overcome. -

Kamen Rider Blade Reply

That could work too, the Central I/O die has some extra thermal capacity =D and space for L4 cache.jimmysmitty said:Doubt the CCDs will be stacked in any way yet. More likely memory and maybe I/O. Intel has been working on 3D stacking for a long time and cooling is a major issue to overcome. -

thGe17 Most likely this is simply HBM2-memory on the CPU package substrate ... the same already known for Sapphire Rapids SP to be the case, which seems to have up to 64 GiB directly on the package, speeding up AI-workloads and working as a large L4.Reply

In this case, X3D is according to 3D more something like marketing and does not directly compete with Intels Foveros.

Stacking compute tiles with Milan-X on the other hand is currently highly unlikely because of thermals.