AMD Unveils Zen 4 CPU Roadmap: 96-Core 5nm Genoa in 2022, 128-Core Bergamo in 2023

AMD drops the 128-core bomb

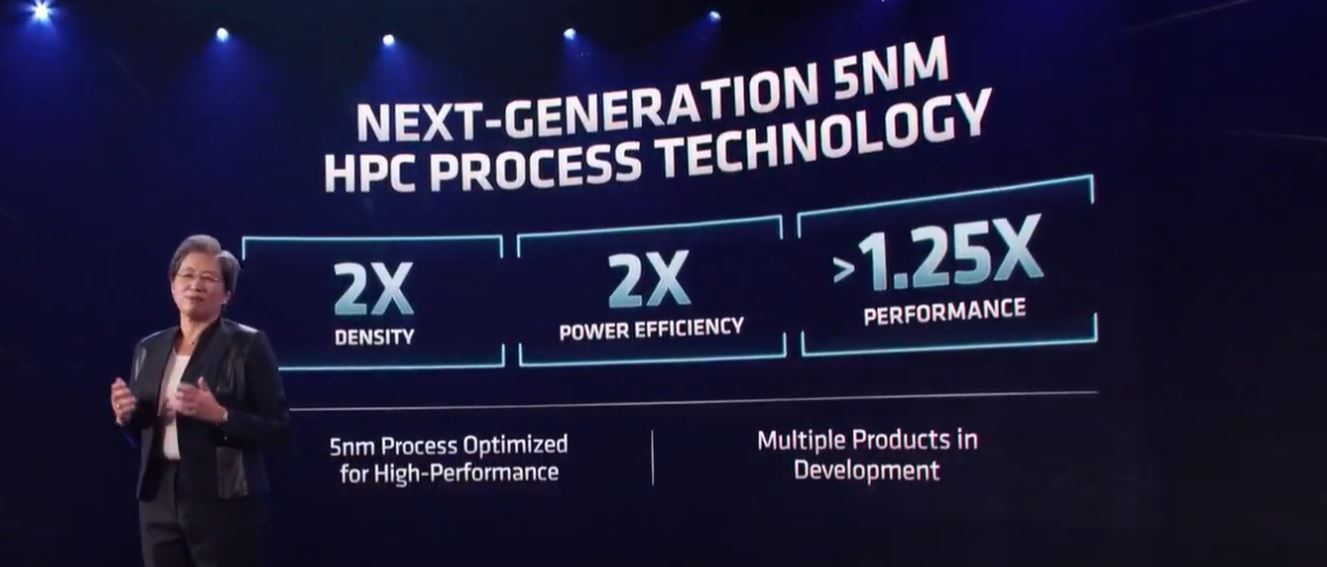

AMD CEO Lisa Su shared the company's Zen 4 CPU roadmap today at its AMD Accelerated Data Center event, including a 96-core Genoa model and a 128-core Bergamo chip. That adds yet more excitement to the event after AMD unveiled the EPYC Milan-X chips with up to 768MB of L3 cache and the Instinct MI250X GPU. AMD also shared its first details of the 5nm TSMC process it will use for the new Genoa and Bergamo chips, claiming it provides twice the density and power efficiency along with 1.25X more performance than the 7nm process AMD uses for its current-gen chips.

The new roadmap covers the fourth-gen EYPC processors. The 96-core Genoa will come on the 5nm process in 2022, while the 128-core Bergamo, also on 5nm, will come to market in 2023. In addition, Bergamo comes with a new type of 'Zen 4c' core optimized for specific use cases, meaning that AMD's Zen 4 chips will come with two types of cores, with the 'c' cores obviously being the smaller variants.

Here's AMD's TLDR for the Zen 4 CPU roadmap:

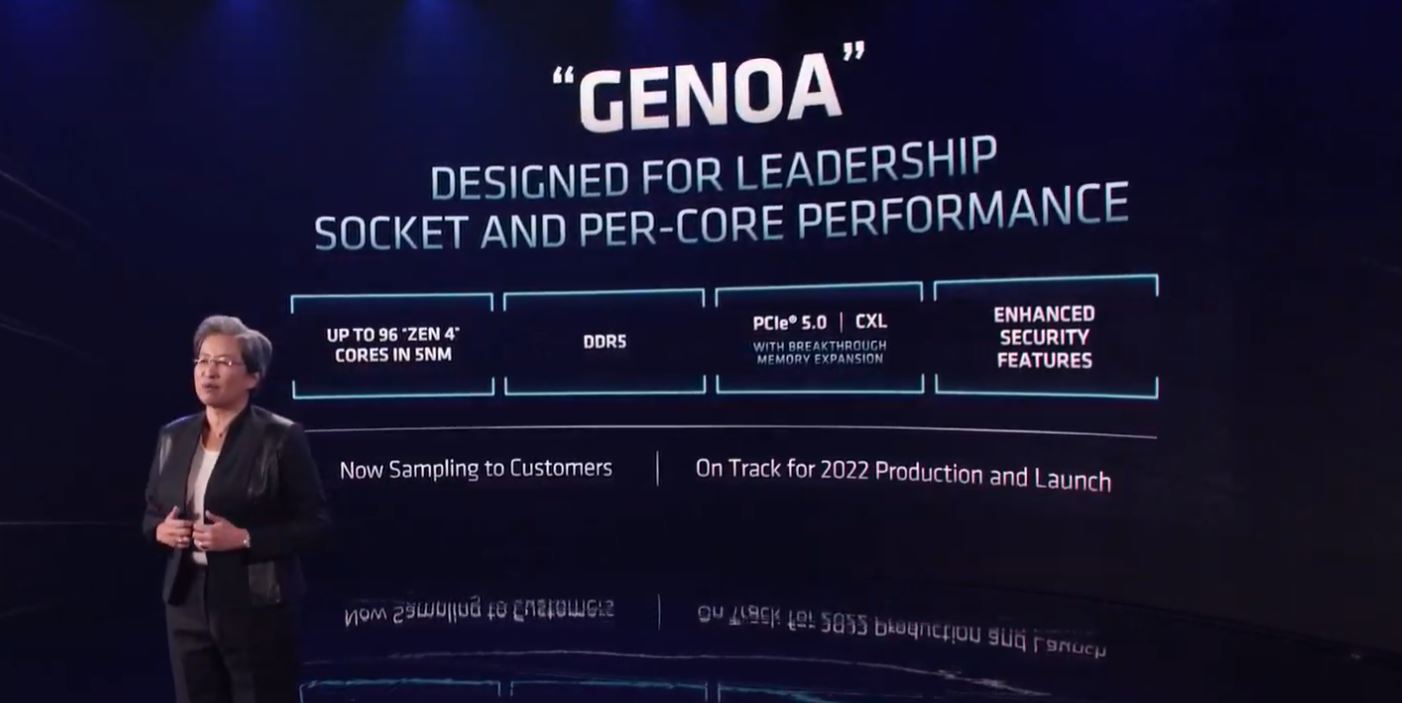

- “Genoa” will have up to 96 high-performance “Zen 4” cores, implement the next generation of memory and I/O technologies in DDR5 and PCIe Gen 5 and drive platform capabilities that perfectly balance the Zen 4 core, memory, and I/O to deliver leadership performance

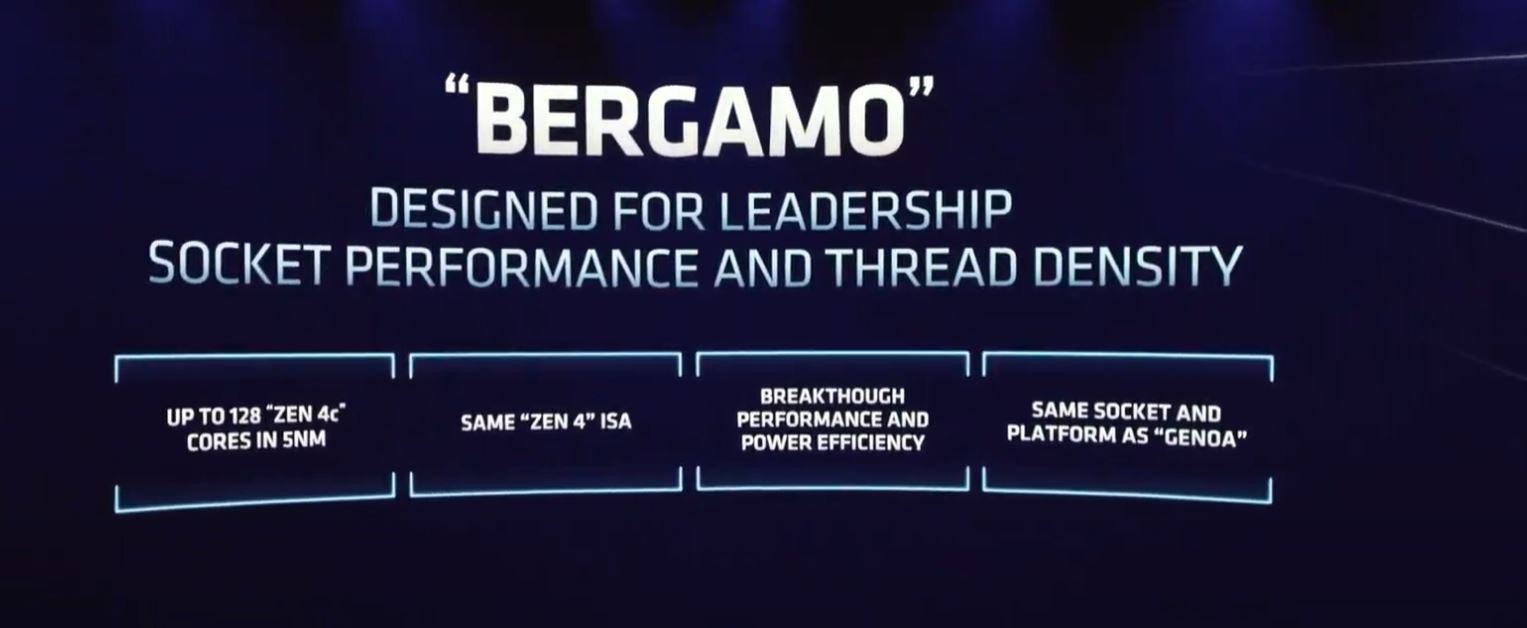

- “Bergamo” is a high-core count compute engine, customized for cloud native applications that demand high density thread density. Featuring 128 high performance “Zen 4 C” cores

- "Bergamo” has all the same features as Genoa including, DDR5, PCIe 5, CXL 1.1, same RAS, and the full suite of Infinity Guard security features, and it is socket compatible with Genoa

Genoa will have the 5nm process from TSMC, and AMD says 5nm offers twice the density and power efficiency of the 7nm process that powers the current-gen EPYC Milan chips. It also offers 1.25X of the performance of the 7nm process. That also bodes well for the consumer-focused Ryzen Zen 4 chips as well.

The EPYC Genoa chips will have up to 96 Zen 4 cores and support DDR5 and PCIe 5.0, along with the CXL 1.1 interface that allows for coherent memory connections between devices. This chip will address HPC and general-purpose data center, enterprise, and cloud workloads, with Su saying it will extend both per-core and socket-level (multi-threaded) performance. Genoa is sampling to customers now and is on track for launch in 2022.

Bergamo is also fabbed on the 5nm process and will come with up to 128 cores in a single chip.

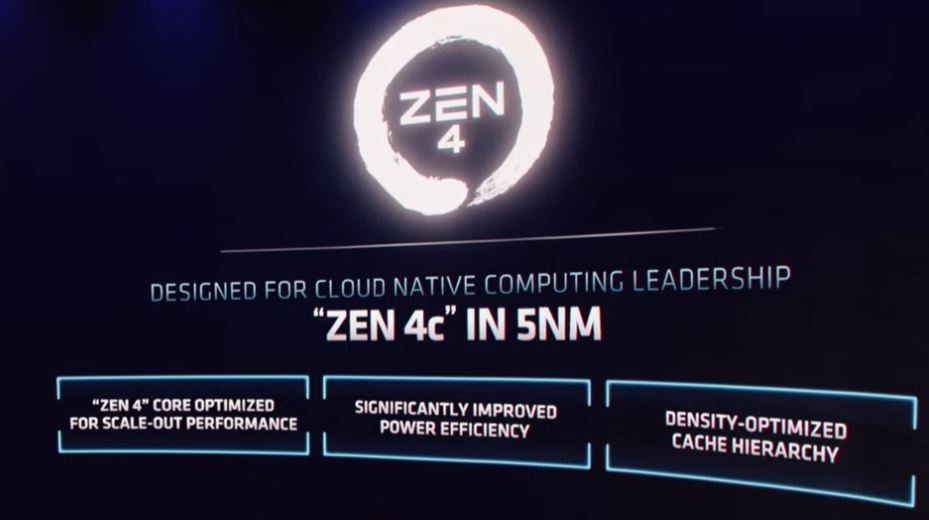

AMD has created a new 'Zen 4c' type of Zen 4 core, with the 'c' signifying that this core is designed for cloud-native workloads. The Zen 4c cores debut in the 5nm EPYC Bergamo, which is socket-compatible with Genoa and uses the same Zen 4 instruction set. That means you can drop these chips into the same servers as the Genoa models.

These 'c' cores are likely smaller than the standard Zen 4 core that will debut in Genoa, with certain unneeded functionality removed to improve compute density. However, the chips have a density-optimized cache hierarchy to increase core counts, thus addressing cloud workloads requiring higher thread density. This could mean that the chips have a smaller cache(s), or perhaps a cache level has been removed, but AMD hasn't shared details.

AMD does say that Bergamo will offer a higher level of power efficiency and performance per socket. Bergamo will ship in the first half of 2023. It comes with the same overall feature set as Genoa, so it has PCIe 5.0, DDR5, and CXL 1.1.

We're sure to learn more as AMD comes closer to launching these processors. Stay tuned.

- MORE: Best CPUs for Gaming

- MORE: CPU Benchmark Hierarchy

- MORE: AMD vs Intel

- MORE: All CPUs Content

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

ezst036 I want to see AMD adopt a big.LITTLE strategy in the future. They have those Jaguar/Bobcat etc cores, it would be nice to see them used across the board for the low/mid end. Having this many cores, it makes a lot of sense to have even 10 or so of them little efficiency cores. Threadripper is aimed at a big core userbase that presumably wants max threads at all times and has the specialty software to leverage it.Reply

I would think that servers would also be a big beneficiary of efficiency cores given the electric-bill sensitivity of many data centers. -

we_are_theBorg Article title should be "Bergamo", not "Begamo"Reply

Gotta teach that spell check Italian 😉

Thanks for all the great content and hard work you put in🌹 -

washmc "The 128-core Genoa will come on the 5nm process in 2022, while the 128-core Bergamo, also on 5nm, will come to market in 2023 " I think you meant 96-core Genoa.Reply -

Paul Alcorn Thanks for the heads-up, good eye! Both issues are corrected. Sorry for that, had to type this one up as it happened.Reply -

jeremyj_83 Reply

Datacenter really won't benefit from big.LITTLE. Due to virtualization you are always loading the cores and things that are mission critical need absolute best CPU performance. For example lets say you have a small 4 node datacenter. In an ideal scenario all your hosts will be running at 50% CPU capacity all the time. That way you have leftover cycles if a host should fail. In theory you could have 2 hosts fail and only then be at max CPU usage. Basically you don't want your cores sitting idle so there is very little use for big.LITTLE.ezst036 said:I want to see AMD adopt a big.LITTLE strategy in the future. They have those Jaguar/Bobcat etc cores, it would be nice to see them used across the board for the low/mid end. Having this many cores, it makes a lot of sense to have even 10 or so of them little efficiency cores. Threadripper is aimed at a big core userbase that presumably wants max threads at all times and has the specialty software to leverage it.

I would think that servers would also be a big beneficiary of efficiency cores given the electric-bill sensitivity of many data centers. -

peachpuff Reply

dE9N95uSqHAView: https://youtu.be/dE9N95uSqHAezst036 said:I want to see AMD adopt a big.LITTLE strategy in the future. -

VforV Yup, if MLiD is correct AMD's big-Little will be a combination of Zen last gen with Zen new gen. Described in very simple words.Reply

Their ciplets are already smaller in size than intel's tiles, or whatever they are called. That's why they also have better power consumption while using full sized cores. -

Sluggotg Just wait until AMD releases the "Bulldozer" Cores! (Joking) Impressive stuff. It is shocking how fast things change. I remember when they announced that "The Laws of Physics prevent making a Transistor smaller than 0.18 Microns". Now we are making them smaller than 5nm, (0.005microns).Reply -

escksu ReplyOsiris4.0 said:Did they say anything about quad channel RAM, or USB 4 support?

Quad channel is only reserved for threadripper. Ryzen remains at dual.