Intel Drops 10nm Tremont Atom P5900, Diamond Mesa eASIC, 'Edgewater Channel' Ethernet 700 Series

Intel supercharges its portfolio for 5G base stations

As part of Intel's announcement today of new Cascade Lake Refresh processors that come with significant per-core pricing reductions, the company also announced an expansion of its reach into the burgeoning 5G server market with a new lineup of products that includes the 10nm Atom P5900, the first all-Atom SoC based on the Tremont architecture, the Diamond MESA structured FPGA (eASIC), and the Ethernet 700 series of network adaptors.

Intel wraps these products up as a complete portfolio for 5G servers and base stations as it plans to become the leading silicon provider for 5G base stations, which represents an estimated $25 billion TAM opportunity by 2023. Intel had already set its sights on being the premiere silicon provider for base stations by 2022, but the company has pulled that projection into 2021, indicating it is well ahead of its own plans. Much of that improved outlook comes from a full range of processors and accelerators for the 5G segment, which we'll cover below.

- Intel Cascade Lake Xeon Platinum 8280 Review: Taking the Fight to EPYC

- Intel Announces Socketed 56-Core Cooper Lake Processors

- Intel Xeon Refresh: New Cascade Lake Refresh CPUs up to 60 Percent Cheaper Per Core

Tremont Comes to 10nm Atom P5900 SoC

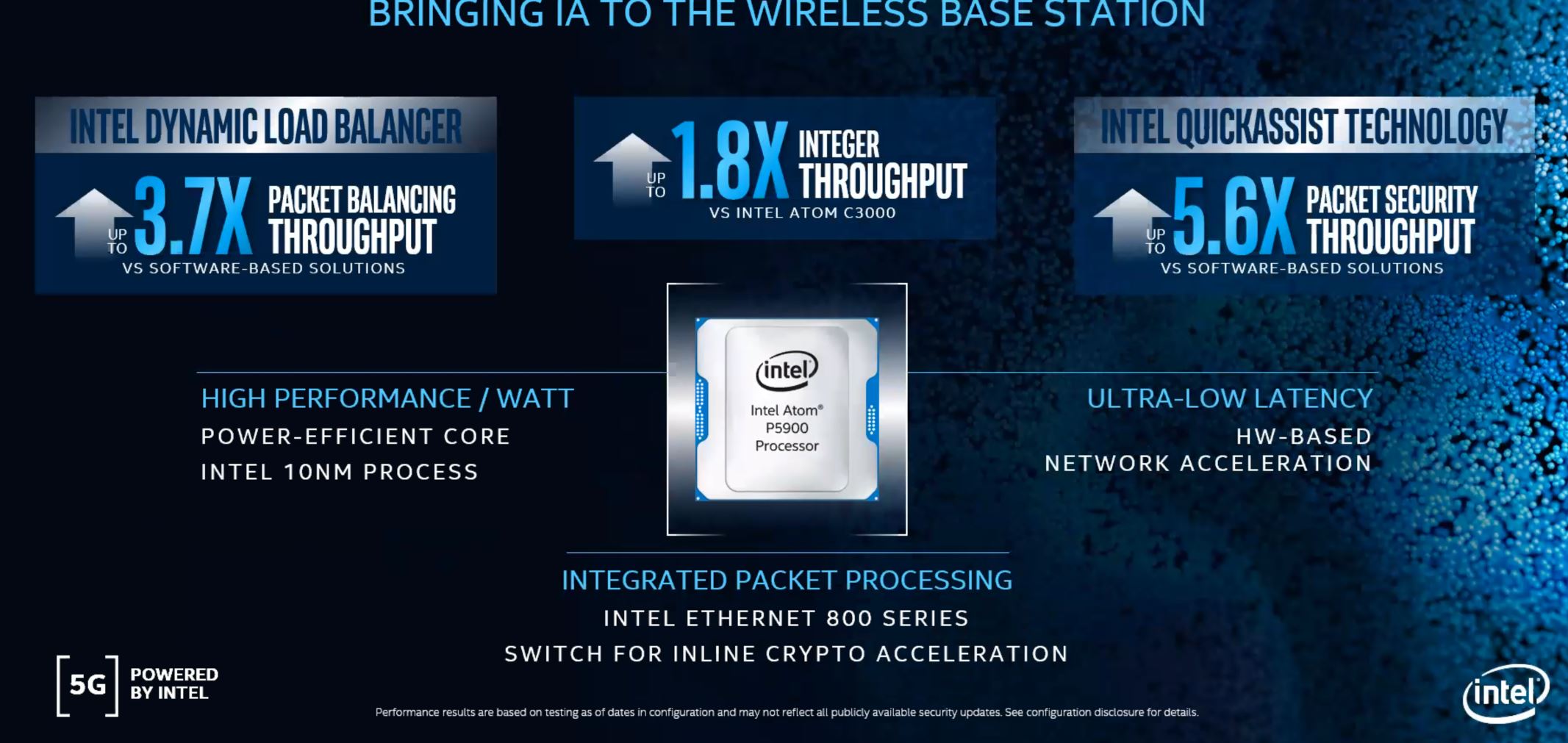

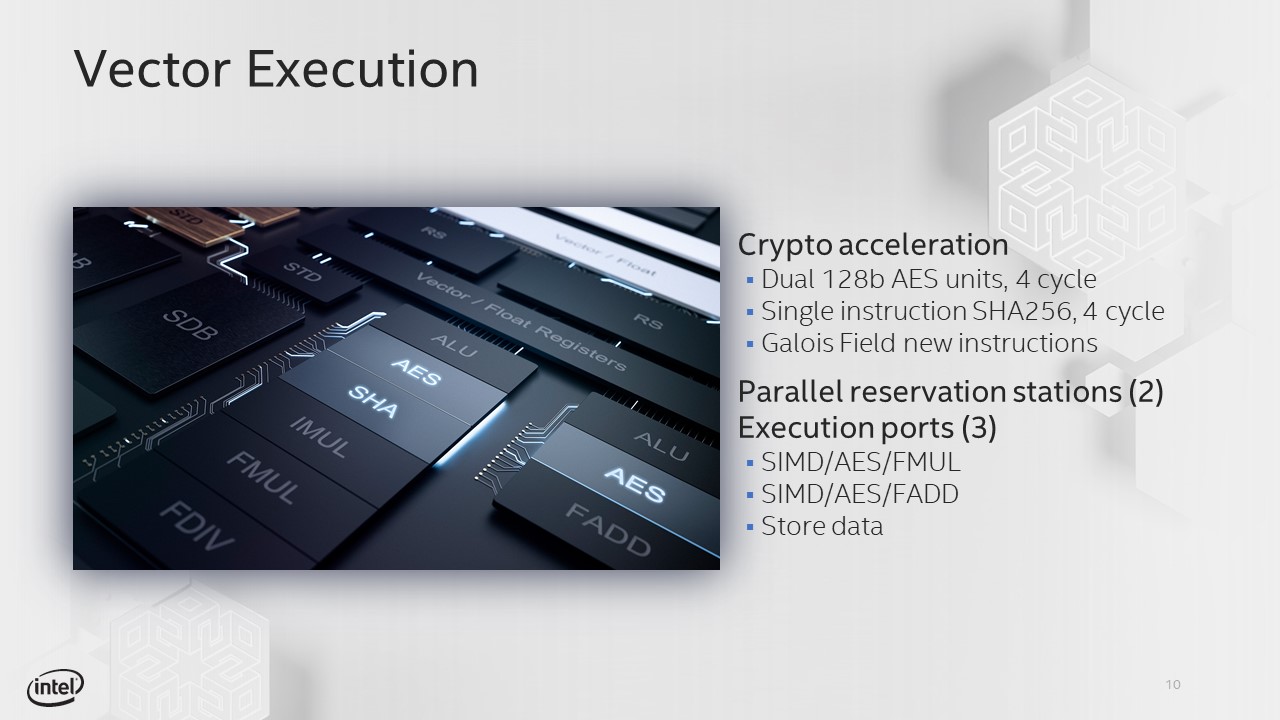

Intel designed the Atom P5900 SoC to capture key portions of the edge network, with the new chip being most noteworthy for its new Tremont architecture paired with the 10nm process. Intel tailored the new silicon specifically for the networking segment with hardware-based acceleration that is says provides up to an 80% increase in integer throughput compared to the Atom C3000 and up to 5.6X the cryptography throughput (courtesy of an internal Ethernet 8000 series switch) compared to software-based solutions. The chips also come with intel's Dynamic Load Balancer that the company claims provides a 3.7X boost to packet processing throughput.

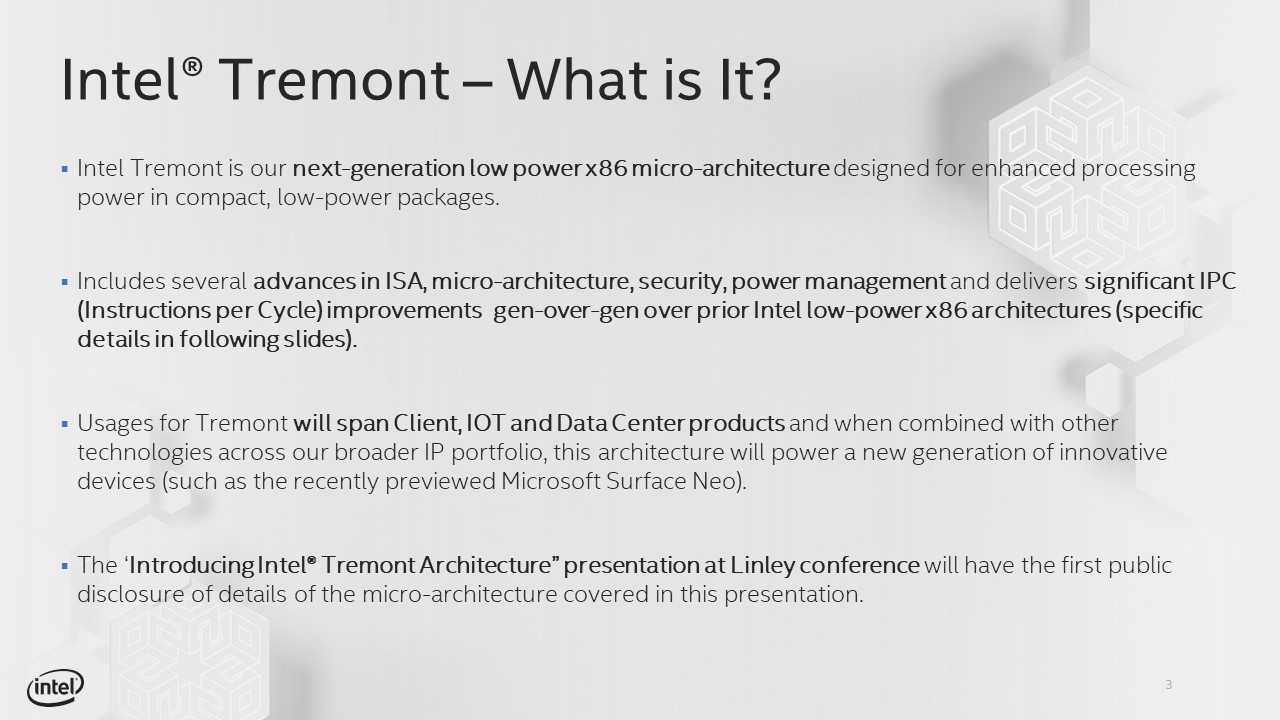

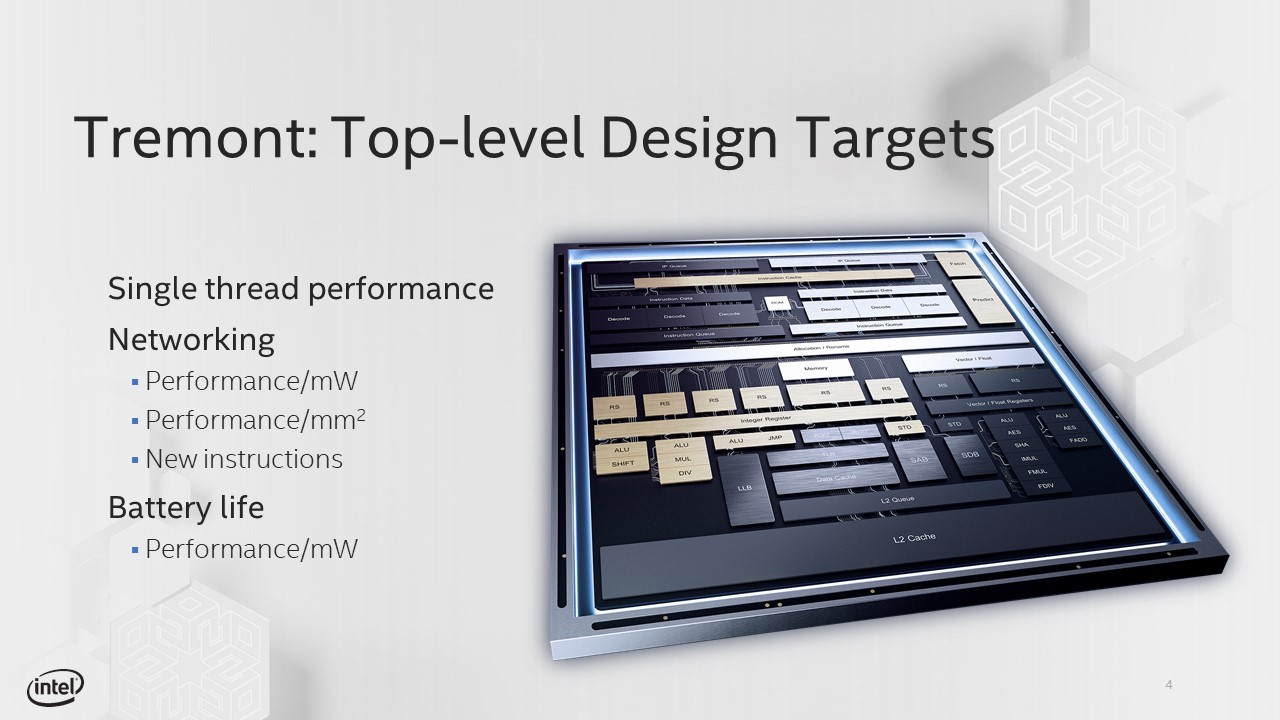

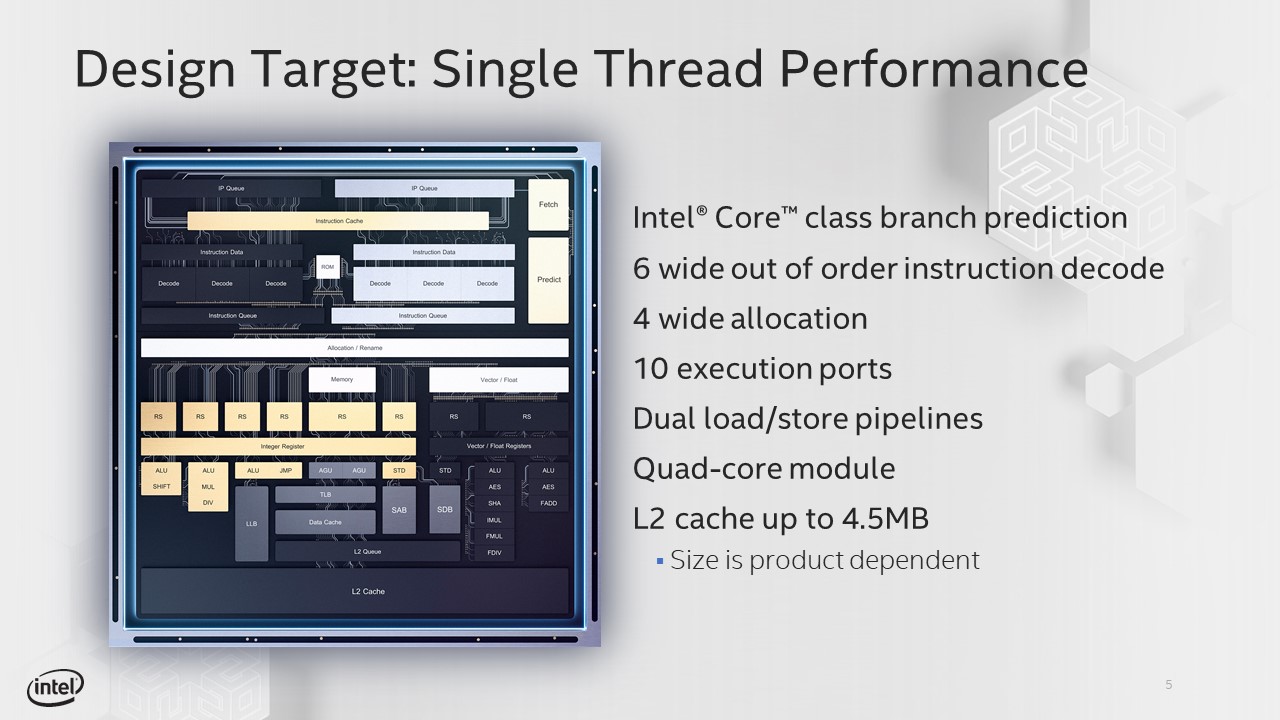

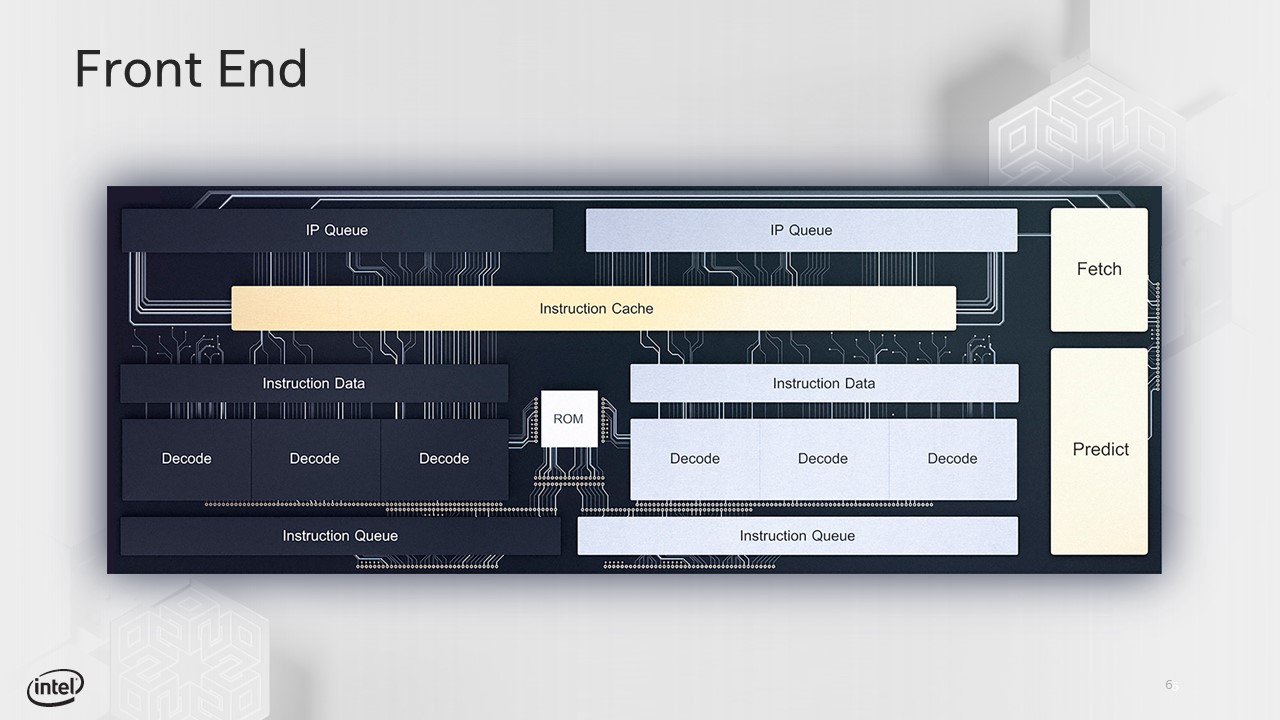

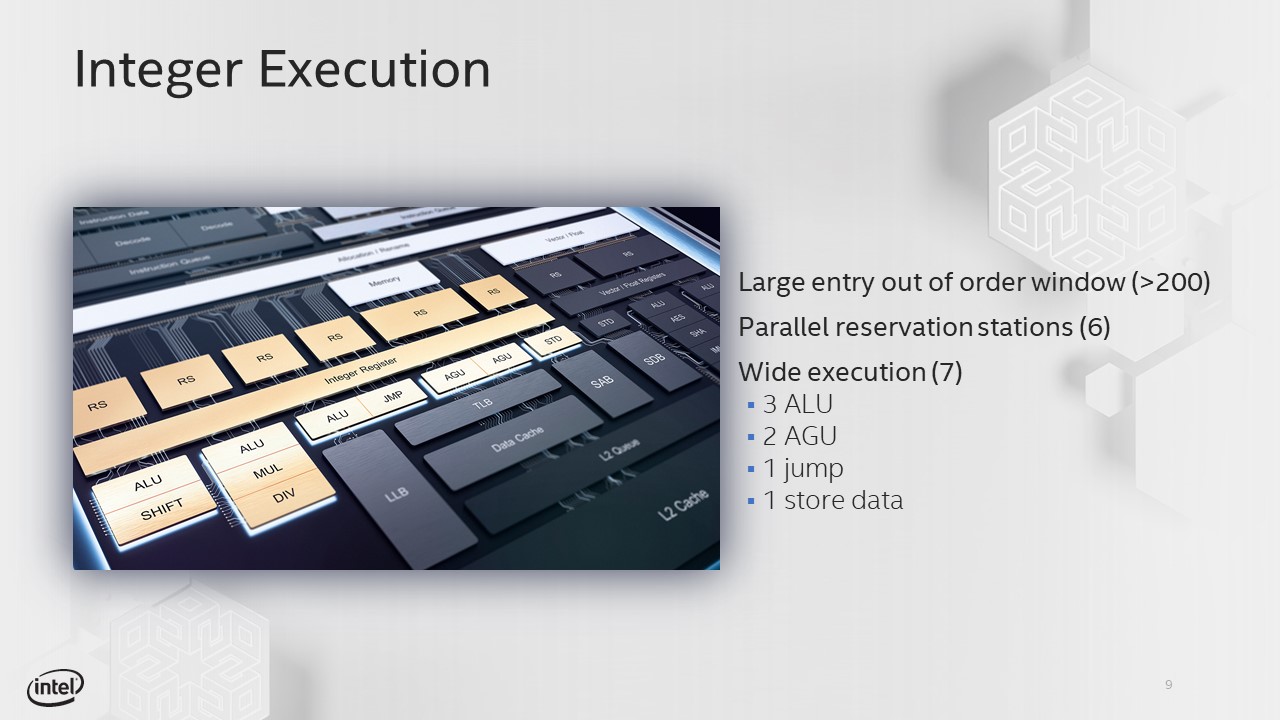

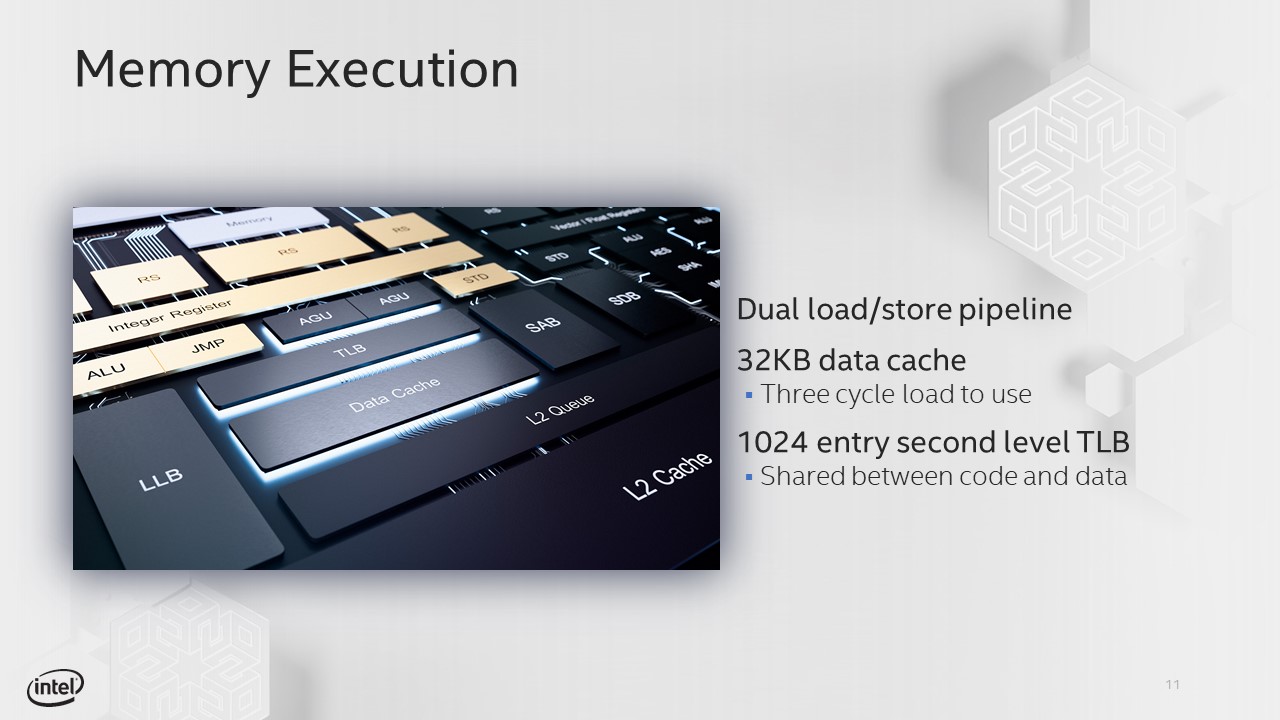

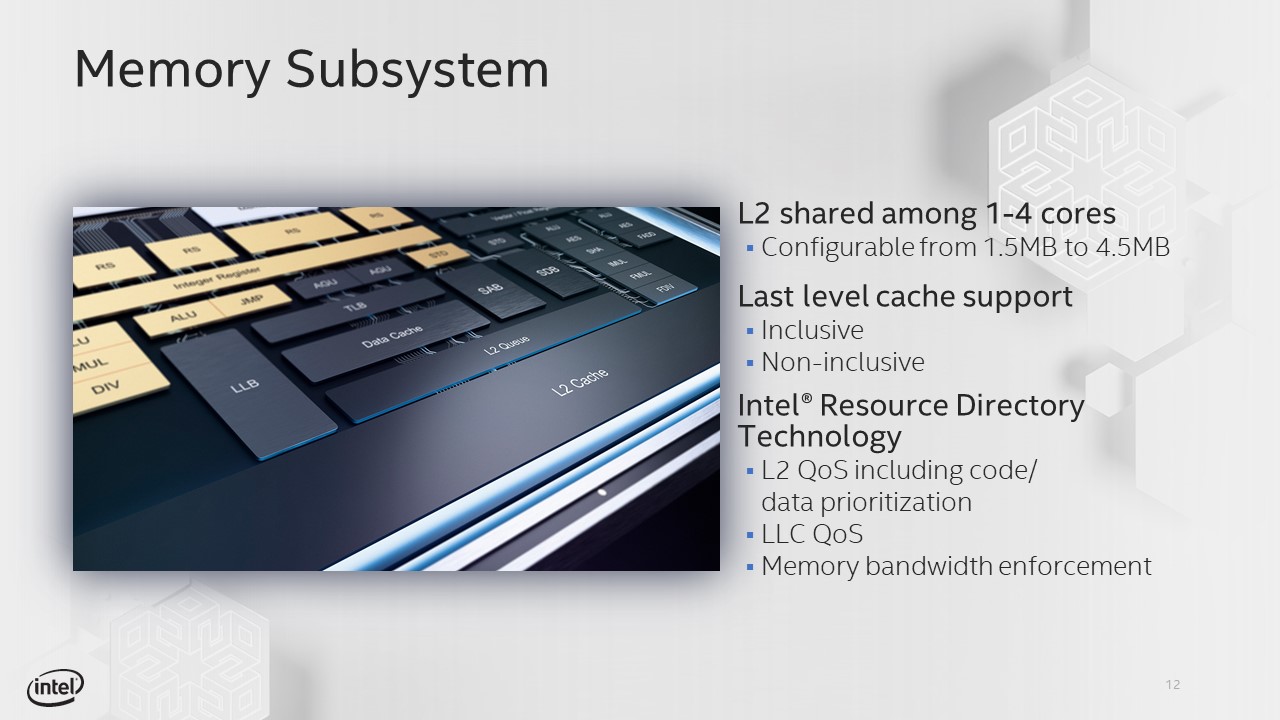

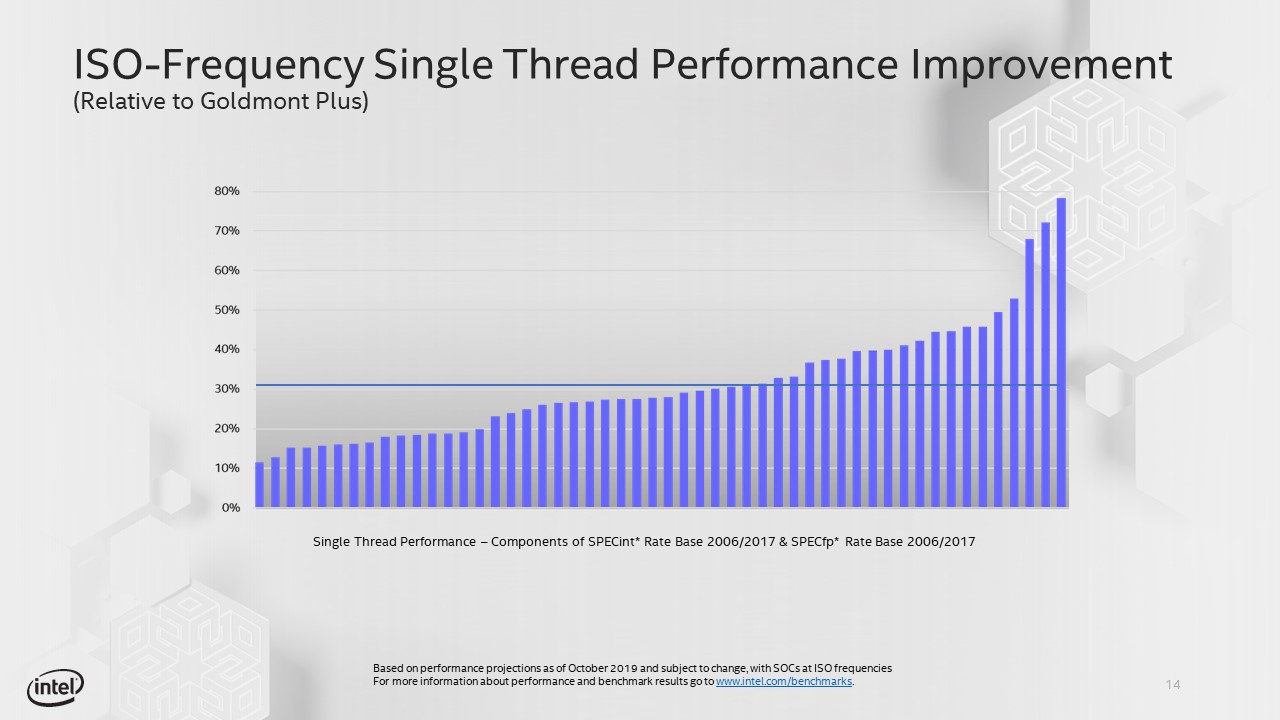

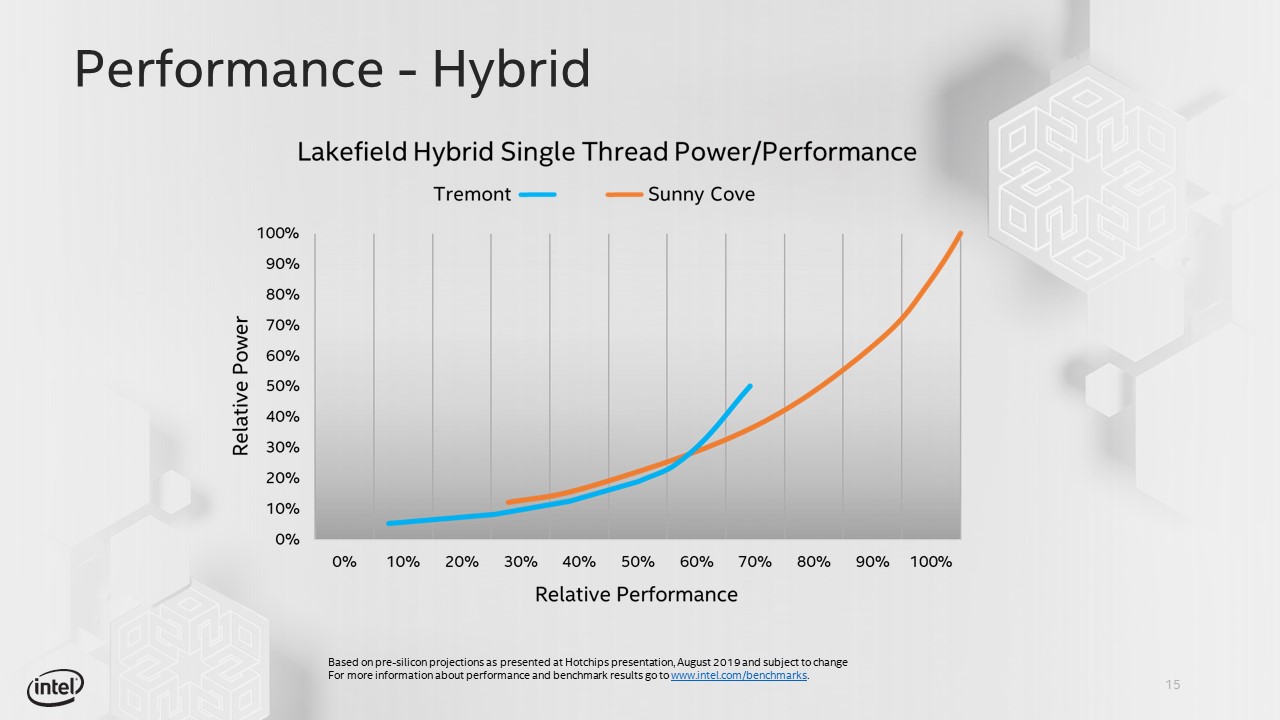

Intel's 10nm Atom Tremont architecture focuses on single-threaded performance but also brings other big improvements to bear, like the addition of L3 cache, a first for Atom, new power management enhancements that complement improved performance-per-watt, bolstered security, and support for new instructions. Intel claims the net effect of these optimizations equates to (up to) a 30% increase in instructions per clock (at static clock rates) over the previous Goldmont Plus architecture, but the jury is still out on clock speeds, which will ultimately determine overall performance. We've seen lower clock speeds with some of Intel's inaugural 10nm parts, but the company has obviously optimized its process several times since the last launch of 10nm parts, so we could see better gen-on-gen clock rates with the P5900.

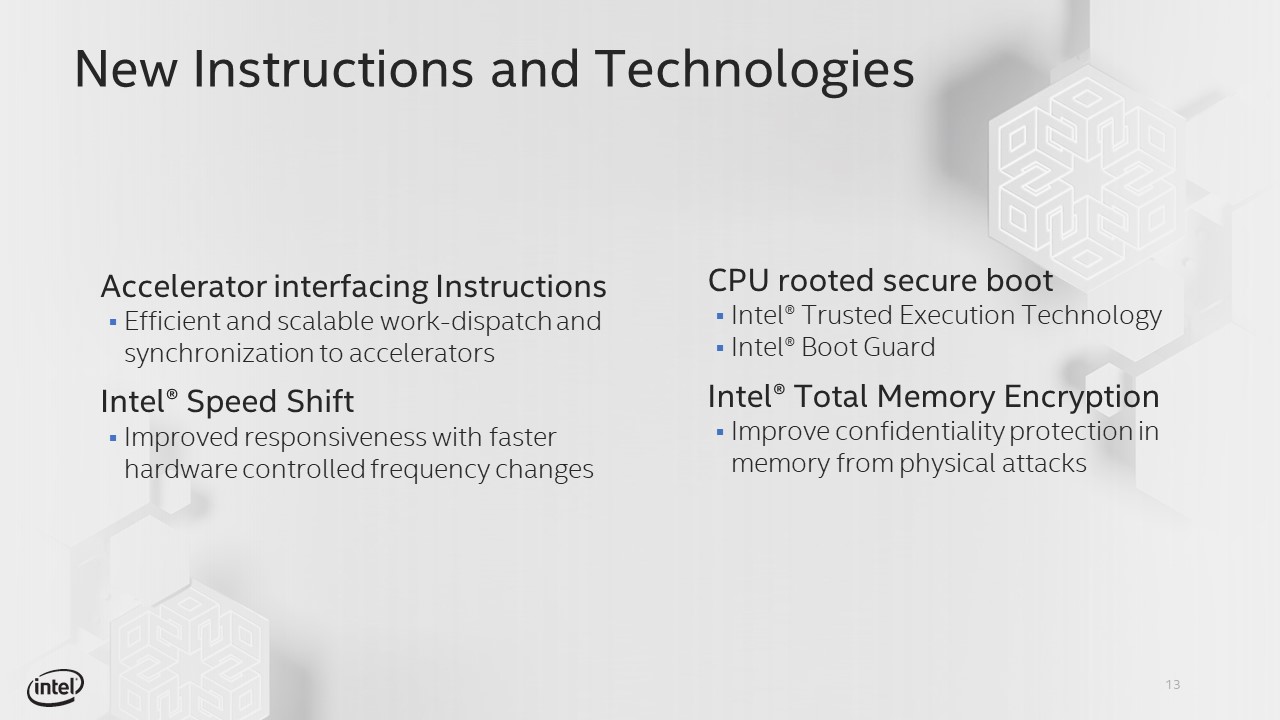

Intel's Lakefield processors currently use the Tremont cores in a 3D-stacked Foveros arrangement with a larger Sunny Cove core, but the P5900 marks the first Atom SOC with the new architecture. That brings a whole host of improvements, including a new dual-stage branch prediction unit and Speed Shift technology, along with a bevy of new security features for Atom, like secure boot, trusted execution technology, and total memory encryption. Intel hasn't provided the P5900's full technical specifications yet, but we'll update this article as they become available. Meanwhile, we have a deep dive on the architecture here.

The Diamond Mesa Debut

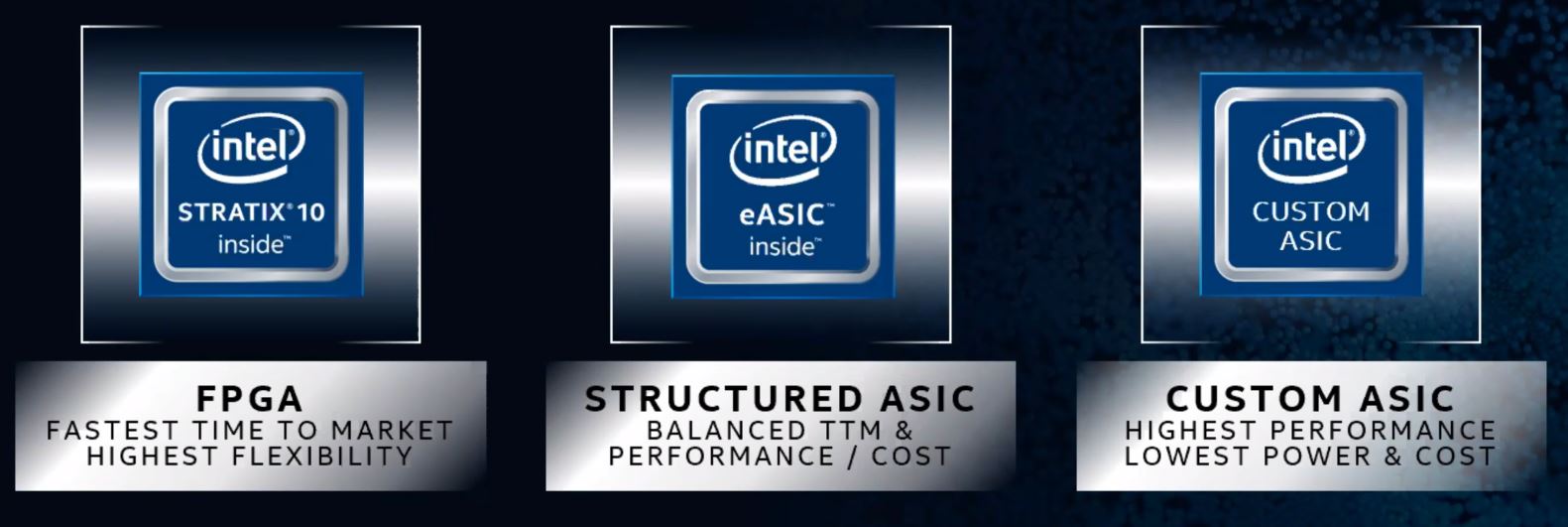

FPGAs are typically fully-programmable matrixes of logic units and interconnects that can address nearly any type of workload in a flexible manner, which improves time to market, but several other types of processors, like fully-customized ASICs, which offer lower price points and power consumption due to their specialized nature. However, these take longer to come to market due to their customized designs. Intel's structured ASIC (eASIC) lineup bridges the gap between standard ASICs and FPGAs, offering many of the benefits of a typical ASIC design paired with a faster time to market.

The eASIC lineup provides Intel with yet another form of compute, joining CPUs, FPGAs, ASICs, and soon GPUs, in the company's war chest, giving it unique options for various types of workloads and use-cases.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Intel's N3XS, N3X and N2x eASICs are already in the market, but today the company unveiled the broad strokes of its new Diamond Mesa lineup. Intel says the Diamond Mesa eASICs offer double the performance efficiency compared to their predecessors, but are footprint-compatible with Intel's FPGA products. These chips are designed for radio access networks, cloud storage appliances, embedded systems, and military applications. Intel didn't share any specific product specifications yet, but says the processors are already sampling to early access customers.

Intel "Edgewater Channel" Ethernet 700 Series

Finally, intel introduced its 'Edgewater Channel' Ethernet 700 series of network adaptors. These NICs feature specific optimizations for 5G networks, such as a hardware-accelerated Precision Time Protocol (PTP) that uses GPS clocks to satisfy the heightened cross-network service synchronization demands of 5G network providers, particularly for edge servers. The increased timing precision, which comes from an unspecified combination of hardware and software, helps to reduce overall application latency. We also expect this series to come with many of the same characteristics of Intel's broader Ethernet 800 series, but we'll update as more detailed specifications come to light.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.