AMD reportedly establishes $280 million silicon photonics hub in Taiwan — new R&D center could accelerate company's co-packaged optics roadmap

AMD straps in for lightning-fast execution

According to a new report, AMD has made the decision to establish two new R&D centers in Taiwan, focusing on silicon photonics, heterogeneous integration, and AI-related technologies, reports the Liberty Times. Both heterogeneous integration of system-in-packages (SiPs) and silicon photonics with co-packaged optics (CPO) are crucial technologies for current and next-generation AI and HPC components, as performance scaling via traditional methods is too slow to meet market requirements.

AMD's new R&D facilities will reportedly be established in Tainan and Kaohsiung, according to Taiwan’s Ministry of Economic Affairs (MOEA), but have not yet been officially confirmed by AMD. The R&D center in Kaohsiung would join forces with National Sun Yat-sen University and other academic and industrial institutions to accelerate talent development and research in AI-related fields such as heterogeneous integration and silicon photonics.

The total investment in two R&D facilities reportedly exceeds $280 million (NT$8.64 billion), with $170 million (NT$5.33 billion) provided by AMD, and the remaining $110 million (NT$3.31 billion) covered by the government funding.

AMD and silicon photonics: The story so far

Optical interconnects provide higher speeds, longer distances, and higher energy efficiency than traditional copper interconnects, making them suitable for next-generation AI and HPC data centers. Silicon photonics integrates optical and electronic functions on a single platform, establishing optical interconnections without using complex and power-hungry adapters, which typically increase latency.

Just like Intel and Nvidia, AMD is working to integrate silicon photonics into its platforms. But the reported establishment of an R&D center in Taiwan is not the first of AMD's efforts to get into the silicon photonics game.

Earlier this year, the company acquired Enosemi, which was its external development partner in photonics. AMD hopes to accelerate its silicon photonics and co-packaged optics solutions — from foundational silicon to systems-level integration — for its next-generation AI systems.

AMD's takeover of Enosemi strengthened the company's position in silicon photonics and optical interconnects by adding a specialized team experienced in combining light-based communication with traditional silicon. The small startup had single-chip Rx and Tx 16x112G chiplets, along with various IP at the time of acquisition, and AMD will likely integrate some of these components into future products.

By bringing Enosemi's engineers and intellectual property in-house, AMD gains the ability to design its own optical interconnects moving forward, instead of relying on external vendors. This enables the company to control a crucial piece of its technology stack: the communication fabric, which ties its CPUs and GPUs together inside data centers.

AMD's mid-term plan is likely to build vertically integrated rack-scale AI solutions — similar to Nvidia's NVL72 or NVL144 — that rely on copper, then offer optical interconnects, as well as develop optical connectivity solutions for AI data centers. Longer-term plans could include making inter-chip communication optical to boost performance and reduce power consumption, as well as enabling the connection of millions of processors across a single data center.

In May, Enosemi added a missing optical interconnection/silicon photonics piece to AMD's set of data center-grade technologies and expertise, which now includes CPUs, GPUs, DPUs, FPGAs, network solutions, and rack-scale system integration (via ZT Systems). The company now has the experienced specialists, proprietary IP, and early production expertise to avoid teething problems with its own silicon photonics products.

Moving closer to TSMC

AMD's U.S. R&D teams will develop elements like transceiver architectures, signaling protocols, and packaging topology to fit AMD's system needs. However, the company needed R&D close to manufacturing facilities (i.e. TSMC's most advanced fabs and packaging operations), and the ecosystem at large. To that end, the establishment of additional R&D centers focused on silicon photonics and integration is a highly strategic move aimed at streamlining the development of silicon photonics products.

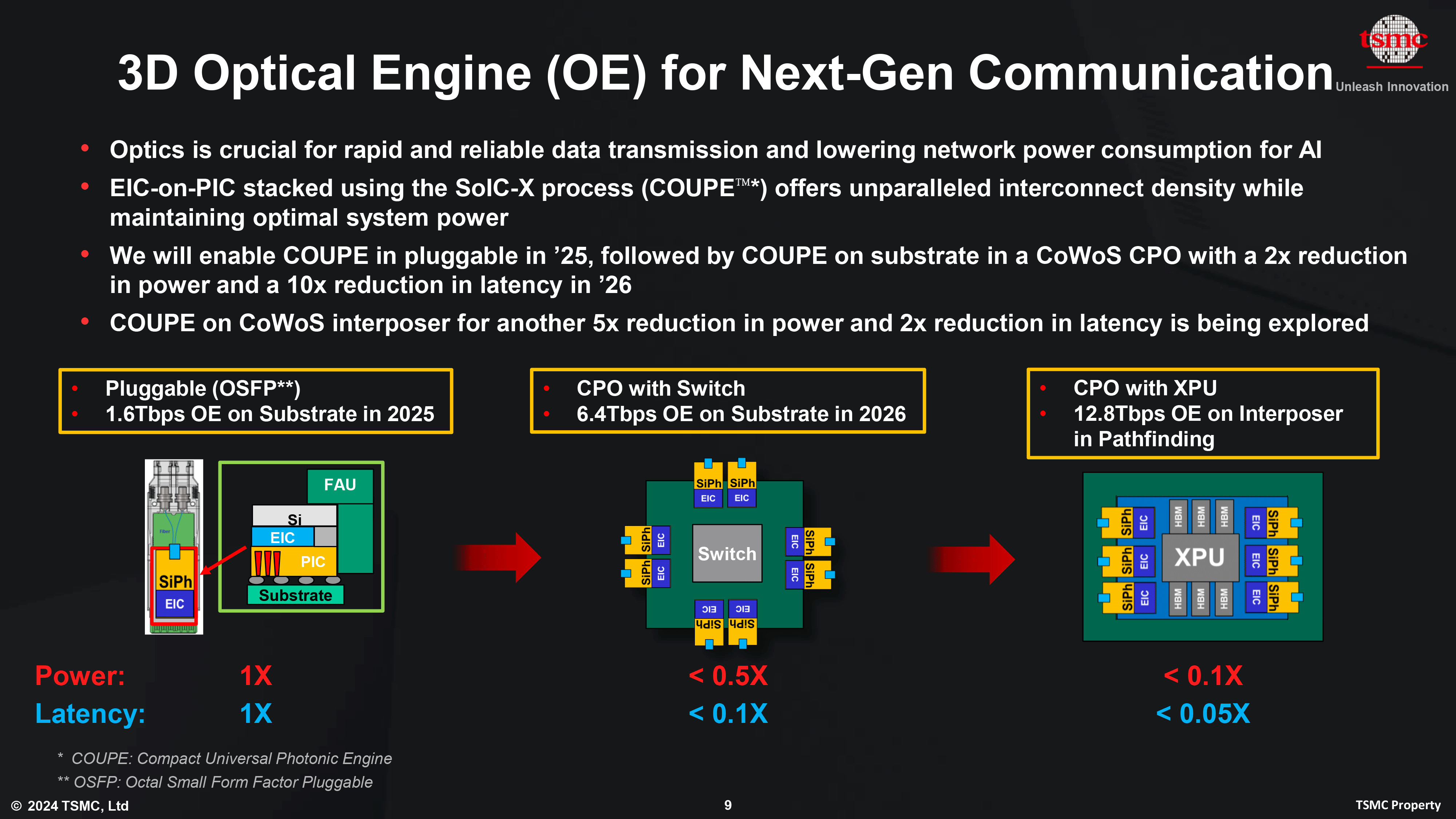

On the silicon photonics side of things, TSMC has COUPE — Compact Universal Photonic Engine — a hybrid optical platform that integrates photonic and electrical dies using SoIC-X and CoWoS packaging. The first-generation solution delivers up to 1.6 Tb/s on-package optical bandwidth, with the second generation delivering up to 6.4 Tb/s by 2026 – 2027, and up to 12.8 Tb/s with the third generation, which is expected to land before 2030.

As AMD produces all (or almost all) of its products at TSMC, it is reasonable for the company to adopt COUPE as the foundational platform for its upcoming silicon photonics products. This is not dissimilar to Nvidia's approach with ASICs for its Quantum-X and Spectrum-X switches, which are due in 2026 and 2027, respectively.

Assuming that AMD adopts TSMC's COUPE (not that it has much choice), it will follow the COUPE roadmap, and its Taiwanese R&D facilities will work closely with the contract chipmaker to optimize AMD's silicon photonics developments with TSMC's COUPE platforms (e.g., align photonics layouts with AMD's high-speed electrical fabrics), prototype the company's silicon photonics silicon, and perhaps bring up actual platforms together with engineers from TSMC.

Since AMD will team up with universities, expect the company to conduct material research focused on silicon photonics and heterogeneous integration in Taiwan, again, close to TSMC's primary R&D facilities. By doing so, local engineers will also be able to work closely with the global data center ecosystem, which is still predominantly based in Asia.

Another step towards the future

As bandwidth demands rise, optical interconnections and silicon photonics will be mandatory for future AI clusters, first at the cluster scale and eventually at the rack scale as well.

Nvidia's roadmap clearly shows that the company expects optical interconnects to be a part of its NVL144 Rubin and NVL576 Rubin Ultra rack-scale offerings. So, if AMD plans to compete, it needs to develop its own platforms with silicon photonics and CPO.

Enosemi and the Taiwan R&D centers will give AMD both the intellectual property and local engineering talent to optimize its IP with TSMC's COUPE to match Nvidia’s silicon-photonics trajectory. Whether AMD's 2027 rack-scale platform, based on the Verona CPUs and Instinct MI500-series accelerators, will use in-house-developed optical technologies for scale-out connectivity remains to be seen, but the firm's 2028 rack-scale solution is likely to enjoy the fruits of the Enosemi acquisition.

Follow Tom's Hardware on Google News, or add us as a preferred source, to get our latest news, analysis, & reviews in your feeds.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.