Intel's Z690 Chipset for Alder Lake Detailed in Leak, DDR5, DDR4, and PCIe 5.0

DDR5 and DDR4 both supported

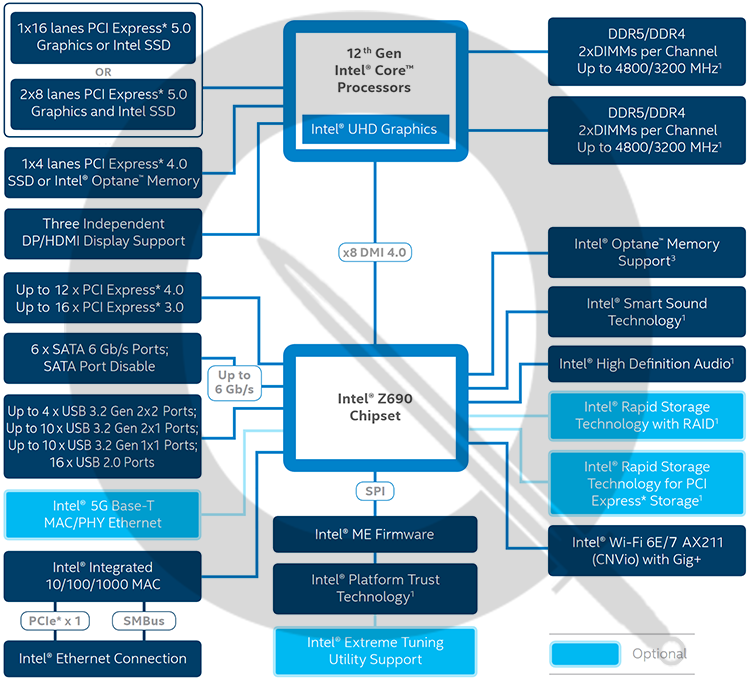

If you believe the chatter around the water cooler, Intel's upcoming Alder Lake lineup of processors is coming our way as soon as October. And, of course, a processor needs to find a home in a motherboard. Intel's Z690 will be the top-end chipset for 12th Generation Core processors codenamed Alder Lake, and according to a report by Performance Computing Inquisitor, the new boards will come with cutting-edge memory and PCIe connectivity. As with all leaked information, even though these details do line up with what's generally known about the Alder lake processors, do take these new bits with a grain of salt.

For starters, the leaked information claims the Z690 chipset supports both DDR4 and DDR5 DRAM. That means that it is up to the motherboard maker to choose which memory it decides to support on the motherboard, and it will ultimately result in mixed motherboard offerings from board partners like Asus, MSI, and Gigabyte, among others. In addition to the mixed memory support, the Z690 chipset has Gear 2 or Gear 4 modes for DDR5. This allows the memory controller to run at half or quarter speed, respectively, depending on the data rate, to boost overall throughput.

The CPU outputs 16 Gen5 PCIe lanes, while the chipset provides up to 12 PCIe Gen4 lanes and up to 16 PCIe Gen3 lanes. This setup purportedly allows for higher-end SSDs to be attached, while also keeping GPUs on the newer PCIe bus standards.

Intel has decided to upgrade its Direct Media Interface (DMI) connection, which now uses 8 PCIe Gen4 lanes for communication between the processor and chipset, as pictured in the diagram above. It is worth pointing out that the chipset supports solid USB connectivity with up to four USB 3.2 2×2 (20Gb/s) ports. And for WiFi, there are CNVio modules that support Intel Wi-Fi 6E, and possibly even Wi-Fi 7. However, the latter is less likely in the near term.

As a general reminder, all of the aforementioned information should be taken with a grain of salt. Until Intel discloses further details, the specifications are uncertain and will remain that way until the launch later this year.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

-

PCWarrior Nice to see the DMI link getting upgraded to DMI4.0 (i.e. using PCIe4) while retaining 8 lanes (DMI4x8). Together with the other CPU lanes (the PCIEe5x16 and the PCIe4x4) it means that this generation offers 28 cpu physical lanes and with multiplexing you get (up to) 50 platform physical lanes from which 36 (16+4+16) can operate unsaturated as direct PCI3 physical lanes when populated with PCIe3 peripherals. Amazing that we now have IO connectivity closer in sheer number of lanes to last gen HEDT/server platforms while of course beating them in speed/ bandwidth (the total IO direct bandwidth of 12th gen cpus is equivalent to 88 PCIe3 lanes!). As a reminder the X299 offered 48 (44direct+4DMI) and X299X offered 52 (48direct+4DMI) PCI3 physical cpu lanes and bandwidth.Reply

Problem is that the boards that will offer all these features will be expensive. Even PCIe bifurcation for x8/x8 is now considered an “enthusiast feature” on Z490/Z590. Minimum cost to get the full Z690 experience will probably be $370-$380. I expect the extreme aircooled versions (Godlike, Xtreeme) to top at $1200 and the extreme watercooled ones with the monoblocks (waterforce, aqua, glacier) to top at $1700. Insane prices for motherboards for cpus that cost $600-$650 or less. -

kal326 Hopefully at least some models follow the support both method. The last board I recall that did both was a Gigabyte one that had 2xDDR3 slots and 4xDDR2 slots with a P35 chipset. It allowed swapping over to DDR3 down the line. I don’t recall any Intel chipsets that did this for DDR3 to DDR4, but they may have existed. So dual support isn’t really unexpected and hopefully does exist for around launch for transition purposes.Reply

Especially with an uncertainty around DDR5 pricing and availability. We already know it’s going to be more given some structural changes which ultimately will benefit consumers, but bleeding edge isn’t cheap.

Edit: checking around evidently this happened with the 1xx and 2xx chipsets for Skylake and Kabby Lake. I skipped that whole generation. -

Geef That will probably be a big thing for upgrades this time around since DDR4 has been around a long time and also DDR5's base performance are lower or at high end DDR4. Make people think twice before upgrading unless they don't have to buy new ram...Reply -

scottsoapbox With how much additional heat and power requirements PCIe 4 brought, do we even want PCIe 5 before they can improve its efficiency?Reply

Especially since nothing can use it yet. Totally paying more for a number on the box (likely justified as future proofing). -

dan1991Ro Replyscottsoapbox said:With how much additional heat and power requirements PCIe 4 brought, do we even want PCIe 5 before they can improve its efficiency?

Especially since nothing can use it yet. Totally paying more for a number on the box (likely justified as future proofing).

Its not about having pcie 5.0 but more about having gpus with less pcie lanes i think.So lower costs at the same bandwith.

Right now, even pcie4.0x8 isnt saturated by much so imagine pcie5.0 with 8 lanes. -

scottsoapbox Reply

Except PCIe 5 costs more than PCIe 4 so that makes no sense.dan1991Ro said:Its not about having pcie 5.0 but more about having gpus with less pcie lanes i think.So lower costs at the same bandwith.

Right now, even pcie4.0x8 isnt saturated by much so imagine pcie5.0 with 8 lanes.

Neither does doubling the speed of something per lane to then use half as many lanes. That is literally doing work to end up in the exact same place.