IBM Talks Next-Gen Power Architecture, Live Hot Chips 31 Coverage

We're here at Hot Chips 31, the premiere venue for the biggest semiconductor vendors to highlight their latest architectural developments, to cover IBM's presentation of the next generation Power architecture. This is live coverage, so refresh your browser frequently for updates as the talk progresses.

Surprisingly, supercomputing bellwether IBM hasn't been in the news lately with big supercomputing wins, with the latest Frontier and Aurora wins going to AMD's EPYC and Radeon and Intel's Xeon and Xe Graphics Architecture, respectively. Even the newly-announced El Capitan doesn't seem to be headed IBM's way, either, largely because the now-dominant Cray Shasta/Slingshot architecture that will power the system currently doesn't come in IBM flavors.

That leaves the Power9-packing Summit, which we covered in-depth here, as IBM's last big win. Let's see what the company is up to now.

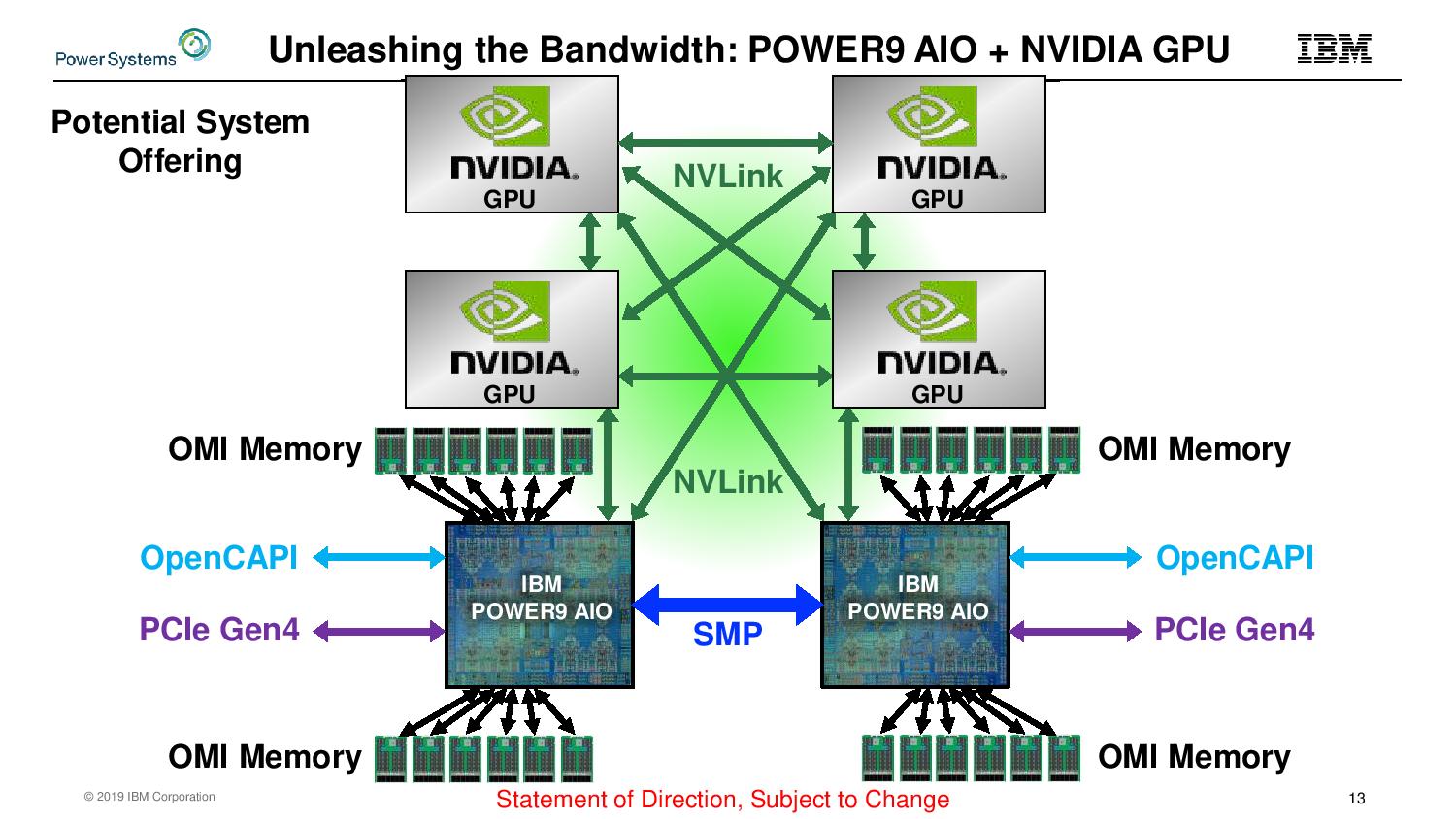

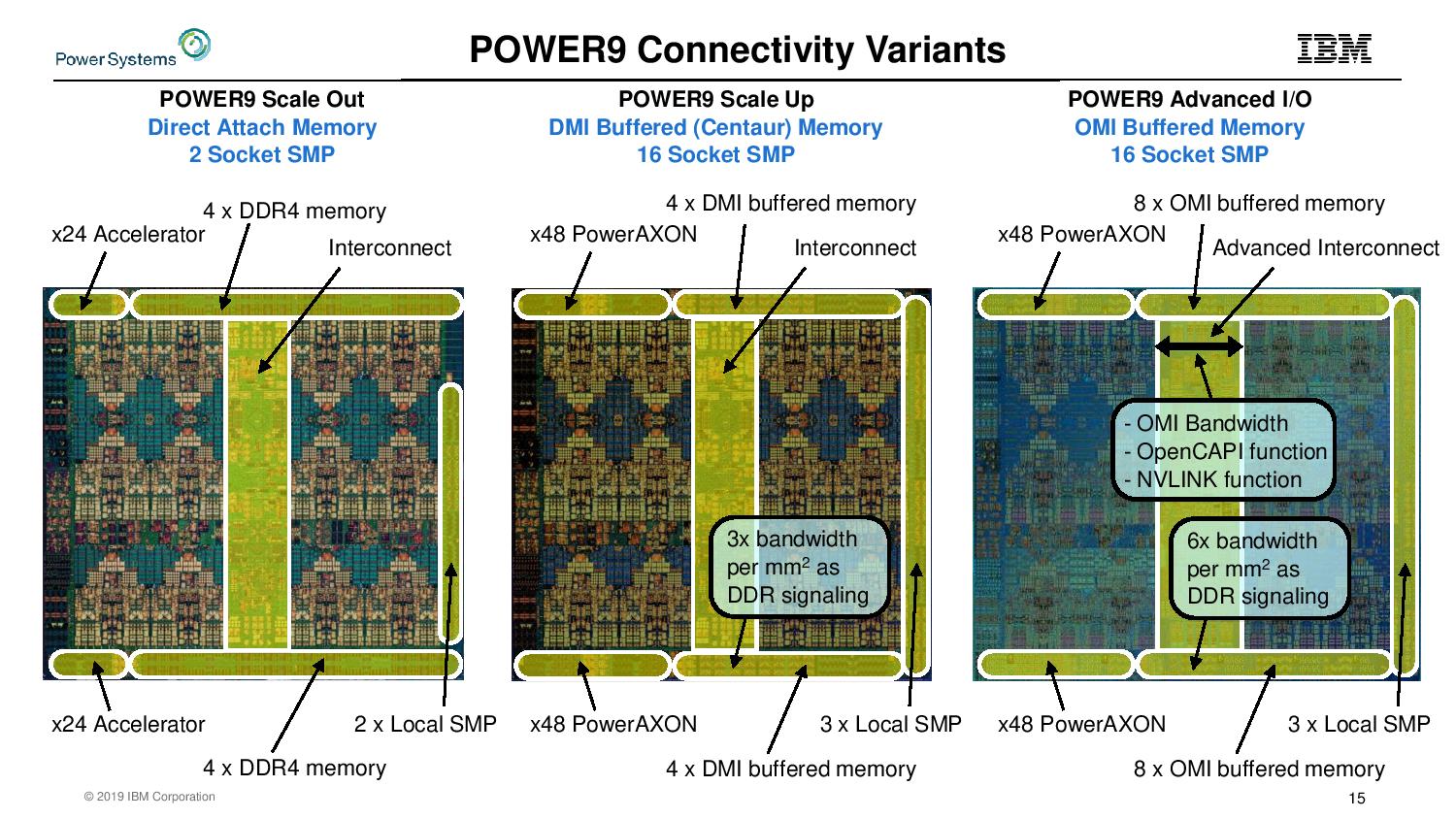

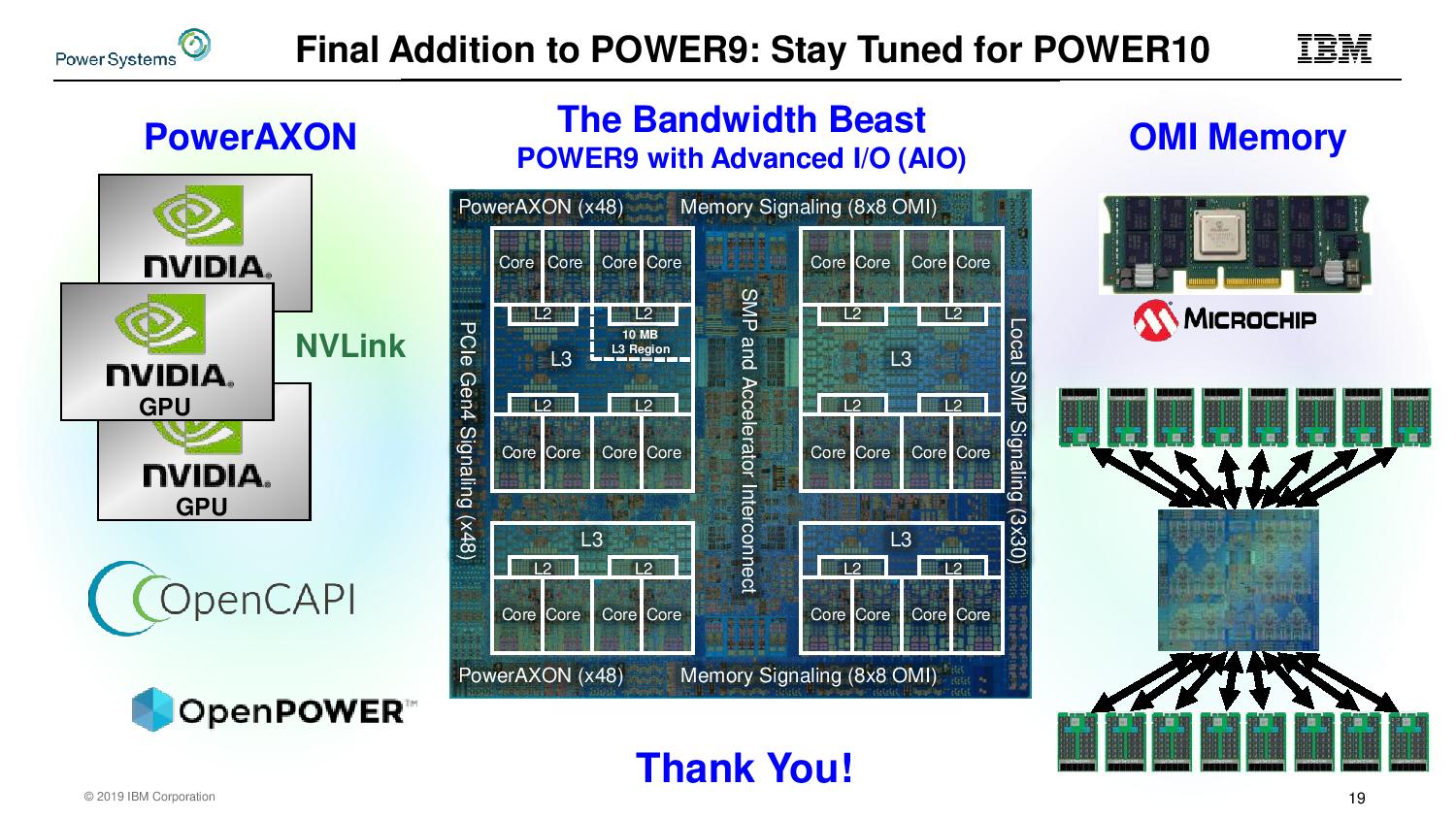

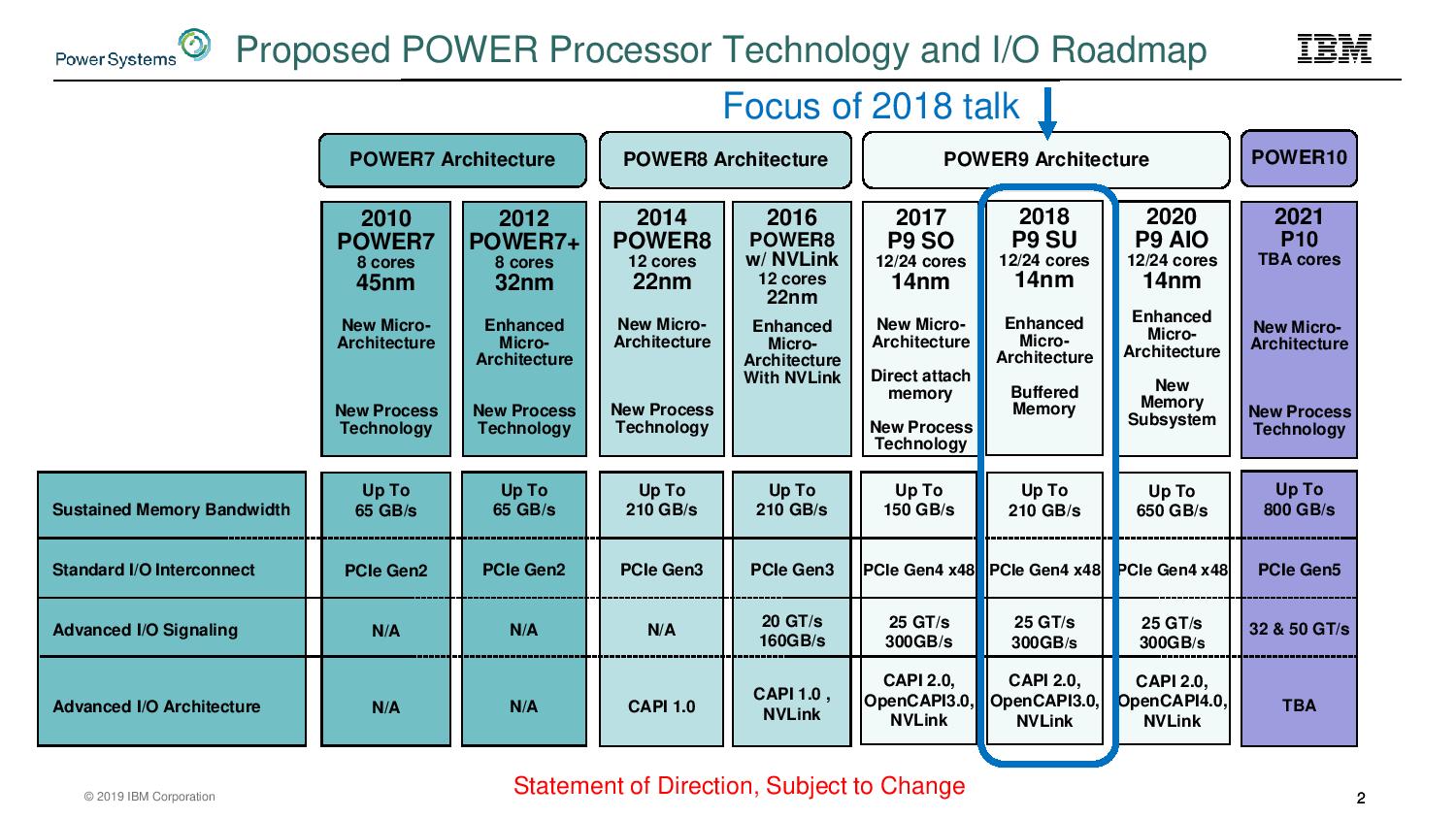

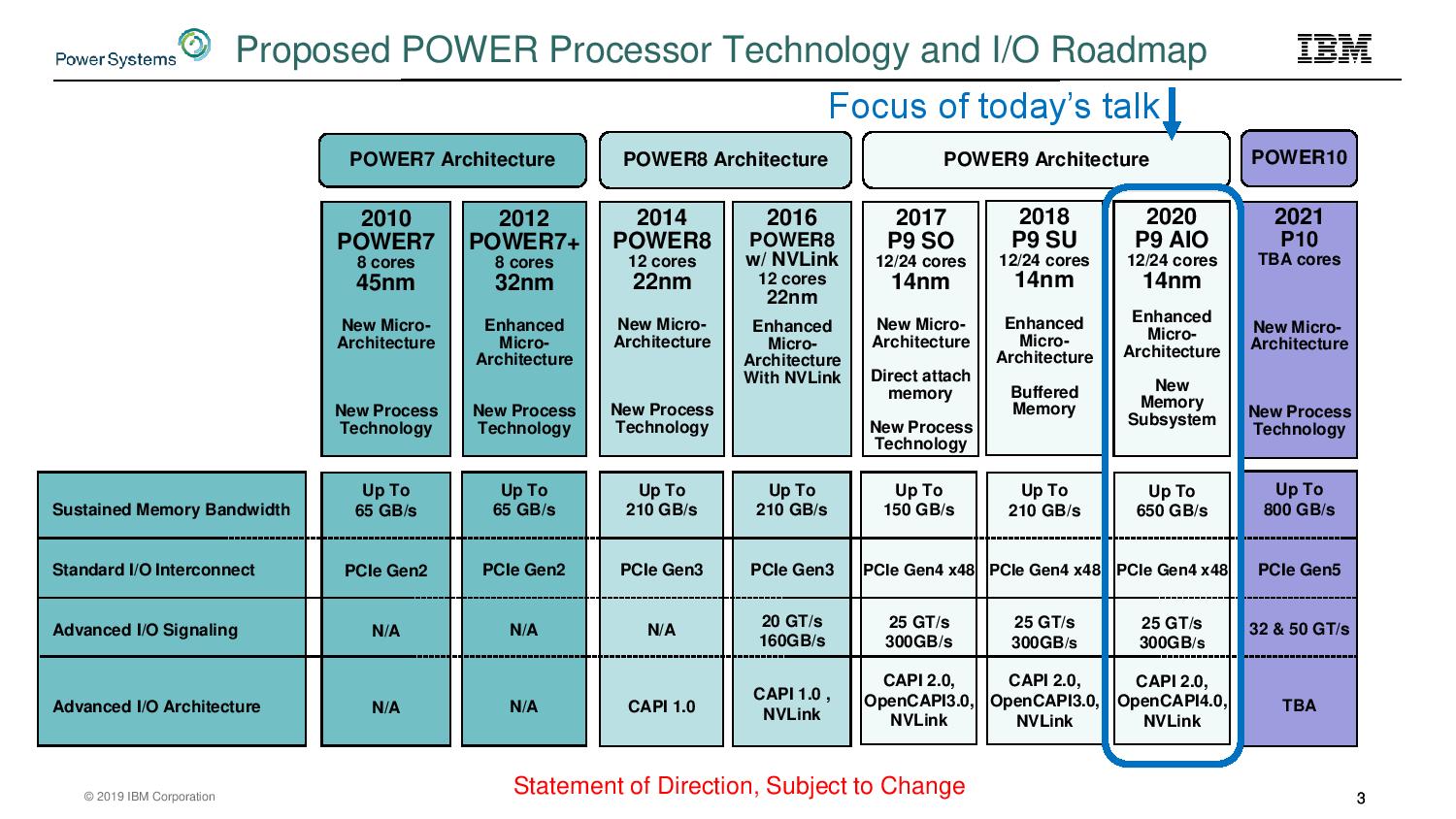

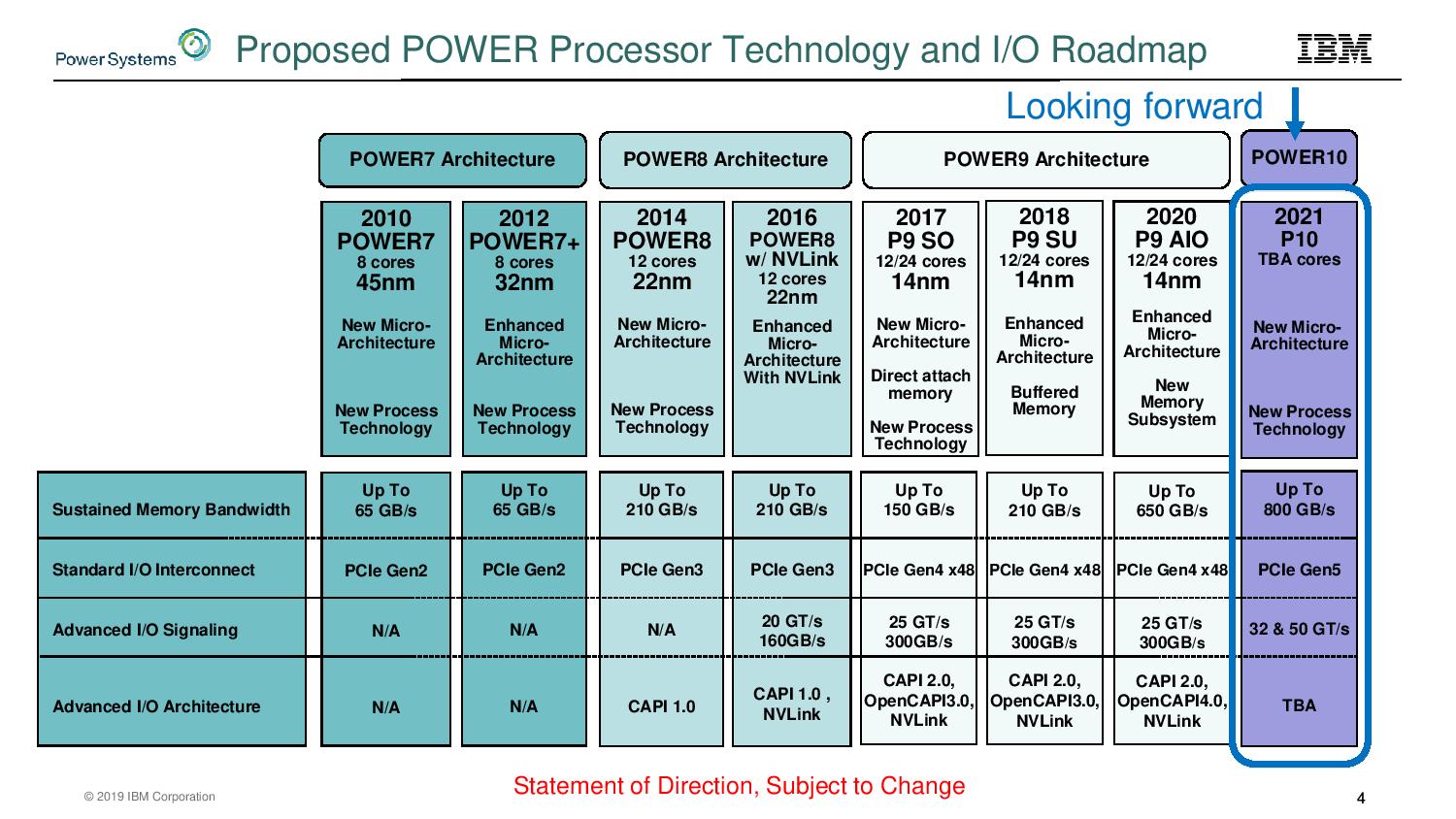

IBM creates families of processors to address different segments, with different models for tasks like scale-up, scale-out, and now NVLink deployments. Now the company is adding new custom models that use new acceleration and memory devices, and the focus of this talk. POWER10 will come with these new enhancements in 2021, along with new, but announced, core counts and process technology.

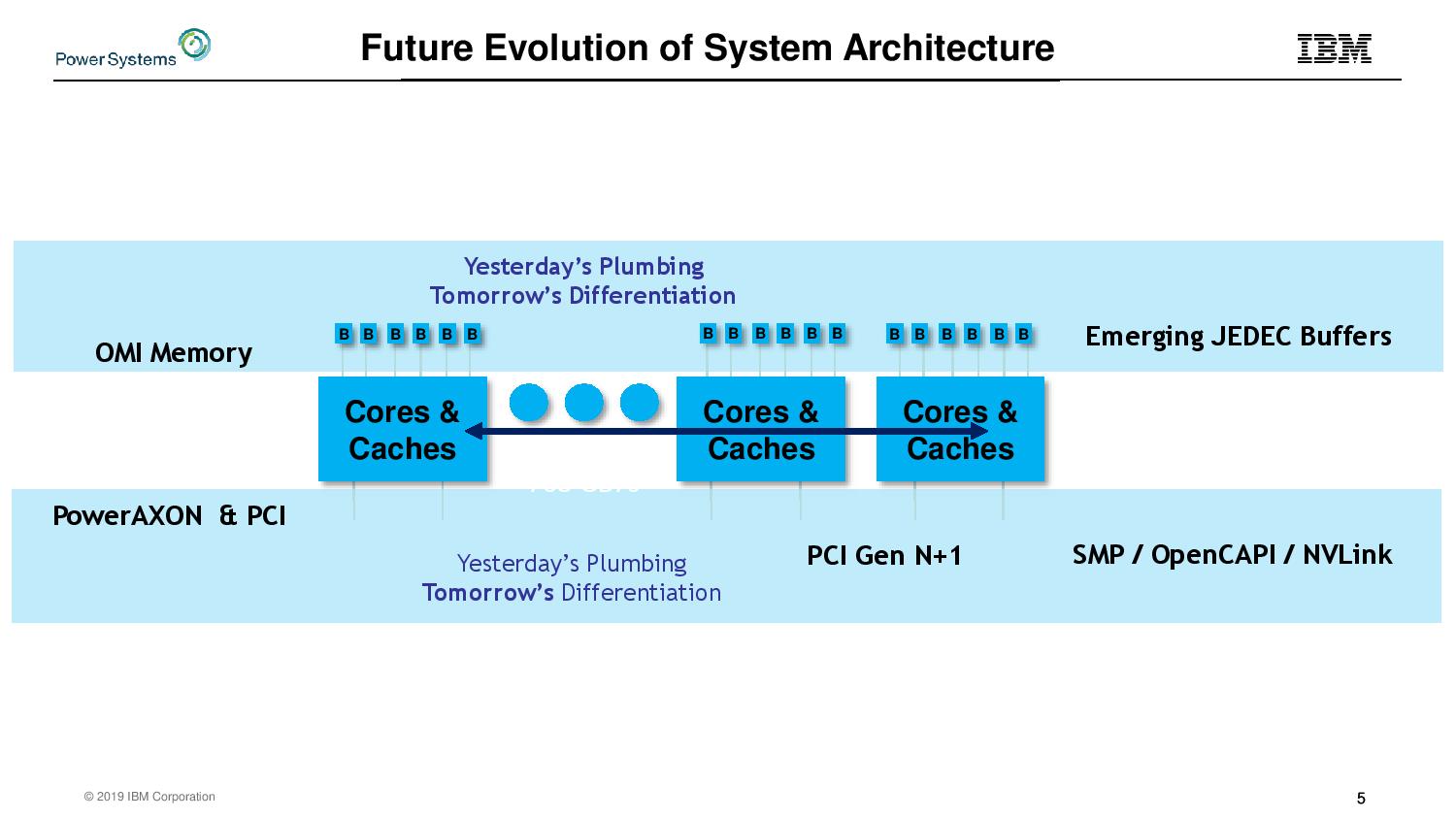

IBM focuses on developing diverse memory and accelerator solutions to differentiate its product stack with heterogeneous systems.

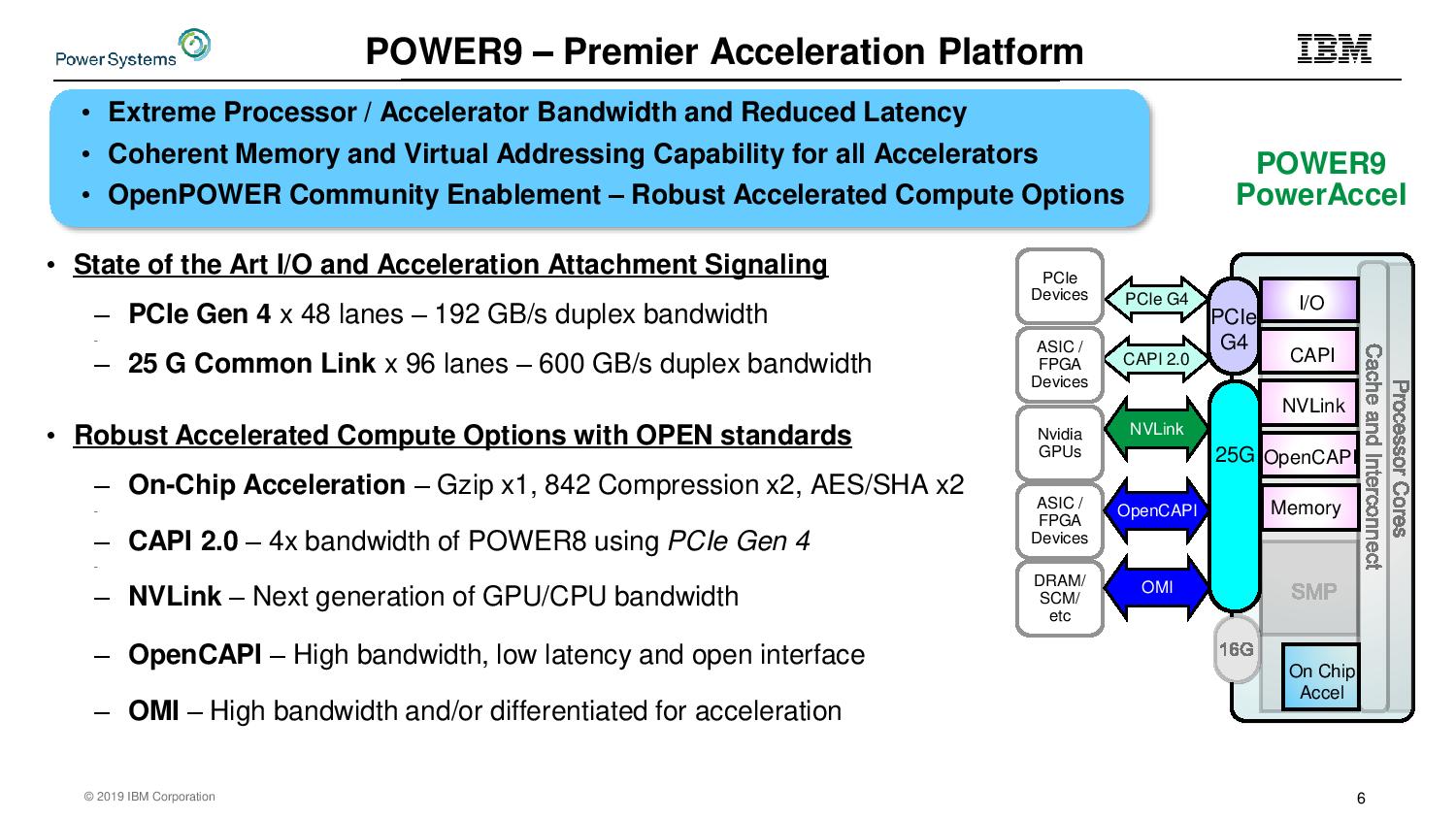

IBM aims to reduce the number of PHYs on its chips, so now it has PCIe Gen 4 PHYs while the rest of the SERDES run with the company's own interfaces. This creates a flexible interface that can support many types of accelerators and protocols, like GPUs, ASICs, CAPI, NVLink, and OpenCAPI.

IBM says this composoable system approach has yielded the world's two fastest supercomputers, albeit with the caveat that these are the two fastest in operation, while faster exascale systems are in the works.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

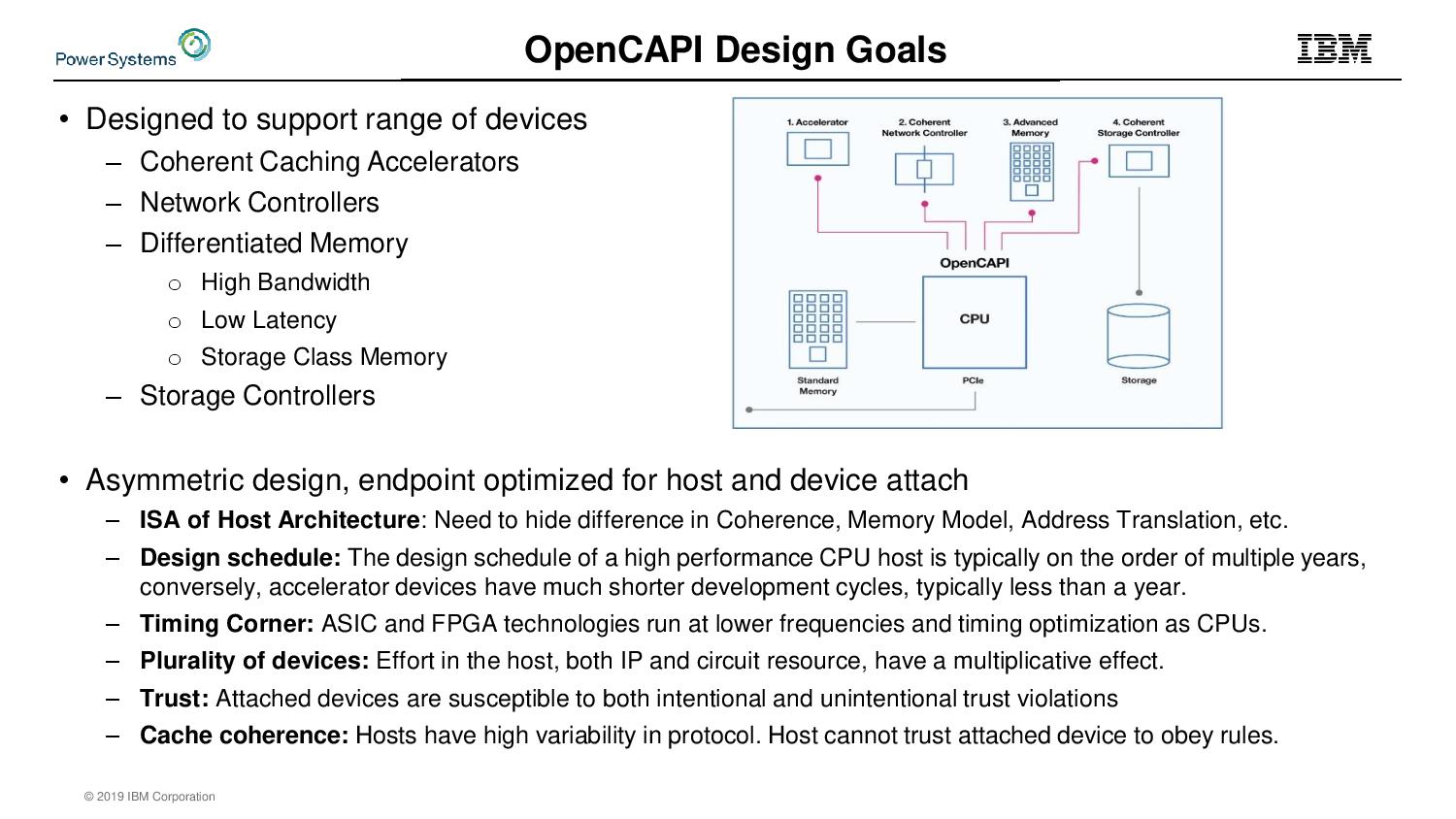

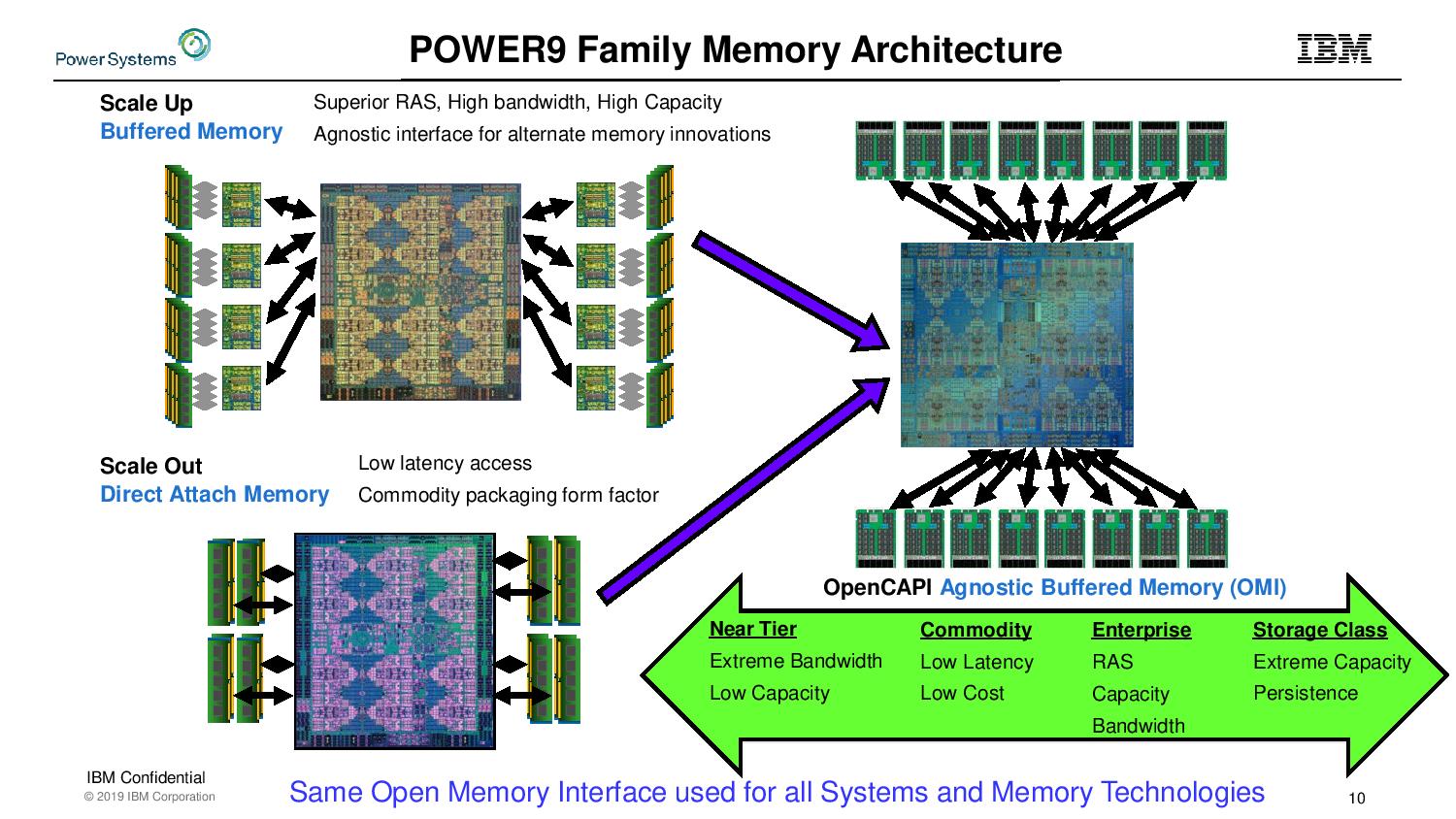

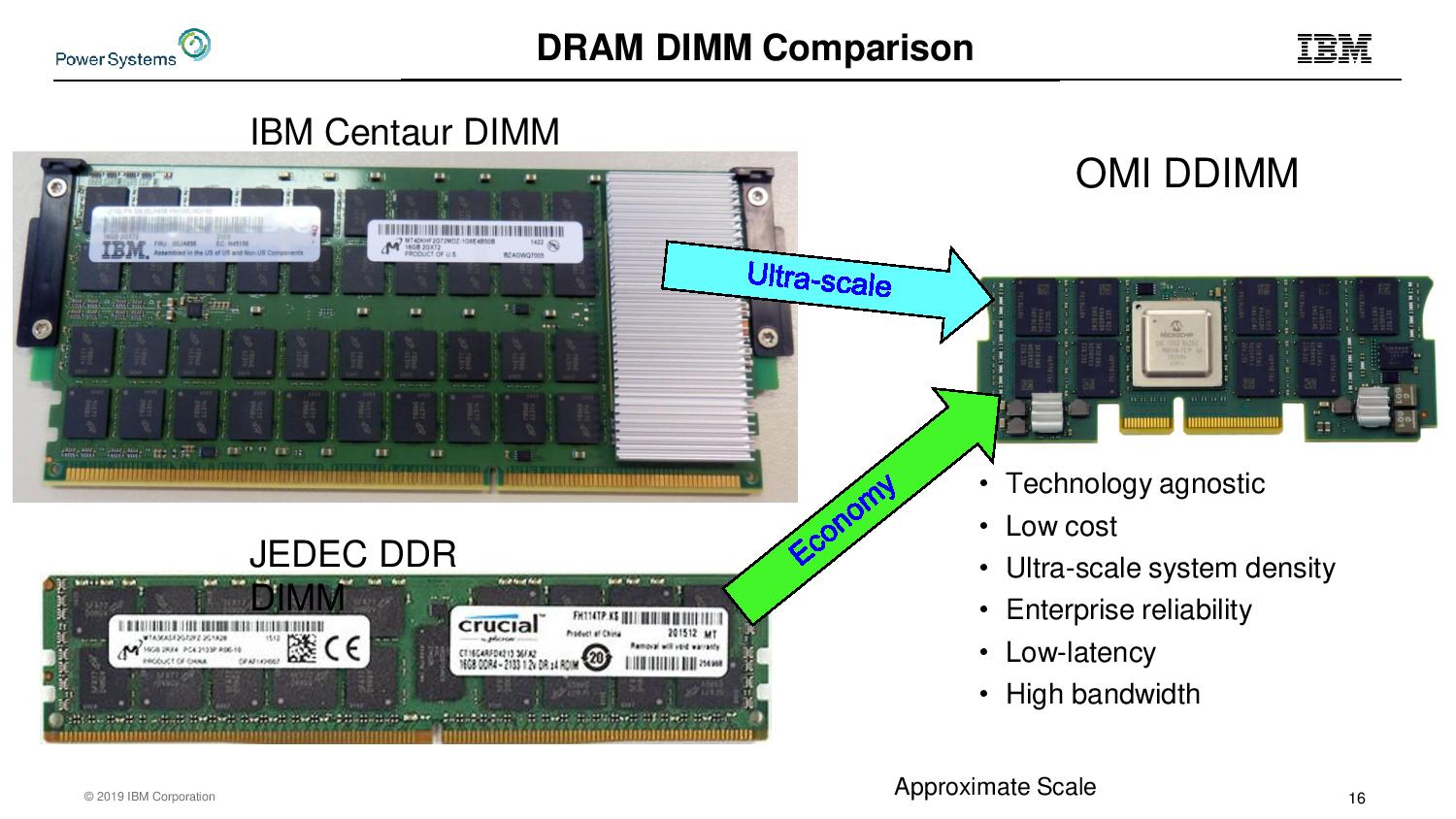

Fostering the OpenCAPI ecosystem is key to IBM's goal to open up new use-cases, like attaching traditional DRAM and persistent memory to the interface. IBM has a long history of building architectures with memory buffers, but now it has created an open memory standard.

IBM created an open standard that supports a buffered memory hierarchy.

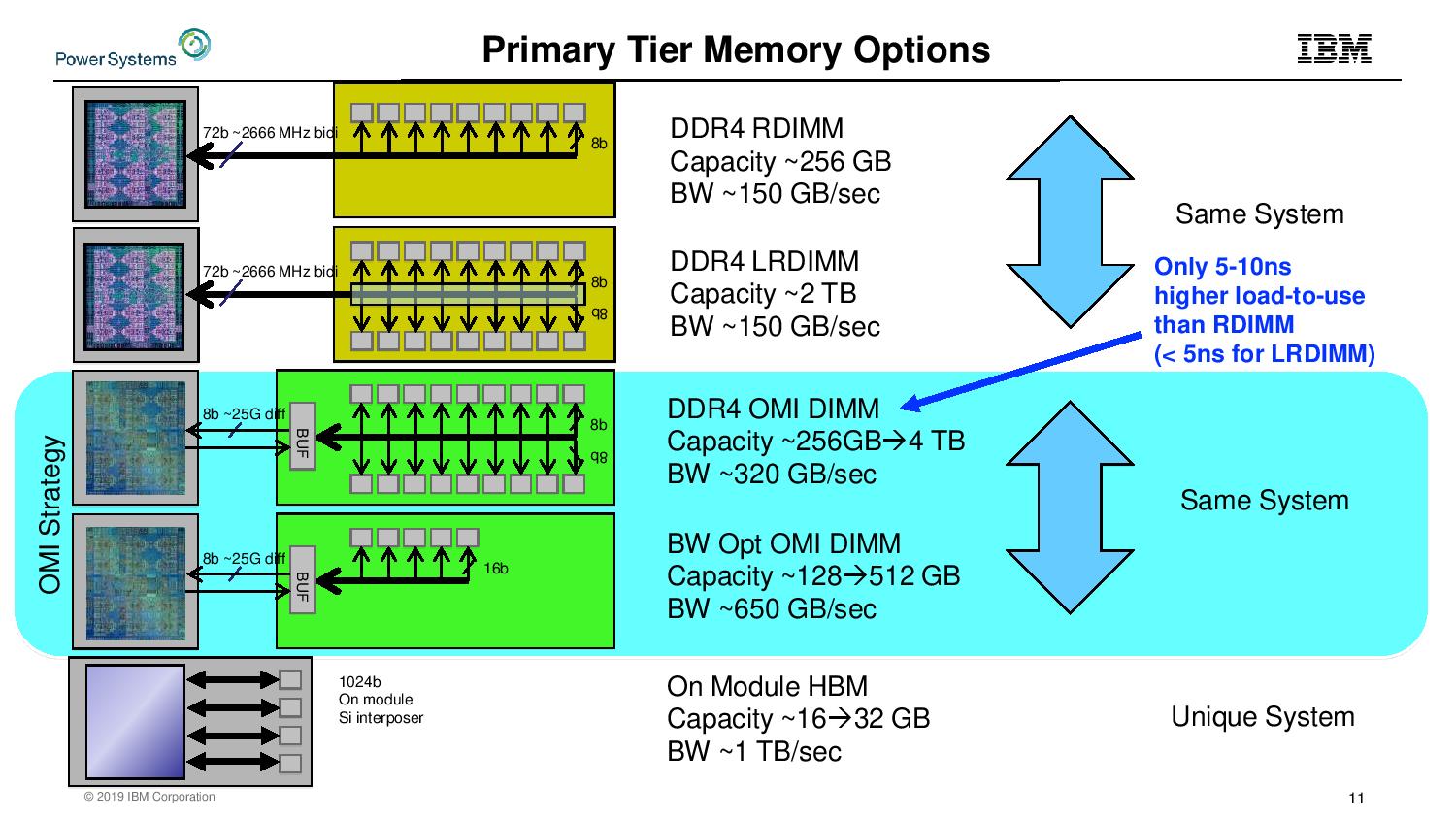

Here we can see the supported memory types.

We're having internet issues here, so this slide comes without explanation.

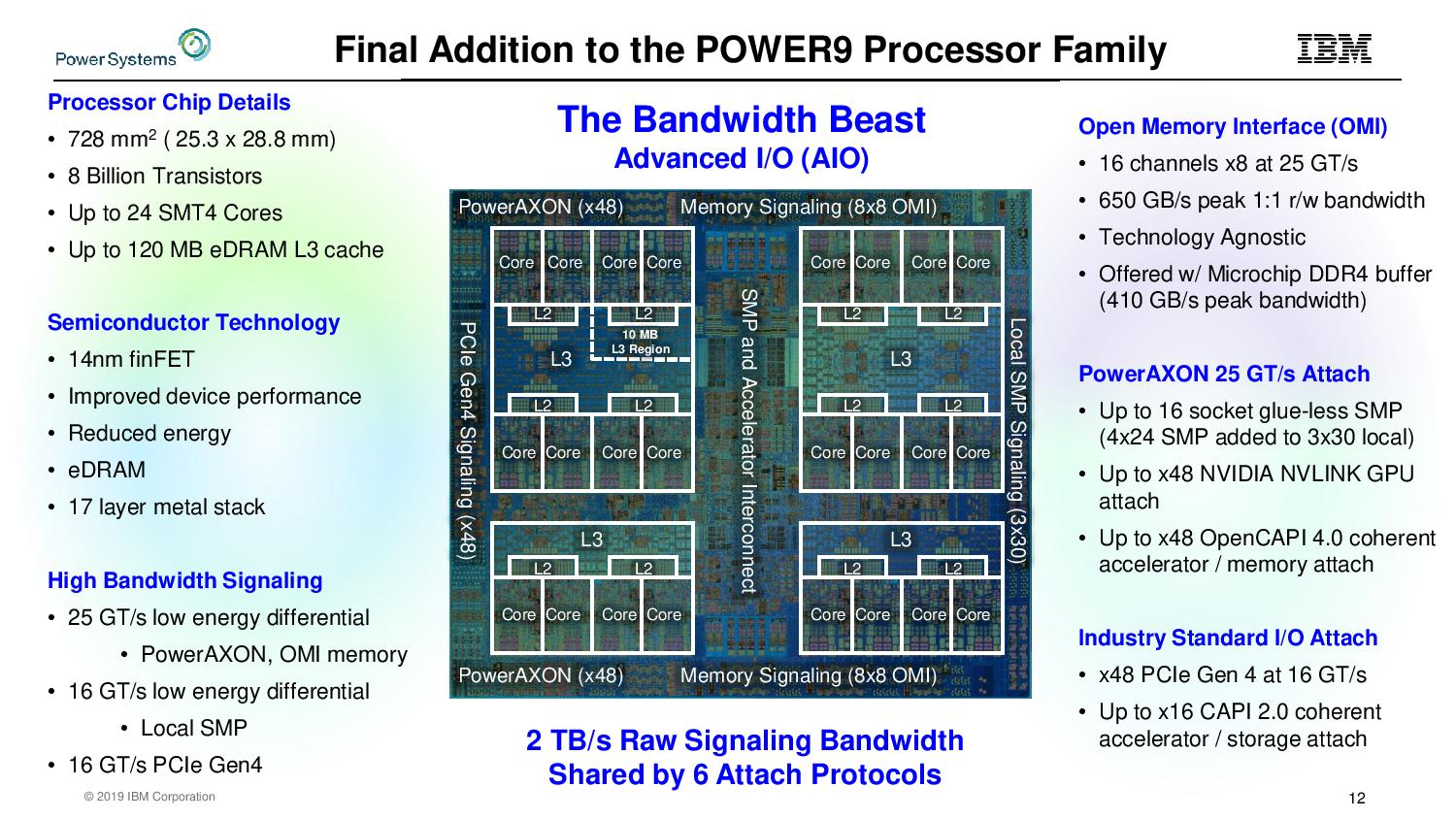

Here we can see the different die IBM uses for its different chips.

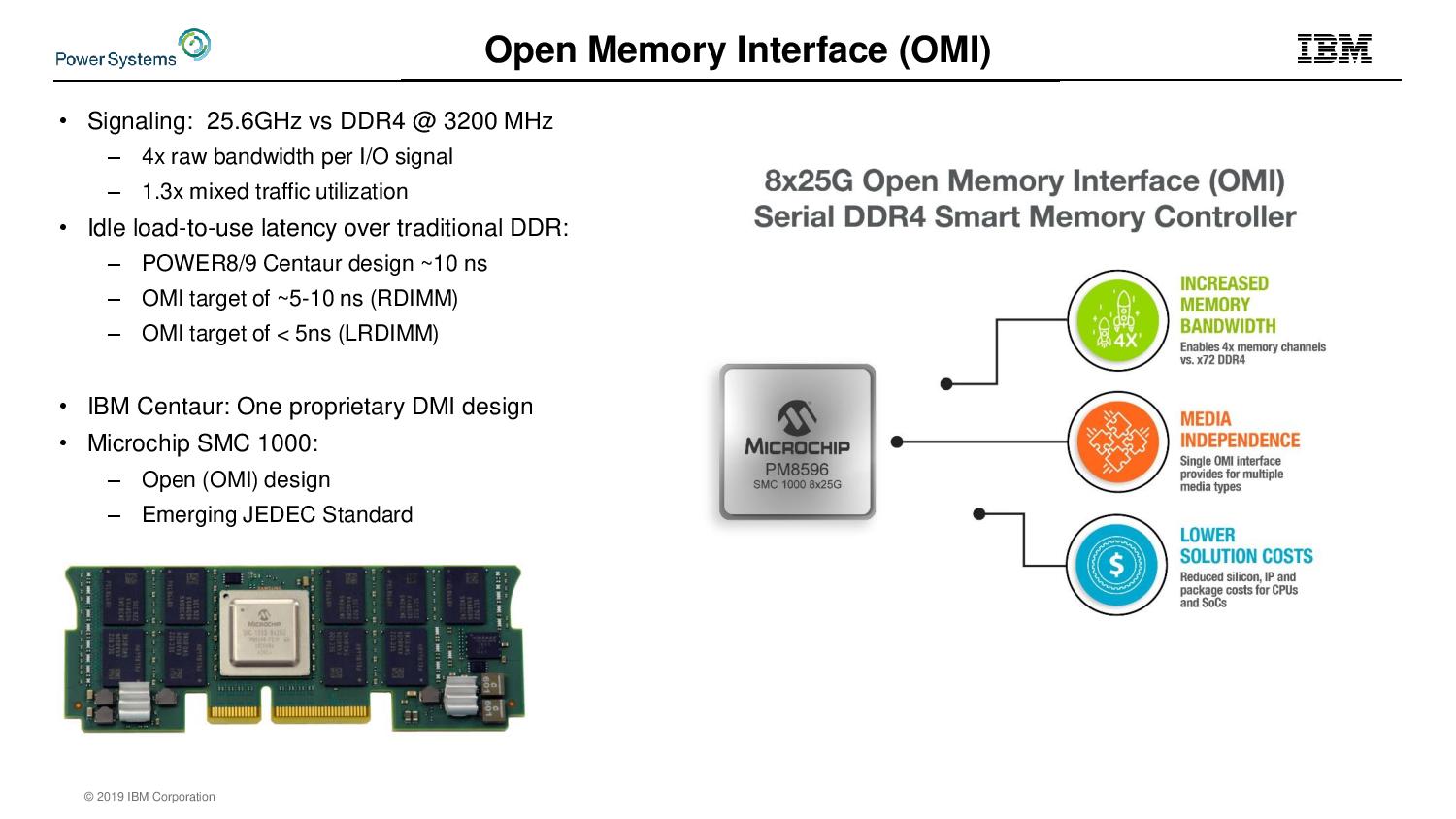

Microchip's SMC 1000 is the leading chip that connects to IBM's open memory standard.

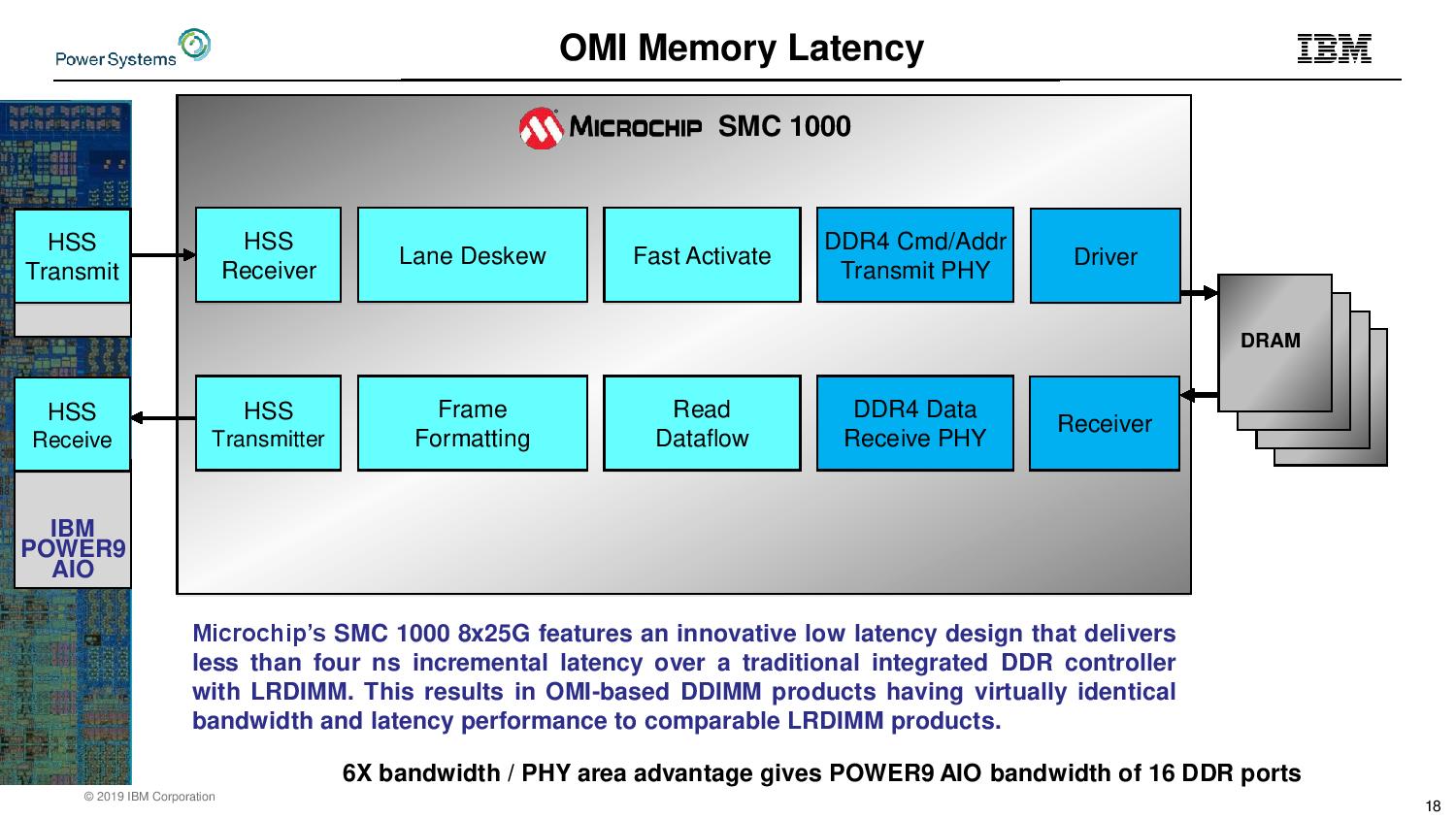

Here we can see how the chip manages the DRAM resource. In the end, these devices have similar bandwidth and response times compared to standard LRDIMMs.

IBM will incorporate this suite of new and existing technologies into its Power10 architecture, but the company didn't elaborate further. Overall the session was very informative, but a poor internet connection prevented more thorough coverage. Look to these pages soon for a follow-up piece.

Paul Alcorn is the Editor-in-Chief for Tom's Hardware US. He also writes news and reviews on CPUs, storage, and enterprise hardware.

-

bit_user Thanks for the coverage.Reply

I can't help but be disappointed that it's still 14 nm, though. Nice to see them innovating on memory interfaces and I/O.