DDR5-6400 RAM Benchmarks Show Major Performance Gains Over DDR4

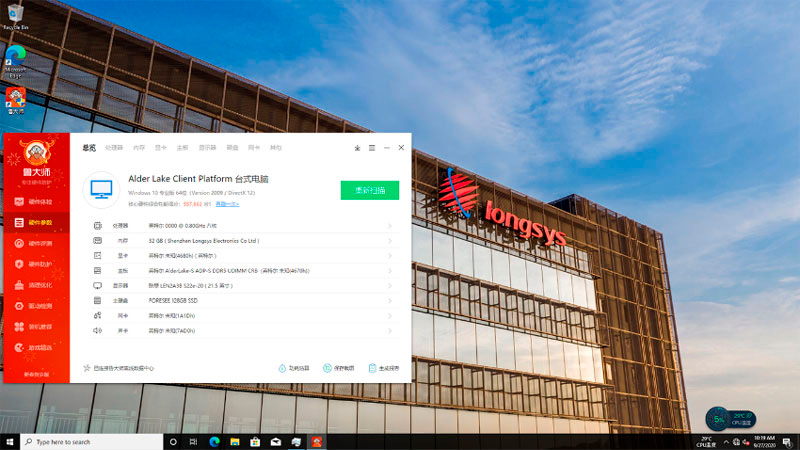

Shenzhen Longsys Electronics Co. Ltd, a Chinese NAND flash memory manufacturer, has demonstrated the power of its DDR5-6400 memory with one of Intel's Alder Lake-S processors. The company's results show that DDR5 will be an absolute delight for next-generation hardware.

Longsys currently has two DDR5-6400 memory modules in development. The 16GB variant follows a single-rank design, while the 32GB variant conforms to a dual-rank design. Both memory modules feature an eight-layer PCB, CAS Latency (CL) of 40, and a 1.1V DRAM voltage. Longsys' offerings aren't even the pinnacle of what DDR5 has to offer, though. DDR5 will eventually arrive with data rates up to DDR5-8400 and capacities that scale up to 128GB per module.

Longsys demonstrated the company's DDR5-6400 (ES1) memory module in its 32GB version with a CL40. For comparison, JEDEC's "A" specification for DDR4-6400 is rated for CL46.

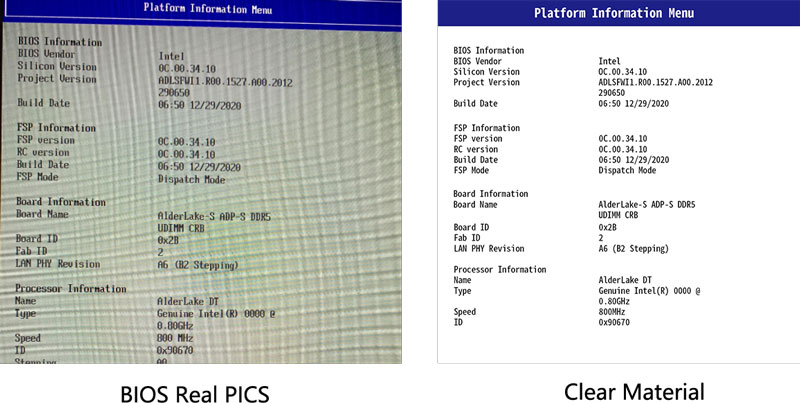

There aren't many processors that support DDR5 memory, and we haven't heard anything conclusive from the AMD camp. Alder Lake is the closest processor on the horizon that will support DDR5. In fact, Longsys' test platform is based on an Alder Lake-S chip with eight cores that operate with an 800 MHz base clock speed.

DDR5-6400 Benchmarks

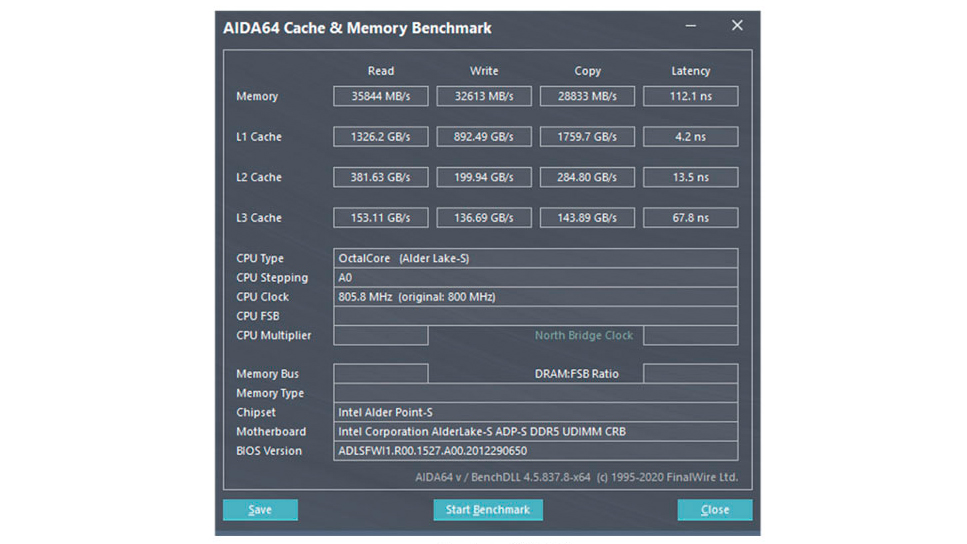

It's uncertain if Longsys compared its DDR5-6400 or DDR5-4800 memory module to one of the brand's DDR4 memory modules. The company refers to DDR5-6400 in its results, but the BIOS screenshots show DDR5-4800. The data rate of the DDR4 memory is unknown as well. But judging by the CL22 value, the DDR4 memory module most likely conforms to JEDEC's DDR4-3200 speed bin. In any event, we've reached out to Longsys for clarification.

| Header Cell - Column 0 | Longsys DDR4 32GB C22 | Longsys DDR5 32GB C40 | Difference |

|---|---|---|---|

| AIDA64 Read | 25,770 | 35,844 | 39% |

| AIDA64 Write | 23,944 | 32,613 | 36% |

| AIDA64 Copy | 25,849 | 28,833 | 12% |

| AIDA64 Latency | 56.8 | 112.1 | 97% |

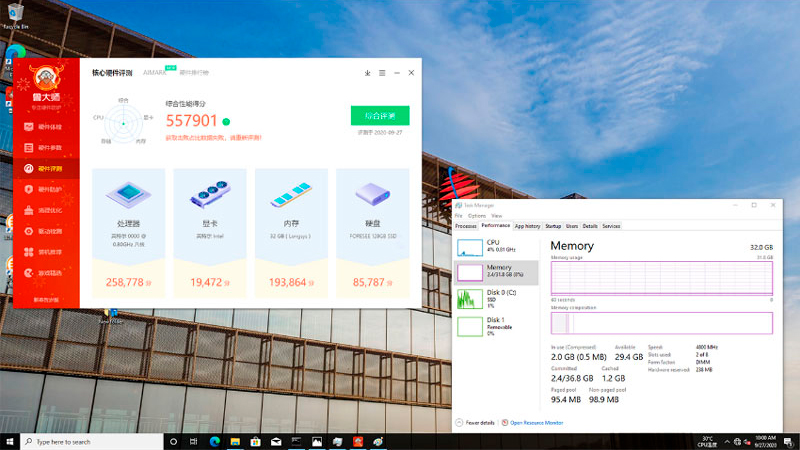

| Master Lu Benchmark | 91,575 | 193,684 | 112% |

According to Longsys' provided RAM benchmarks, the DDR5 memory module outperformed the DDR4 memory module in AIDA64's read, write and copy tests. The performance gains came down to 39%, 36%, and 12%, respectively. However, the DDR5 memory module did show a 97% higher latency than the DDR4 offering, though.

Longsys also shared the memory result for the Master Lu benchmark, which is a pretty popular benchmark in China. The DDR4 memory module scored 91,575 points, while the DDR5 memory module put up a score of 193,684 points. Synthetic benchmarks don't tell the whole story, but the DDR5 memory module delivered up to 112% better performance in Master Lu.

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Intel's 12th Generation Alder Lake-S processors may debut in late 2021 or early 2022, therefore, it shouldn't be long before consumers get a first taste of the type of performance that DDR5 can supply.

Zhiye Liu is a news editor, memory reviewer, and SSD tester at Tom’s Hardware. Although he loves everything that’s hardware, he has a soft spot for CPUs, GPUs, and RAM.

-

Makaveli Bandwidth looks great but Latency terrible which is par the course with every new memory standard. By the time i'm looking to build a DDR5 platform which won't be until maybe 2024-2025 these modules should be much better.Reply -

tharkis842 I agree, those latencies are awful, but as DDR5 matures, bandwidth should improve to a point. It'll be interesting to see how DDR5 performs going forward.Reply -

hotaru.hino If it really was DDR5-6400, then CL40 would be faster than DDR4-3200 CL22. Even if it's DDR5-4800, CL40 should only be ~20% worse.Reply

So there's either something else that's hosing up the memory module or AIDA64 doesn't quite know the best way to test the memory. -

Makaveli Replyhotaru.hino said:If it really was DDR5-6400, then CL40 would be faster than DDR4-3200 CL22. Even if it's DDR5-4800, CL40 should only be ~20% worse.

So there's either something else that's hosing up the memory module or AIDA64 doesn't quite know the best way to test the memory.

it is possible the Aida test is not optimized for DDR5 yet. -

pocketdrummer 3200 Mhz CL22 memory is bargain bin memory. I want to see how this performs against the 3600 CL16 memory that most people are buying nowadays.Reply -

logainofhades Replypocketdrummer said:3200 Mhz CL22 memory is bargain bin memory. I want to see how this performs against the 3600 CL16 memory that most people are buying nowadays.

3200 Mhz CL22 is JEDEC standard . -

TheJoker2020 Reply

One of the reasons for the extra lame latency is that DDR5 is ECC as standard.Makaveli said:Bandwidth looks great but Latency terrible which is par the course with every new memory standard. By the time i'm looking to build a DDR5 platform which won't be until maybe 2024-2025 these modules should be much better.

No doubt someone will start to produce cheaper lower latency non-ECC DDR5 RAM if it is possible to do so. We will wait and see what happens, there is plenty of time before DDR5 hits the mass market for desktops, and then we will find out the reality of DDR5 in the desktop environment rather than this super crappy info release where we really do not know what the RAM speed even was.! -

Makaveli ReplyTheJoker2020 said:One of the reasons for the extra lame latency is that DDR5 is ECC as standard.

No doubt someone will start to produce cheaper lower latency non-ECC DDR5 RAM if it is possible to do so. We will wait and see what happens, there is plenty of time before DDR5 hits the mass market for desktops, and then we will find out the reality of DDR5 in the desktop environment rather than this super crappy info release where we really do not know what the RAM speed even was.!

Some more info on DDR5

There will still be ECC memory even after launch.

From Anandtech

Ryan Smith - Tuesday, July 14, 2020 "So on-die ECC is a bit of a mixed-blessing. To answer the big question in the gallery, on-die ECC is not a replacement for DIMM-wide ECC.

On-die ECC is to improve the reliability of individual chips. Between the number of bits per chip getting quite high, and newer nodes getting successively harder to develop, the odds of a single-bit error is getting uncomfortably high. So on-die ECC is meant to counter that, by transparently dealing with single-bit errors.

It's similar in concept to error correction on SSDs (NAND): the error rate is high enough that a modern TLC SSD without error correction would be unusable without it. Otherwise if your chips had to be perfect, these ultra-fine processes would never yield well enough to be usable.

Consequently, DIMM-wide ECC will still be a thing. Which is why in the JEDEC diagram it shows an LRDIMM with 20 memory packages. That's 10 chips (2 ranks) per channel, with 5 chips per rank. The 5th chip is to provide ECC. Since the channel is narrower, you now need an extra memory chip for every 4 chips rather than every 8 like DDR4."

https://www.anandtech.com/show/15912/ddr5-specification-released-setting-the-stage-for-ddr56400-and-beyond