AMD Phenom II X4: 45nm Benchmarked

Technical Details

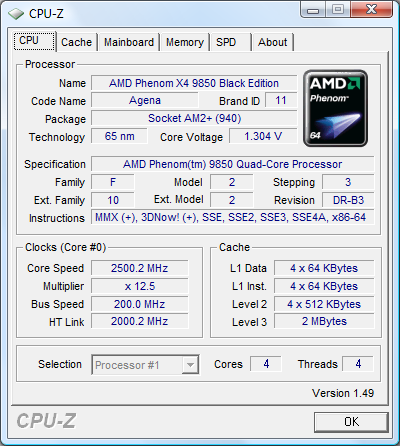

In switching its production processes over from 65 nm to 45 nm, AMD was able to increase the transistor count in the chip core markedly, while reducing the surface area of the die from 285 mm2 down to 258mm2. Its overall device count went from roughly 450 million to 758 million.

Beyond simply shrinking the transistors in its Phenom II core, AMD made some notable silicon enhancements that, individually might not be game-changers, but cumulatively enable some of the performance and efficiency increases we'll be exploring further in this story. Most obvious is the 45 nm immersion lithography that minimizes current leakage. The L3 cache, which is up to 6 MB from 2 MB, is also two cycles faster than the previous generation's L3.

In light of AMD's Cool'n'Quiet 3.0 enhancements, which introduce extra power states and slash idle power (more on that shortly), each core's L1 and L2 caches now flush into the shared L3 after the core enters a halt state, allowing lower speeds. Our sample quickly scaled down to 800 MHz during periods of inactivity.

Finally, improved brach prediction, bigger buffers, and optimizations to the way certain instructions execute also give Phenom II significant advantages over the older Phenom.

| CPU Model | Athlon X2 | Phenom | Phenom II |

|---|---|---|---|

| Dimensions | 230 mm2 | 285 mm2 | 258 mm2 |

| Transistor Count | 227 M | 450 M | 758 |

The following table compares technical details of processors from both AMD and Intel:

| Header Cell - Column 0 | AMD Phenom | AMD Phenom II | Intel Core i7 | Intel Core 2 |

|---|---|---|---|---|

| Core | Agena / Toliman | Deneb | Bloomfield | Yorkfield / Wolfdale / Kentsfield / Conroe / Allendale |

| Manufacturing Process | 65 nm | 45 nm | 45 nm | 65 nm, 45 nm |

| Top Clock Speed | 2.6 GHz | 3.0 GHz | 3.2 GHz | 3.2 GHz |

| L1 Cache | 64 + 64 KB | 64 + 64 KB | 32 + 32 KB | 32 + 32 KB |

| L2 Cache | 512 KB | 512 KB | 256 KB | 4 MB |

| L3 Cache | 2 MB | 6 MB | 8 MB | N/A |

| Max Power (TDP) | 140 W | 125 W | 136 W | 136 W |

| CPU <-> Northbridge | HyperTransport | HyperTransport | Quick Path Interconnect | Front Side Bus |

| CPU <-> CPU | HyperTransport | HyperTransport | Quick Path Interconnect | Northbridge Internal |

| Max Clock | 3.2 GHz (25.6 GB/s) | 3.2 GHz (25.6 GB/s) | 6.4 GT/s (12.8 GB/s) | 400 MHz (12.8 GB/s) |

| Min Clock | 800 MHz (6.4 GB/s) | 800 MHz (6.4 GB/s) | 4.8 GT/s (9.0 GB/s) | 200 MHz (6.4 GB/s) |

| Reference Clock | 200 MHz | 200 MHz | 133 MHz | 400 MHz, 333 MHz, 266 MHz, 200 MHz |

| 64-bit Support | x86-64 | x86-64 | EM64T | EM64T |

| Hyper-Threading | N/A | N/A | Yes | N/A |

| Multimedia Extensions | MMX 3DNow! SSE SSE2 SSE3 SSE 4a | MMX 3DNow! SSE SSE2 SSE3 SSE 4a | MMX SSE SSE2 SSE3 SSSE3 SSE4.1 SSE 4.2 | MMX SSE SSE2 SSE3 SSSE3 SSE4.1 |

| Virtualization | Pacifica | Pacifica | VT | VT |

| Energy Saving | Cool’n’Quiet | Cool’n’Quiet 3.0 | Enchanced Halt State (C1E), SpeedStep | Enchanced Halt State (C1E), SpeedStep |

| Thermal Protection | Thermal Diode | Thermal Diode | Thermal Monitor 2 | Thermal Monitor 2 |

| Virus Protection | XD bit | XD bit | XD bit | XD bit |

| Trusted Execution | Presidio | Presidio | LaGrande Technology | LaGrande Technology |

| Active Management | No | No | iAMT2 (V-Pro) | iAMT2 (V-Pro) |

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Current page: Technical Details

Prev Page The Phenom II And AMD's Dragon Platform Next Page Performance-Enhancing Changes-

firedogevan why focus on the q6600... wouldn't the q9550 or 9650 be a more accurate comparison given their respective locations in the product lineup?Reply -

dechy Yeah, the price comparison table should of included a Q9550, which costs same as i7 920 but with the lower mobo/ram combo price.Reply

Ends up being the same price as the AMD bundle, but with a good more performance... there goes the whole "AMD price/performance" aspect of this chip. -

one-shot Great review. Maybe some overclocking later? There were some pretty high claims about its overclocking potential. I'll wait for AM3 before I retire my E6750.Reply -

The Q9xxx series would trump the PhenomII in all the categories listed above. THG, it was downright *criminal* to have not included the Yorkfield chips in your performance per dollar and performance per watt analysis.Reply

-

nashville hey bert/tom's:Reply

good write up: thought id comment on i7 watts:

"we measured the power consumption directly from the 12 volt rail that supplied the CPU", i read somewhere the only i7 core logic gets power from 12v rail, the uncore/cache part somewhere else. if this is true, you going to do another measurements? -

kirvinb I'm so happy to see Intel has some competetion. While these new processors are not mind blowing, they offer some decent performance at the price given. I am sure this will lower the price of the q9400 and q9550, which is exactly what I want to see. Maybe even the i7s price will lower and maybe we will be back in the good days..where intel and amd flipped sides of the powerhouse like every 6 months..!! Good Write Up..Reply -

jj463rd On the forums someone mentioned "why did they use DDR2-800 RAM when DDR2-1066 would give better performance for the Phenom II".Wouldn't this skew the benchmarks by a little bit (perhaps 2 to 3%)?Reply