ASML explores Hyper-NA chipmaking tools as the next step in shrinking transistors — tools would debut in 2030, but significant technology and cost hurdles remain

The world needs more shrinking, and Hyper-NA could help.

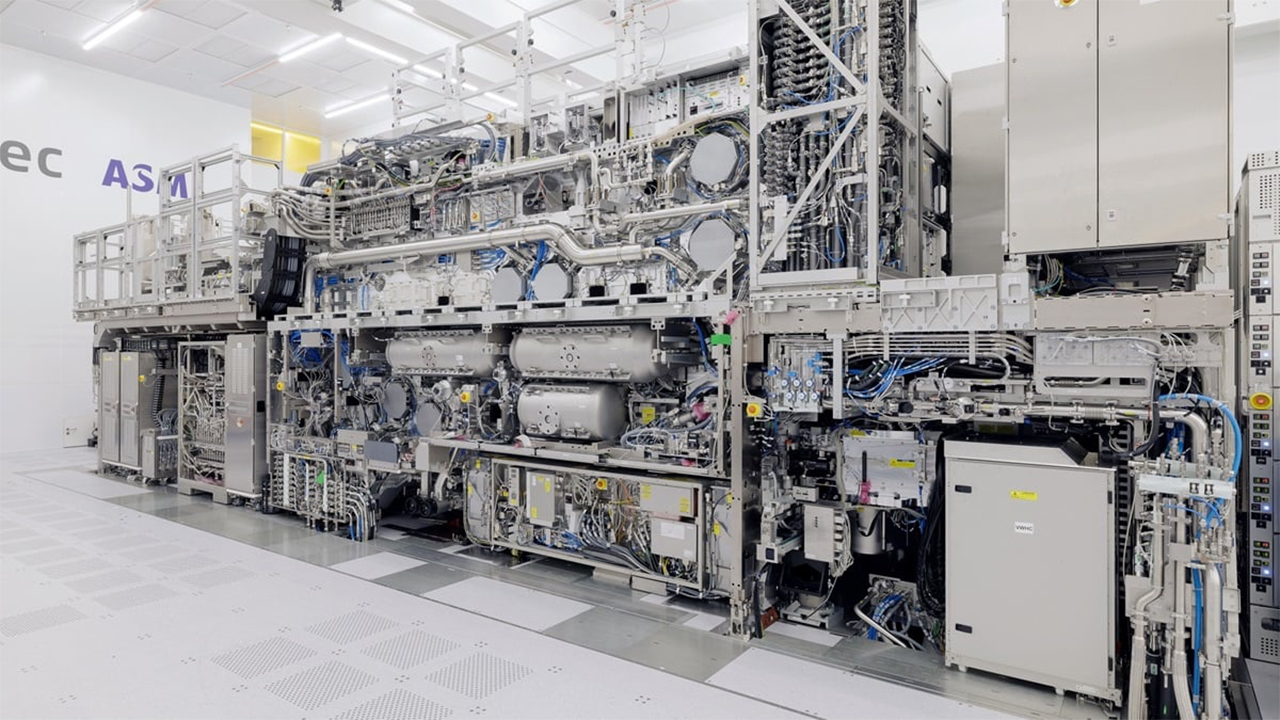

Shrinking transistor dimensions is critical for continued scaling of chip performance, so the semiconductor industry is working on various ways to make transistors smaller. In the coming years, chipmakers are set to adopt ASML's latest high-NA extreme ultraviolet (EUV) lithography tools, which will be particularly useful for post-3nm-class fabrication nodes. But what's next? ASML says that Hyper-NA is currently being explored for as-yet-undefined new tools that would arrive in the 2030s to power future generations of chips.

"Hyper-NA with an NA higher than 0.7 is certainly an opportunity that will become more visible from around 2030," wrote Martin van den Brink, chief technology officer of ASML, in ASML's 2023 Annual Report (via Bits & Chips). "It is likely to be most relevant for Logic — and it will need to be more affordable than [High-NA EUV] double patterning — but it may also be an opportunity for DRAM. For us, the key thing is that Hyper-NA is driving our overall EUV capability platform to improve both cost and lead time."

ASML's current crop of EUV tools consists of Low-NA models, which feature 0.33 NA optics and can achieve a critical dimension (CD) of 13.5 nm. That's sufficient to produce a minimum metal pitch of 26 nm and an approximate interconnect space pitch of 25–30nm tip-to-tip with a single exposure patterning. These dimensions are good enough for 4nm/5nm-class production nodes. Still, the industry will need 21-24nm pitches for 3nm, which is why TSMC's N3B process technology is designed to use Low-NA EUV double patterning to print the smallest possible pitches. This approach is considered very expensive.

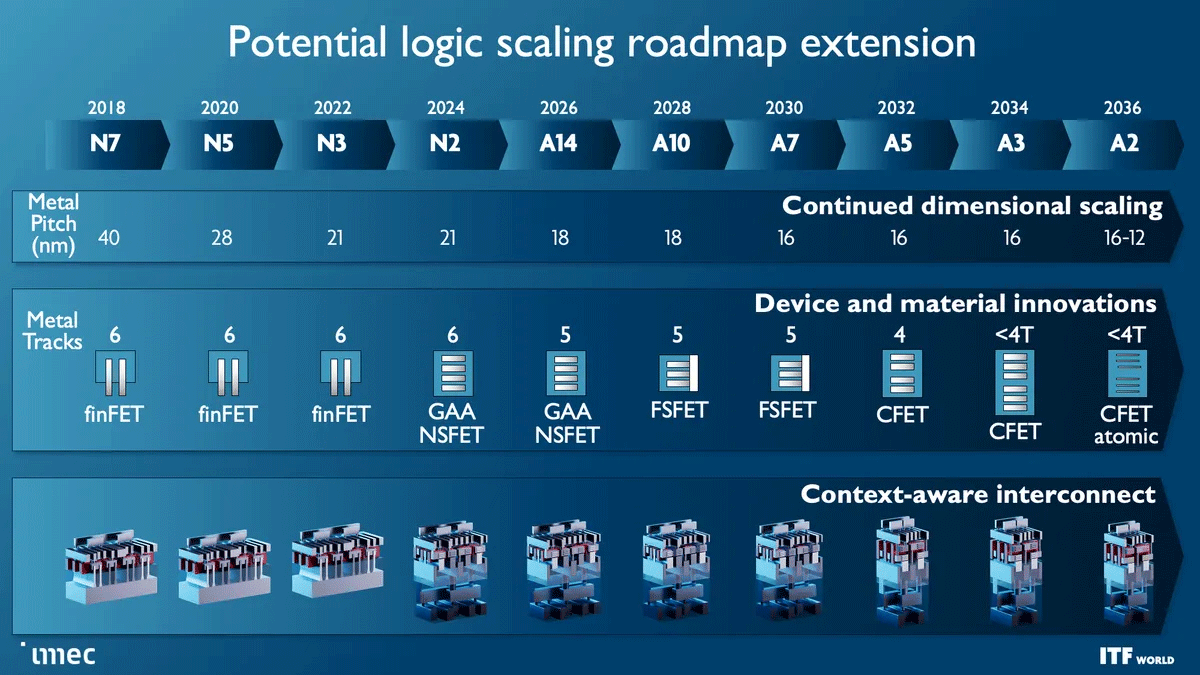

Next-gen High-NA EUV systems with 0.55 NA optics will achieve a CD of 8nm, which will be enough to print a minimum metal pitch of around 16nm, which will be useful for nodes beyond 3nm and is expected to be good enough even for 1nm, at least according to figures envisioned by Imec.

But metal pitches will get even smaller beyond 1nm, so the industry will need more sophisticated tools than ASML's High-NA devices. This leads us to Hyper-NA tools with even higher numerical aperture projection optics. ASML's CTO, Martin van den Brink, confirmed in an interview with Bits & Chips that the viability of Hyper-NA technology is being investigated. Still, no final decision has been made yet.

Increasing the numerical aperture of projection optics is a costly process involving significant changes to the design of the lithography tools. In particular, this includes the machine's physical dimensions, the need to develop many new components, and the impact of increased costs. A Low-NA EUV Twinscan NXE machine costs $183 million or higher depending on configuration, and a High-NA EUV Twinscan EXE tool will be priced at $380 million or higher depending on configuration, ASML recently disclosed. Hyper-NA would cost more than that, so ASML has to answer two questions: whether it can be done technologically and whether it will be economically viable for the leading logic chipmakers.

Only three leading-edge chipmakers are left: Intel, Samsung Foundry, and TSMC. Japan-based Rapidus has yet to develop into a feasible competitor. So, while Hyper-NA EUV lithography is needed, it has to be reasonably affordable.

"The introduction of Hyper-NA will be determined by the extent to which we can reduce costs," Martin van den Brink told Tweakers.net last year. "I have traveled around the world several times and have spoken with customers about the necessity and desirability of Hyper-NA. In recent months, I have gained the confidence and insight that customers want to drive the resolution down so much further, that the possibility for the use of Hyper-NA for mass production of logic and memory chips is there. That would be around the next decade change. But it depends on the costs."

Get Tom's Hardware's best news and in-depth reviews, straight to your inbox.

Anton Shilov is a contributing writer at Tom’s Hardware. Over the past couple of decades, he has covered everything from CPUs and GPUs to supercomputers and from modern process technologies and latest fab tools to high-tech industry trends.

-

yeyibi In the past, there were so many foundries, that when one got stuck, being unable to advance, some other foundry developed a new idea, and beat them, accelerating the advance of the technology.Reply

Today the number of foundries is so small and expensive, that new ideas that think out the box got so rare that progress has been stopped. Patents accumulate unused, unable to attract new investors. -

bit_user Reply

You don't just need multiple competitive foundries, but also competitive equipment suppliers. This article is really about ASML being in the driver's seat about whether to go ahead with hyper-NA. We shouldn't consider it a good thing that a single company is relied upon to make such decisions for an entire industry.yeyibi said:In the past, there were so many foundries, that when one got stuck, being unable to advance, some other foundry developed a new idea, and beat them, accelerating the advance of the technology.

I'm not too concerned about willingness to try new ideas. The fabs roll out different developments in slightly different orders and timelines, also with their own twists on the approach. For instance, TSMC was first to embrace EUV, Samsung was first to utilize GAA, and Intel was first to deploy backside PDN. I think, if there were good ideas that are feasible, they wouldn't be ignored. This business is so incredibly high-stakes that you really can't afford to leave any stone unturned.yeyibi said:Today the number of foundries is so small and expensive, that new ideas that think out the box got so rare that progress has been stopped. Patents accumulate unused, unable to attract new investors.

Probably the main reason fabs are following similar roadmaps is that IMEC does so much work in analyzing different ideas and assessing their merits and the roughly optimal order to deploy them. Of course, having a common equipment supplier is surely another big factor. -

yeyibi Reply

The story of computer hardware is full of cases where the engineers didn't got support for their ideas, so they left the company, started their own, and made a revolution.bit_user said:I'm not too concerned about willingness to try new ideas. The fabs roll out different developments in slightly different orders and timelines, also with their own twists on the approach. For instance, TSMC was first to embrace EUV, Samsung was first to utilize GAA, and Intel was first to deploy backside PDN. I think, if there were good ideas that are feasible, they wouldn't be ignored. This business is so incredibly high-stakes that you really can't afford to leave any stone unturned.

For example Cray left his company to build his own supercomputers, and his ideas are today in all consumer processors.

Many of them failed, but the ones who succeeded changed the industry.

That's no possible today, because to be relevant is necessary to have billions in new investment. -

bit_user Reply

I think this doesn't really apply so much to a field as well-studied as lithography. Yes, there are some approaches that are fundamentally different, like Canon's, but it takes many $Billions of investment, to get an idea like that off the ground. By the time they have it working, lithography will already have surpassed it, making it unclear where the additional investment would come from to try and keep it going.yeyibi said:The story of computer hardware is full of cases where the engineers didn't got support for their ideas, so they left the company, started their own, and made a revolution.

If we restrict ourselves to the set of incremental changes that fabs can implement, I believe there aren't really untapped opportunities. Too many really smart people are working on this field, in at least 3 different companies.

That was more than 50 years ago, when the industry was in its infancy. He left not because they rejected his ideas (some of which indeed made it into several CDC machines), but because he wanted to chase a different market than his employer. So, it was a business-level disagreement, rather than technical.yeyibi said:For example Cray left his company to build his own supercomputers, and his ideas are today in all consumer processors.